# **Stepper Motor Drive Circuit**

#### **FEATURES**

- Complete Motor Driver and Encoder

- Continuous Drive Capability 350mA per Phase

- Contains all Required Logic for Full and Half Stepping

- Bilevel Operation for Fast Step Rates

- Operates as a Voltage Doubler

- Useable as a Phase Generator and/or as a Driver

- Power-On Reset Guarantees Safe, Predictable Power-Up

#### DESCRIPTION

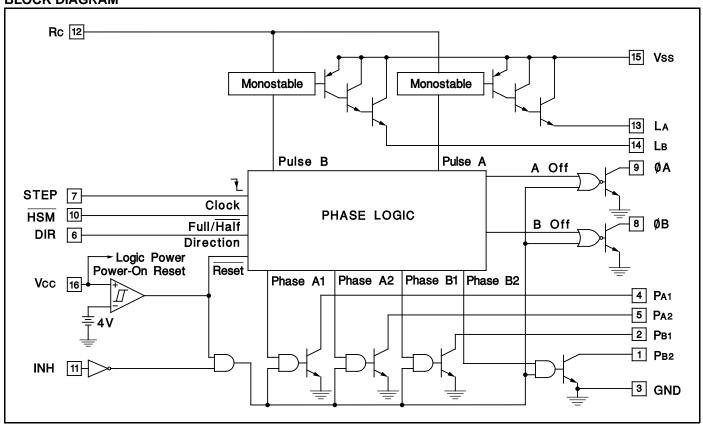

The UC3517 contains four NPN drivers that operate in two-phase fashion for full-step and half-step motor control. The UC3517 also contains two emitter followers, two monostables, phase decoder logic, power-on reset, and low-voltage protection, making it a versatile system for driving small stepper motors or for controlling large power devices.

The emitter followers and monostables in the UC3517 are configured to apply higher-voltage pulses to the motor at each step command. This drive technique, called "Bilevel," allows faster stepping than common resistive current limiting, yet generates less electrical noise than chopping techniques.

## **ABSOLUTE MAXIMUM RATINGS**

| Second Level Supply, Vss             | JV |

|--------------------------------------|----|

| Phase Output Supply, VMM 40          | VC |

| Logic Supply, Vcc                    | 7V |

| Logic Input Voltage                  | 7V |

| Logic Input Current±10m              | ìΑ |

| Output Current, Each Phase 500m      | ηA |

| Output Current, Emitter Follower500m | nΑ |

| Power Dissipation, (Note)            | W  |

|                                      |    |

Power Dissipation, (Note)

2W

Junction Temperature

150°C

Ambient Temperature, UC1517

-55°C to +125°C

Ambient Temperature, UC3517

0°C to +70°C

Storage Temperature

-55°C to +150°C

Note: Consult Packaging section of Databook for thermal limitations and considerations of package.

# **BLOCK DIAGRAM**

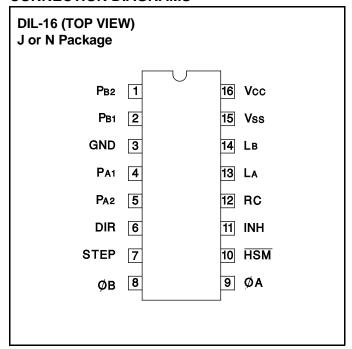

### **CONNECTION DIAGRAMS**

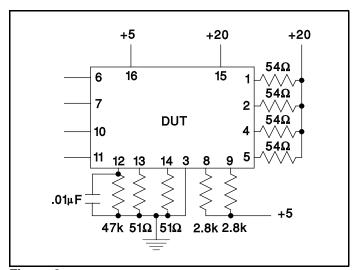

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for TA = -55°C to +125°C for the UC1517 and 0°C to +70°C for the UC3517, Vcc=5V, Vss = 20V, TA=TJ. Pin numbers refer to DIL-16 package.

|                                    |                                   | UC1  | UNITS |      |    |  |

|------------------------------------|-----------------------------------|------|-------|------|----|--|

| PARAMETER                          | TEST CONDITIONS                   | MIN  | TYP   | MAX  |    |  |

| Logic Supply, Vcc                  | Pin 16                            | 4.75 |       | 5.25 | V  |  |

| Second Supply, Vss                 | Pin 15                            | 10   |       | 40   | V  |  |

| Logic Supply Current               | VINH = 0.4V                       |      | 45    | 60   | mA |  |

|                                    | VINH = 4.0V                       |      | 12    |      | mA |  |

| Input Low Voltage                  | Pins 6, 7, 10, 11                 |      |       | 0.8  | V  |  |

| Input High Voltage                 | Pins 6, 7, 10, 11                 | 2.0  |       |      | V  |  |

| Input Low Current                  | Pins 6, 7, 10, 11; V = 0V         | -400 |       |      | μΑ |  |

| Input High Current                 | Pins 6, 7, 10, 11; V = 5V         |      |       | 20   | μΑ |  |

| Phase Output Saturation Voltage    | Pins 1, 2, 4, 5; I = 350mA        |      | 0.6   | 0.85 | V  |  |

| Phase Output Leakage Current       | Pins 1, 2, 4, 5; V = 39V          |      |       | 500  | μΑ |  |

| Follower Saturation Voltage to Vss | Pins 13,14; I = 350mA             |      |       | -2   | V  |  |

| Follower Leakage Current           | Pins 13,14; V = 0V                |      |       | 500  | μΑ |  |

| Output Low Voltage, ØA, ØB         | Pins 8, 9; I = 1.6mA              |      | 0.1   | 0.4  | V  |  |

| Phase Turn-On Time                 | Pins 1, 2, 4, 5                   |      | 2     |      | μs |  |

| Phase Turn-Off Time                | Pins 1, 2, 4, 5                   |      | 1.8   |      | μs |  |

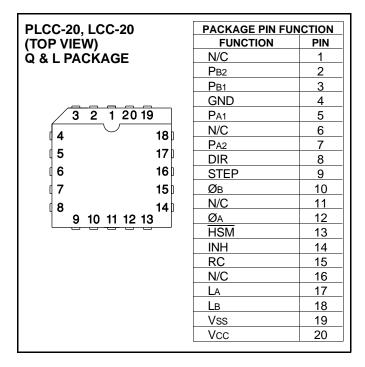

| Second-Level On Time. TMONO        | Pins 13,14; Figure 3 Test Circuit | 275  | 325   | 375  | μs |  |

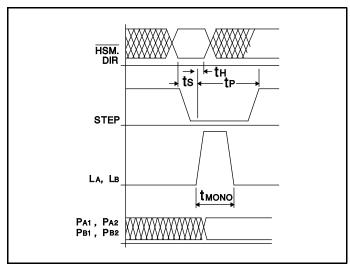

| Logic Input Set-up Time, ts        | Pins 6, 10; Figure 4              | 400  |       |      | ns |  |

| Logic Input Hold Time, th          | Pins 6, 10; Figure 4              | 0    |       |      | ns |  |

| STEP Pulse Width, tP               | Pin 7; Figure 4                   | 800  |       |      | ns |  |

| Timing Resistor Value              | Pin 12                            | 1k   |       | 100k | Ω  |  |

| Timing Capacitor Value             | Pin 12                            | 0.1  |       | 500  | nF |  |

| Power-On Threshold                 | Pin 16                            |      | 4.3   |      | V  |  |

| Power-Off Threshold                | Pin 16                            |      | 3.8   |      | V  |  |

| Power Hysteresis                   | Pin 16                            |      | 0.5   |      | V  |  |

Figure 3. Test Circuit

#### PIN DESCRIPTION

**Vcc**: Vcc is the UC3517's logic supply. Connect to a regulated 5VDC, and bypass with a  $0.1\mu F$  ceramic capacitor to absorb switching transients.

**VMM:** VMM is the primary motor supply. It connects to the UC3517 phase outputs through the motor windings. Limit this supply to less than 40V to prevent breakdown of the phase output transistors. Select the nominal VMM voltage for the desired continuous winding current.

Vss: Vss is the secondary motor supply. It drives the LA and LB outputs of the UC3517 when a monostable in the UC3517 is active. In the bilevel application, this supply is applied to the motor to charge the winding inductance faster than the primary supply could. Typically, Vss is higher in voltage than VMM, although Vss must be less than 40V. The Vss supply should have good transient capability.

**GROUND:** The ground pin is the common reference for all supplies, inputs and outputs.

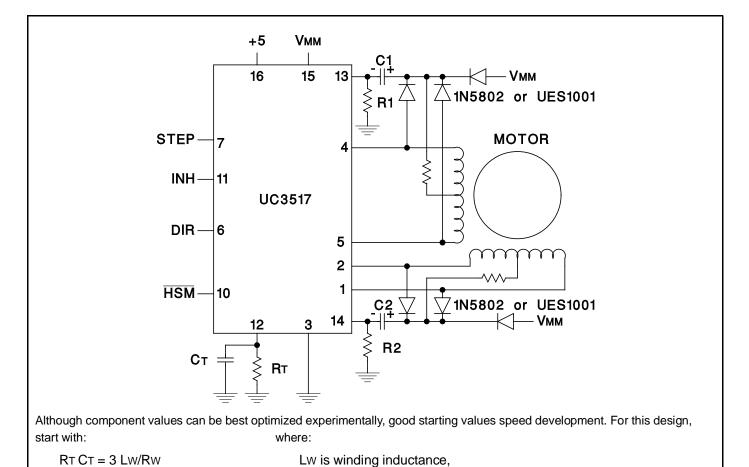

**RC:** RC controls the timing functions of the monostables in the UC3517. It is normally connected to a resistor (RT) and a capacitor (CT) to ground, as shown in Figure 3. Monostable on time is determined by the formula  $TON \approx 0.69 \ RT \ CT$ . To keep the monostable on indefinitely, pull RC to Vcc through a 50k resistor. The UC3517 contains only one RC pin for two monostables. If step rates comparable to TON are commanded, incorrect pulsing can result, so consider maximum step rates when selecting RT and CT. Keep  $TON \le T$  STEP MAX.

ØA and ØB: These logic outputs indicate half-step position. These outputs are open-collector, low-current drivers, and may directly drive TTL logic. They can also drive CMOS logic if a pull-up resistor is provided. Systems which use the UC3517 as an encoder and use a different driver can use these outputs to disable the external driver.

Figure 4. Timing Waveforms

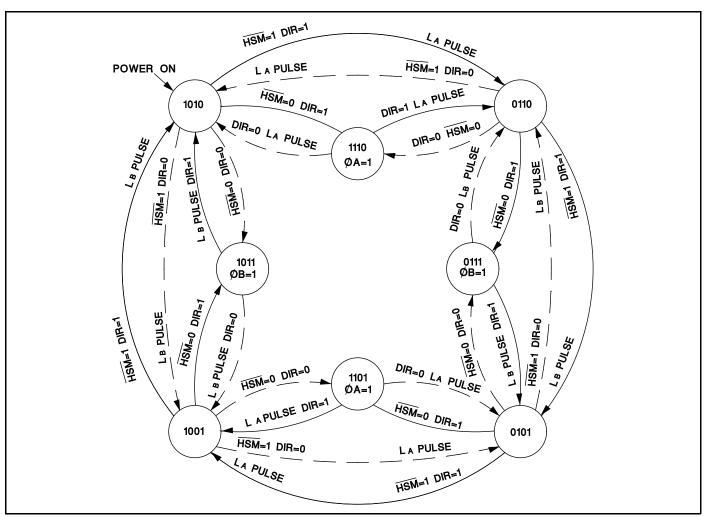

as shown in Figure 8. The sequencing of these outputs is shown in Figure 5.

PA1, PA2, PB1, and PB2: The phase outputs pull to ground sequentially to cause motor stepping, according to the state diagram of Figure 5. The sequence of stepping on these lines, as well as with the LA and LB lines is controlled by STEP input, the DIR input, and the HSM input. Caution: If these outputs or any other IC pins are pulled too far below ground either continuously or in a transient, step memory can be lost. It is recommended that these pins be clamped to ground and supply with high-speed diodes when driving inductive loads such as motor windings or solenoids. This clamping is very important because one side of the winding can "kick" in a direction opposite the swing of the other side.

LA and LB: These outputs pull to Vss when their corresponding monostable is active, and will remain high until the monostable time elapses. Before and after, these outputs are high-impedance. For detail timing information, consult Figure 5.

**STEP:** This logic input clocks the logic in the UC3517 on every falling edge. Like all other UC3517 inputs, this input is TTL/CMOS compatible, and should not be pulled below ground.

**DIR:** This logic input controls the motor rotation direction by controlling the phase output sequence as shown in Figure 5. This signal must be stable 400ns before a falling edge on STEP, and must remain stable through the edge to insure correct stepping.

**HSM:** This <u>logic</u> input switches the UC35<u>17</u> between halfstepping (HSM = low) and full-stepping (HSM = high) by controlling the phase output sequence as show in Figure 5. This line requires the same set-up time as the DIR input, and has the same hold requirement. **INH:** When the inhibit input is high, the phase and  $\theta$  outputs are inhibited (high impedance). STEP pulses received while inhibited will continue to update logic in the IC, but the states will not be reflected at the outputs until inhibit is pulled low. In stepper motor systems, this can be used to save power or to allow the rotor to move freely for manual repositioning.

#### **OPERATING MODES**

The UC3517 is a system component capable of many different operating modes, including:

**Unipolar Stepper Driver:** In its simplest form, the UC3517 can be connected to a stepper motor as a unipolar driver. LA, LB, RC and Vss are not used, and may be left open. All other system design considerations mentioned above apply, including choice of motor supply VMM, undershoot diodes and timing considerations.

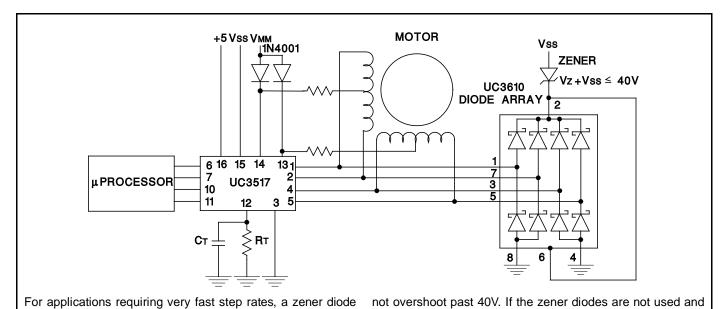

**Unipolar Bilevel Stepper Driver:** If increased step rates are desired, the application circuit of Figure 6 makes use of the monostables and emitter followers as well as the configuration mentioned above to provide high-voltage pulses to the motor windings when the phase is turned on. For a given dissipation level, this mode offers faster step rates, and very little additional electrical noise.

The choice of monostable components can be estimated based on the timing relationship of motor current and voltage: V = LdI/dt. Assuming a fixed secondary supply voltage (Vss), a fixed winding inductance (LM), a desired winding peak current (IW), and no back EMF from the motor, we can estimate that  $RTCT = 1.449 \ lwLm/Vss$ . In practice, these calculations should be confirmed and adjusted to accommodate for effects not modeled.

**Voltage-Doubled Mode:** The UC3517 can also be used to generate higher voltages than available with the system power supplies using capacitors and diodes. Figure 9 shows how this might be done, and gives some estimates for the component values.

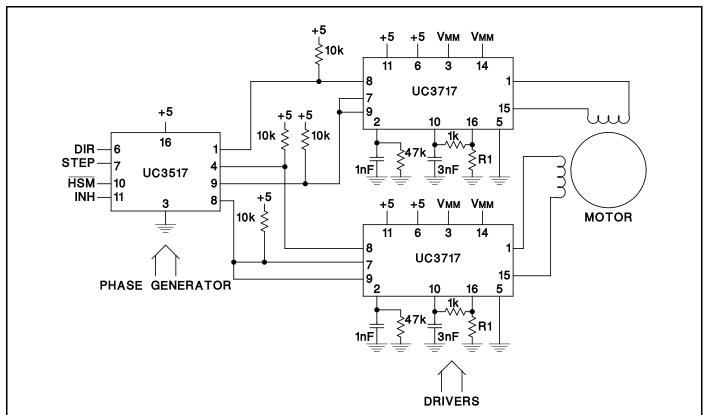

**Higher Current Operation:** For systems requiring more than 350mA of drive per phase, the UC3717A can be

used in conjunction with discrete power transistors or power driver ICs, like the L298. These can be connected as current gain devices that turn on when the phase outputs turn on.

**Bipolar Motor Drive:** Bipolar motors can be controlled by the UC3517 with the addition of bipolar integrated drivers such as the UC3717A (Figure 8) and the L298, or discrete devices. Care should be taken with discrete devices to avoid potential cross-conduction problems.

#### LOGIC FLOW GRAPH

The UC3517 contains a bidirectional counter which is decoded to generate the correct phase and Ø outputs. This counter is incremented on every falling edge of the STEP input. Figure 5 shows a graph representing the counter sequence, inputs that determine the next state (DIR and HSM), and the outputs at each state. Each circle represents a unique logic state, and the four inside circles represent the half-step states.

The four bits inside the circles represent the phase outputs in each state (PA1, PA2, PB1, and PB2). For example, the circle labeled 1010 is immediately entered when the device is powered up, and represents PA1 off ("1" or high), PA2 on ("0" or low), PB1 off ("1" or high) and PB2 on ("0" or low). The ØA and ØB outputs are both low (unidentified).

The arrows in the graph show the state changes. For example, if the IC is in state 0110, DIR is high, HSM is high, and STEP falls, the next state will be 0101, and a pulse will be generated on the LB line by the monostable.

Inhibit will not effect the logic state, but it will cause all phase outputs and both  $\varnothing$  outputs to go high (off). A falling edge on STEP will still cause a state change, but inhibit will have to toggle low for the state to be apparent.

A falling edge on STEP with HSM high will cause the counter to advance to the next full step state regardless of whether or not it was in a full step state previously.

No LA or LB pulses are generated entering half-states.

Figure 5. Logic Flow Graph

Figure 6. Bilevel Motor Driver

permits windings to discharge at higher voltages, and higher

rates. Driver transistor breakdown must be considered when selecting Vss and zener voltage to insure that the outputs will

be used.

UC3610 pin 2 is connected directly to Vss then higher Vss can

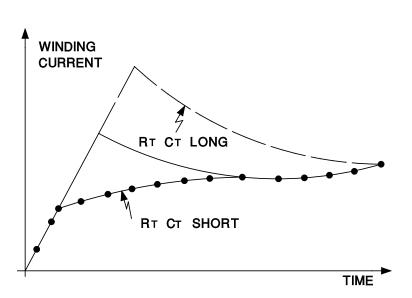

Experimental selection of RT and CT allow the designer to select a small amount of winding current overshoot, as shown above. Although the overshoot may exceed the continuous rated current of the winding and the drive transistors, the dura-

tion can be well controlled. Average power dissipation for the driver and motor must be considered when designing systems with intentional overshoot, and must stay within conservative limits for short duty cycles.

Figure 7. Effects of Different RT & CT on Bilevel Systems

In this application, the  $\varnothing$ A and  $\varnothing$ B outputs of the UC3517 are connected to the current program inputs of the UC3717. This allows the UC3517 inhibit signal to inhibit the UC3717, and

also allows half-step operation of the UC3717. Peak motor winding current will be limited to approximately .42V/R1 by chopping.

Figure 8. Interface to UC3717 Bipolar Driver

Rw is winding resistance,

IR is rated winding current, and

TMIN is minimum step period expected.

Figure 9. Using the UC3517 as a Voltage Doubler

$C_1 = C_2 = Lw IR/Rw$

$R_1 = R_2 = 2.9 \text{ TMIN/C1}$

ww.ti.com

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|-------------------------|----------------------|------------------------------|-----------------------------|

| UC1517J          | OBSOLETE              |              | UTR                | 16   |             | TBD                     | Call TI              | Call TI                      | Add to cart                 |

| UC1517J883B      | OBSOLETE              |              | UTR                | 16   |             | TBD                     | Call TI              | Call TI                      | Add to cart                 |

| UC1517L          | OBSOLETE              |              | UTR                | 20   |             | TBD                     | Call TI              | Call TI                      | Add to cart                 |

| UC3517N          | OBSOLETE              | PDIP         | N                  | 16   |             | TBD                     | Call TI              | Call TI                      | Add to cart                 |

| UC3517Q          | OBSOLETE              | PLCC         | FN                 | 20   |             | TBD                     | Call TI              | Call TI                      | Add to cart                 |

| UC3517QTR        | OBSOLETE              | PLCC         | FN                 | 20   |             | TBD                     | Call TI              | Call TI                      | Add to cart                 |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC1517, UC3517:

www.ti.com 9-May-2012

Military: UC1517

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Military QML certified for Military and Defense Applications

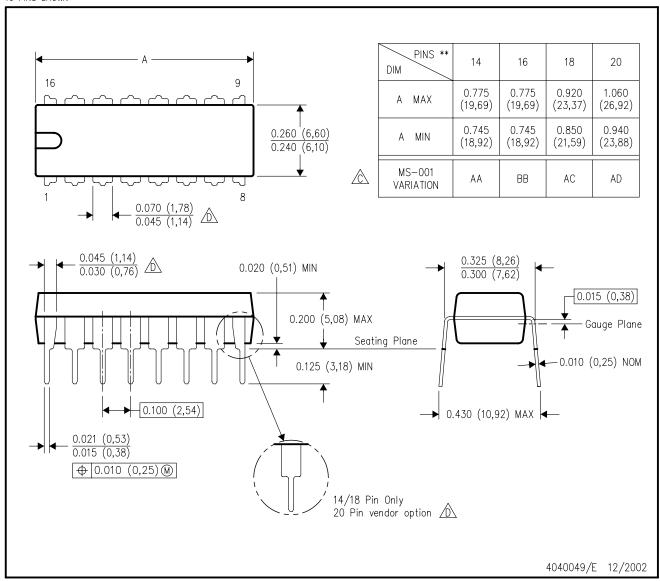

# N (R-PDIP-T\*\*)

# PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- The 20 pin end lead shoulder width is a vendor option, either half or full width.

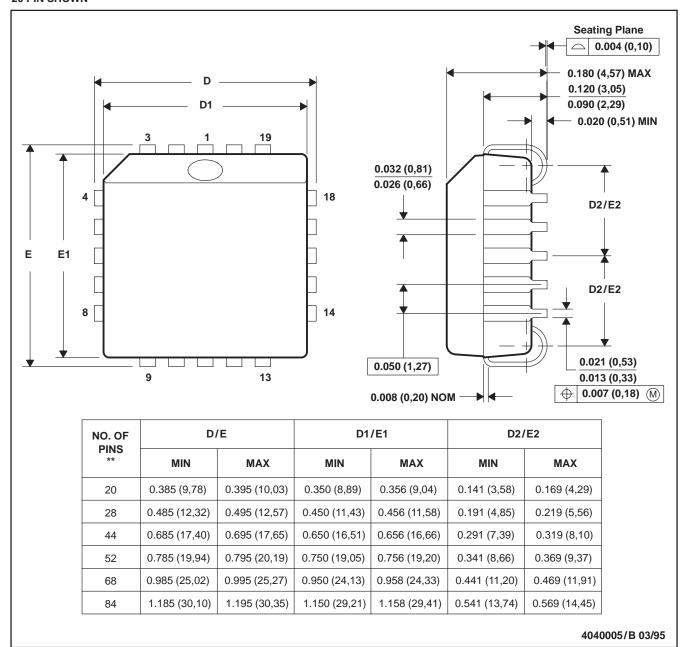

### FN (S-PQCC-J\*\*)

#### 20 PIN SHOWN

### PLASTIC J-LEADED CHIP CARRIER

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-018

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

**Applications**

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Products**

Wireless Connectivity

#### Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications dataconverter.ti.com Computers and Peripherals www.ti.com/computers **Data Converters DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security Power Mgmt www.ti.com/space-avionics-defense power.ti.com Space, Avionics and Defense Microcontrollers Video and Imaging microcontroller.ti.com www.ti.com/video www.ti-rfid.com **OMAP Mobile Processors** www.ti.com/omap

TI E2E Community Home Page

www.ti.com/wirelessconnectivity

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated

e2e.ti.com