# **TSFJ SERIES**

## MIXED ANALOG - DIGITAL BIPOLAR ARRAYS

- ADVANCED BIPOLAR TECHNOLOGY :

- NPN, F<sub>T</sub> = 3GHz

- 2 METAL LAYER

- 100MHz, ECL FUNCTIONS

- FULL ESD PROTECTION

- POWER SUPPLY : MAXIMUM RATINGS = UP TO 15V OPERATING CONDITIONS = 3 TO 12V

- ANALOG DIGITAL ARRAYS :

- ANALOG TILES

- ECL TILE FOR HIGH SPEED LOGIC

- I2L CORE FOR LOW FREQUENCY RAN-DOM LOGIC

- POWER TILE WITH 200mA CAPABILITY

- 5 ARRAYS AVAILABLE :

- J4, J6, J9, J13, J23 FROM 600 TO 3000 COM-PONENTS

- CAD SOFTWARE SUPPORT :

- ADS-PC (analog design system PC)

- FULLY INTEGRATED IN PC ENVIRON-MENT

- P-CAD<sup>®</sup> SOFTWARE, FOR SCHEMATIC CAPTURE, SIMULATION, AND LAYOUT

- OPERATING TEMPERATURE RANGE : COMMERCIAL : 0 TO 70C INDUSTRIAL : - 40 TO + 85C MILITARY : - 55 TO + 125C

- PACKAGE OPTIONS DIL : PLASTIC OR CERAMIC SMD : SO, PLCC, LCCC, QFP

#### USIC PRODUCTS DESCRIPTION

SGS-THOMSON Microelectronics introduces the mixed analog-digital arrays developped on a 3GHz process. Using the expertise in bipolar arrays, SGS-THOMSON has developped this new series to offer a product taking the leading edge of any technology :

- High speed process (NPN, FT = 3GHz)

- Architecture with tile concept to improve the efficiency of the placement and routing

- 2 customized metal layers with 4 masks to personalize (contact, M1, via, M2)

- Complete CAD system on a PC from schematic capture up to the layout.

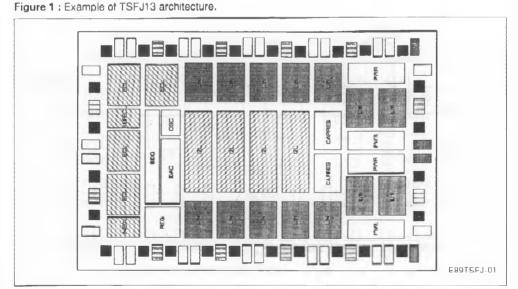

## **TSFJ ARCHITECTURE**

#### TECHNOLOGY

TSFJ series developped by SGS-THOMSON is using an advanced bipolar process with high frequency performance (NPN,  $F_t = 3$ GHz). With a double metal layer the parasitic elements are minimized to improve the layout density and to increase the performances.

The process is very well suited for accurate analog bipolar design. The other key feature is introduced with the digital capability using either ECL functions or I2L ones.

Thanks to protection network placed on each input pad, the complete TSFJ series is protected against ESD parasitic effects.

#### TILE ARCHITECTURE

The TSFJ series has an architecture based on a tile concept in order to take advantage of efficient layout.

For SGS-THOMSON a tile is an optimized placement of basic components such as transistors, resistors, and capacitors, with no routing done in advance. When customisation is prepared, the designer optimized the routing of each tile according to his needs.

6 different types of tiles have been developped :

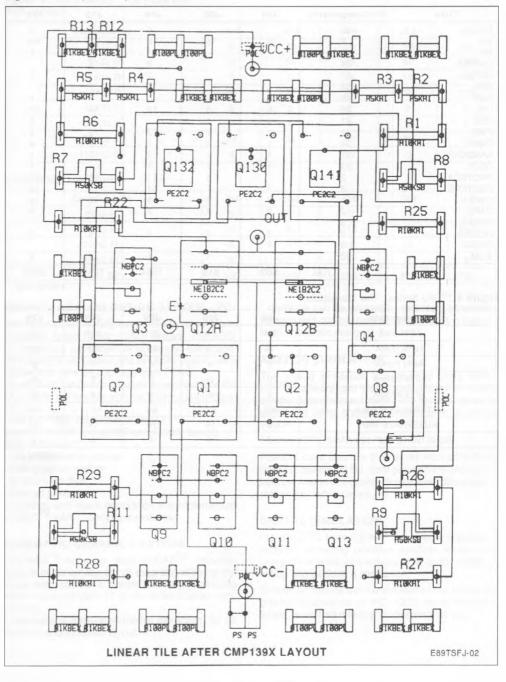

LINEAR TILE, optimized for analog functions (op amps, comparators, ...)

- 6 standard NPN (h<sub>FE</sub> = 105, and I<sub>c</sub> = 100A)

- 2 low noise NPN

- 7 lateral PNP ( $h_{FE} = 52$ , and  $l_c = 1A$ )

- \_ 44 resistances from 100 ohms to 50KΩ

- POWER TILE, optimized for power interface capability ;

- 4 standard substrate PNP

- 1 power substrate PNP (I<sub>KF</sub> = 10mA)

- 1 power NPN (I<sub>KF</sub> = 314mA)

- 1 medium power NPN (I<sub>KF</sub> = 78mA)

- 3 std NPN

- I2L LOGIC TILE, optimized to implement random logic using standard I2L functions (NAND, AND, NOR, OR, Flip-flop, ...)

row of I2L operators

- ECL LOGIC TILE, optimized for high speed logic up to 100MHz

- equivalent to 1 D flip-flop or 5 NOR gates

- BUILT-IN FUNCTION TILES, a certain number of predefined tile have been created to fulfill some specific analog requests such as;

- 1 bandgap voltage reference

- 1 oscillator (RC or quartz)

- 1 voltage regulator

- 1 R-2R resistor ladder for 6 bits DAC

- RESISTOR/CAPACITOR TILE, optimized for RC network or compensation capacitor purpose

- 2.5pF and 7pF capacitor available

Figure 2 : Example of a symbolic Linear Tile.

| Tiles   | Nb Components | J04 | J06 | J09  | J13  | J23  |

|---------|---------------|-----|-----|------|------|------|

| ECL     | 86            |     |     | 4    | 4    | 5    |

| 12L     | 9             | 6   | 15  | 18   | 36   | 54   |

| HF      | 46            |     |     | 1    | 1    | 1    |

| CAPRES  | 24            |     |     | 2    | 2    |      |

| REFECL  | 31            |     |     | 1    | 1    | 1    |

| DAC     | 33            |     |     | 1    | 1    |      |

| R2R     | 46            |     |     |      |      | 1    |

| LIN     | 59            | 6   | 8   | 10   | 14   | 24   |

| RES     | 21            | 1   | 1   |      |      | 4    |

| PWR     | 34            | 1   | 2   | 2    | 2    | 4    |

| PWR1    | 34            | 1   | 2   | 2    | 2    | 4    |

| BANDGAP | 37            | 1   | 1   | 1    | 1    | 1    |

| OSCIL   | 23            | 1   | 1   | 1    | 1    | 1    |

| PROTECA | 2             | 7   | 8   | 11   | 13   | 18   |

| PROTECB | 2             | 7   | 7   | 11   | 13   | 18   |

| CAP1    | 1             | 4   | 6   | 8    | 8    | 10   |

| CAP2    | 2             | 2   | 4   | 2    | 4    | 9    |

| CAPAS   | 3             |     | 1   |      |      |      |

| DIODES  | 2             | 2   | 4   | 4    | 4    | 8    |

| PUISS   | 3             | 1   |     |      |      |      |

| ALIM    | 40            |     | 1   | 1    | 1    | 2    |

|         | TOTAL :       | 600 | 919 | 1554 | 1964 | 3067 |

Figure 3 : TSFJ Series : The Available Tiles.

Figure 4 : TSFJ Series : The Transistors.

| Components         | J04 | J06 | 109 | J13 | J23 |

|--------------------|-----|-----|-----|-----|-----|

| NPN 5mA            | 54  | 79  | 201 | 225 | 331 |

| NPN 16mA           | 14  | 18  | 24  | 32  | 52  |

| NPN 50mA           | 2   | 4   | 4   | 4   | 6   |

| NPN 100mA          | 2   | 2   | 2   | 2   | 4   |

| NPN 200mA          | 2   | 4   | 4   | 4   | 8   |

| LATERAL PNP 60µA   | 50  | 68  | 83  | 111 | 184 |

| SUBSTRATE PNP      | 8   | 16  | 16  | 16  | 32  |

| SUBSTRATE PNP 10mA | 2   | 4   | 4   | 4   | 8   |

E88TSFJ-04

E66TSFJ-05

## Figure 5 : TSFJ Series : The Resistors. (high values)

| Components | J04 | J06 | 109 | J13 | J23 |

|------------|-----|-----|-----|-----|-----|

| 3KQ RI     | 0   | 0   | 10  | 10  | 10  |

| 5KΩ RI     | 36  | 56  | 64  | 80  | 136 |

| 8KΩ RI     | 0   | 0   | 18  | 18  | 18  |

| 10KΩ RI    | 64  | 80  | 96  | 128 | 202 |

| 40KΩ RI    | 0   | 2   | 2   | 2   | 2   |

| 50KΩ RI    | 0   | 4   | 4   | 4   | 4   |

| 50KΩ SB    | 24  | 32  | 40  | 56  | 88  |

| 100KΩ SB   | 4   | 4   | 12  | 12  | 20  |

(medium and low values)

| Components | J04 | J06 | J09 | J13 | J23 |

|------------|-----|-----|-----|-----|-----|

| 300 PL     | 9   | 17  | 17  | 17  | 33  |

| 100Ω PL    | 60  | 80  | 116 | 156 | 260 |

| 2000 PL    | 0   | Ô   | 16  | 16  | 20  |

| 300Ω PL    | 0   | Q   | g   | 9   | 8   |

| 1KO BEX    | 130 | 182 | 398 | 470 | 720 |

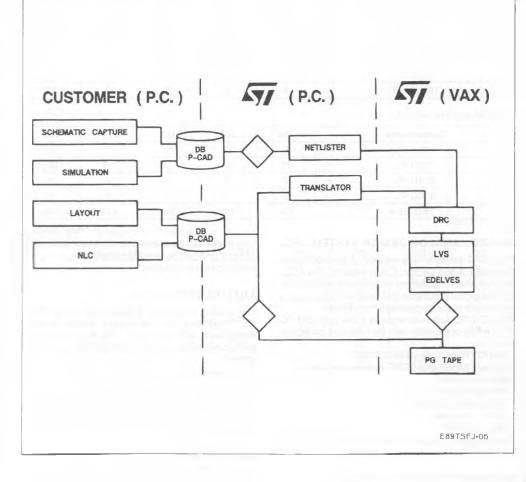

#### ADS-PC : ANALOG DESIGN SYSTEM - PC

The TSFJ series is fully supported by a complete Computer Aided Design (CAD) system. The ADS-PC tool offers capabilities of schematic entry, analog and digital simulation and symbolic layout, using a standard software package from PCAD.

The ADS-PC software requires a low cost IBM PC AT3 or fully compatible with the following configuration :

- 640 KO RAM, coprocessor 80287

optional : 80386 and 80387 accelerator boards 2MB EMS board

- microsoft parallel mouse

- EGA graphic monitor

- 30 MÖ hard disk

- laser jet printer

Checkings and mask generation are implemented on DEC<sup>M</sup> VAX<sup>M</sup> computer systems.

#### SCHEMATIC GRAPHIC CAPTURE

PC-CAPS<sup>™</sup> software, from P-CAD<sup>™</sup>, provides capture of schematic circuit diagram, allowing the circuit description in a hierarchical way<sup>∞</sup> and using either macrocell from ST library or basic array components.

A database is generated (netlist extraction) for simulation and symbolic layout.  (symbols can be created to represent schematic designs and can be used as components in higherlevel schematic designs)

#### ANALOG SIMULATION

The analog simulation is performed using PSPI-CE<sup>TM</sup> software and the models library tor basic components and macrocells. The result analysis is performed using graphic representation on listing edition.

#### \* from MICROSIM

PSPICE input files are the net list from schematic capture, command file, configuration file and simulation environment (active device level description, technology worst cases...).

#### DIGITAL SIMULATION

PC-LOGS<sup>TM</sup>, from P-CAD<sup>TM</sup>, is a logic simulation program providing primitive symbols library and using commands Interactively or in batch mode to set up and perform a simulation.

Simulation results can be displaid to the screen in graphic or tabular forms. PC-LOGS inputs are of two types : a verified netlist and user commands.

## **TSFJ SERIES**

815

## PLACEMENT AND ROUTING

PC-CARDS<sup>TM</sup>, from P-CAD<sup>TM</sup>, is built around an intelligent database that continually keeps track of components and connectivities. The on-screen menu includes commands to draw, edit, move, delete, zoom in and out, view selected window.

## CUSTOMER DESIGN INTERFACE

SGS-THOMSON has developped several interfaces for customers, giving them easy and flexible design approaches for TSFJ mixed analog/ digital bipolar arrays.

User can access ADS-PC system ; - via the SGS-THOMSON Design centers - via CAE workstations using a PC configuration and the P-CAD  $^{\rm TM}$  software package

According to all of these design possibilities, SGS-THOMSON defined 2 main customer interfaces. Next figure outlines these interfaces. Each interface delimits the responsabilities of customer and SGS-THOMSON during circuit development flow.

|                                           | Interface 2 | Interface 3 |

|-------------------------------------------|-------------|-------------|

| Definition of Circuit Specifications      | Customer    | Customer    |

| Electrical Description (analog + digital) | Customer    | Customer    |

| Test Procedure                            | Customer    | Customer    |

| Graphic Capture + Input Signal Entry      | ST          | Customer    |

| Design Verification                       | ST          | Customer    |

| Simulation (analog + digital)             | ST          | Customer    |

| Approval                                  | Customer    | Customer/ST |

| Place and Route                           | ST          | Customer    |

| Final Design Release                      | Customer    | Customer/ST |

| Test Program Generation + Test Tooling    | ST          | ST          |

| Mask Tooling                              | ST          | ST          |

| Prototype Manufacturing                   | ST          | ST          |

| Prototype Delivery                        | ST          | ST          |

With interface 3, design can be done either at SGS-THOMSON Microelectronics design center facilities or at customer location.

#### ABSOLUTE MAXIMUM RATINGS (note 1) Tamb = 25°C, Voltage Referenced to V-

| Quarter | Parameter                     | Value |       |      |  |

|---------|-------------------------------|-------|-------|------|--|

| Symbol  | Parameter                     | Min.  | Max.  | Unit |  |

| V+      | Supply Voltage                | - 0.5 | + 15  | V    |  |

| Tstg    | Storage Temperature (ceramic) | - 60  | + 150 | °C   |  |

|         | Storage Temperature (plastic) | - 40  | + 125 | C    |  |

Note : 1. Stresses above those listed order "maximum rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these on any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED DC OPERATING CONDITIONS, Voltage Referenced to V-

| Quanta | Parameter                |                                      |                   | Yaluc |                    |      |

|--------|--------------------------|--------------------------------------|-------------------|-------|--------------------|------|

| Symbol | Parameter                |                                      | Min-              | Тур.  | Max.               | Unit |

| V+     | Operating Supply Voltage |                                      | 3                 |       | 12                 | Y.   |

| Tamb   |                          | Military<br>Industrial<br>Commercial | - 55<br>- 40<br>0 |       | +125<br>+85<br>+70 | °C   |

## **TSFJ SERIES**

## DC GENERAL ELECTRICAL CHARACTERISTICS

| Symbol                                                                                                    | Parameter                                                                                   | Test Conditions                                                                                                                        |                | Value      |                                    | Unit                |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|------------------------------------|---------------------|

| Symbol                                                                                                    | Parameter                                                                                   | Test Conditions                                                                                                                        | Min.           | Тур.       | Max.                               | Unit                |

|                                                                                                           | Resistors                                                                                   |                                                                                                                                        |                |            |                                    |                     |

| P₊                                                                                                        | P. Diffusion                                                                                | Resistor Value Range<br>Absolute Accuracy<br>Matching (note 1)<br>Matching (note 2)<br>Temperature Coefficient (1 <sup>st</sup> order) | 30             |            | 420<br>± 25<br>± 2<br>± 6<br>0.12  | Ω<br>%<br>%<br>%    |

| Bext                                                                                                      | Extrinsec Base Region                                                                       | Resitor Value Range<br>Absolute Accuracy<br>Matching (1)<br>Matching (2)<br>Temperature Coefficient (1 <sup>st</sup> order)            | 270            |            | 5000<br>± 15<br>± 2<br>± 6<br>0.09 | Ω<br>%<br>%<br>%/°C |

| Rı                                                                                                        | Implanted Resitor                                                                           | Resitor Value Range<br>Absolute Accuracy<br>Matching (1)<br>Matching (2)<br>Temperature Coefficient (1 <sup>st</sup> order)            | 5              |            | 50<br>± 15<br>± 2<br>± 6<br>0.21   | κΩ<br>%<br>%<br>%℃  |

| BINT                                                                                                      | Intrinsec Base Region                                                                       | Resitor Value Range<br>Absolute Accuracy<br>Matching (1)<br>Matching (2)                                                               | 50             |            | 100<br>± 25<br>± 2<br>± 6          | ΚΩ<br>%<br>%        |

|                                                                                                           | Capacitors                                                                                  | Capacitor Value Range<br>Absolute Accuracy                                                                                             | 2.5            |            | 7<br>± 20                          | pF<br>%             |

| V.                                                                                                        |                                                                                             | Maximum Operating Voltage                                                                                                              |                |            | 20                                 | V                   |

| NBPC1<br>VBCB0<br>VBCE0<br>VBCS0<br>HFE<br>IKF                                                            | Breakdown Voltage<br>Breakdown Voltage<br>Breakdown Voltage<br>Current Gain<br>Knee Current | std NPN Transistor (note 3)<br>Collector-base<br>Collector-emitter<br>Collector-substrate<br>@ I <sub>c</sub> = 100μA                  | 40<br>18<br>40 | 100<br>5.6 |                                    | V<br>V<br>V<br>mA   |

| NPWR<br>V <sub>BCB0</sub><br>V <sub>BCE0</sub><br>V <sub>BCS0</sub><br>H <sub>FE</sub><br>I <sub>KF</sub> | Breakdown Voltage<br>Breakdown Voltage<br>Breakdown Voltage<br>Current Gain<br>Knee Current | Power NPN Transistor (note 3)<br>Collector-base<br>Collector-emitter<br>Collector-substrate<br>@ I <sub>c</sub> = 10mA                 | 40<br>18<br>40 | 140<br>314 |                                    | V<br>V<br>V<br>mA   |

Notes= 1. matching between 2 resistors of the same value, closed to each other and with the same orientation on the die.

2. matching between 2 resistors of different values, close one from the other and with the same orientation on the die.

3. for more informations refer to the TSFJ user's manual.

4. voltage references are provided by an "ECL reference" macrocell (REFECL) built on a specific tile.

5. input voltages could be supplied by a specific tile called HFECL.

6. output levels are not compatible with standard 10K, 100K ECL series.

## DC GENERAL ELECTRICAL CHARACTERISTICS (continued)

|                 |                   |                                       |      | Value |      | Unit |

|-----------------|-------------------|---------------------------------------|------|-------|------|------|

| Symbol          | Parameter         | Test Conditions                       | Min. | Тур.  | Max. | Unit |

| PNPS            |                   | Substrate PNP Transistor (note 3)     |      |       |      |      |

| VBCBO           | Breakdown Voltage | Collector-base                        | 40   |       |      | V    |

| VBCEO           | Breakdown Voltage | Collector-emitter                     | 18   |       |      | V    |

| VBCSO           | Breakdown Voltage | Collector-substrate                   | 40   |       |      | V    |

| HEE             | Current Gain      | $@ I_c = 1 \mu A$                     |      | 160   |      |      |

| IKE             | Knee Current      |                                       |      | 40    |      | μA   |

|                 |                   | ECL Cells (V <sub>+</sub> = 5V ± 10%) |      |       |      |      |

| VB              | Vreference        | Voltage Reference (note 4)            |      | .97   |      | V    |

| V <sub>T1</sub> | Vreference        | Voltage Reference (note 4)            |      | 3.92  |      | V    |

| V <sub>T2</sub> | Vreterence        | Voltage Reference (note 4)            |      | 3.20  |      | V    |

| VIL             | Input Voltage     | (note 5)                              |      |       | 3.6  | V    |

| VIH             | Input Voltage     | (note 5)                              | 4.3  |       |      | V    |

| VOL             | Output Voltage    | (note 6)                              |      |       | 3.6  | V    |

| VOH             | Output Voltage    | (note 6)                              | 4.3  |       |      | V    |

Notes : 1. matching between 2 resistors of the same value, closed to each other and with the same orientation on the die.

2. matching between 2 resistors of different values, close one from the other and with the same orientation on the die. 3. for more informations refer to the TSFJ user's manual.

voltage references are provided by an "ECL reference" macrocell (REFECL) built on a specific tile.

input voltages could be supplied by a specific tile called HEECL.

6. output levels are not compatible with standard 10K, 100K ECL series

## DIGITAL LIBRARY AC ELECTRICAL CHARACTERISTICS ABSTRACT

(unless otherwise specified,  $T_{amb} = 25^{\circ}C$ , typical process)

|                | Description               | Tool Openditions                                                                   |      | Value |                  | Unit              |

|----------------|---------------------------|------------------------------------------------------------------------------------|------|-------|------------------|-------------------|

| Symbol         | Parameter Test Conditions | Min.                                                                               | Тур. | Max.  | Unit             |                   |

|                |                           | ECL CELLS                                                                          |      |       |                  |                   |

| Vs             | Voltage Swing             |                                                                                    |      | 600   |                  | mV                |

| TG             | Toggle Frequency          | D Type Flip-flop                                                                   |      |       | 100              | MHz               |

| <b>t</b> plh   | Propagation Delay         | NAND2, (FO = 1)                                                                    |      | 1.1   |                  | ns                |

| <b>t</b> PHL   | Propagation Delay         | NAND2, $(FO = 1)$                                                                  |      | 3.2   |                  | ns                |

|                |                           | I2L CELLS (note 7)                                                                 |      |       |                  |                   |

| T <sub>G</sub> | Toggle Frequency          | D Type Flip-flop<br>@ Injection = 0.1μA<br>@ Injection = 1μA<br>@ Injection = 10μA |      |       | 20<br>160<br>600 | KHz<br>KHz<br>KHz |

Note : 7. I2L cells have been caracterised between 0.1µA and 100µA.

## ANALOG LIBRARY, AC ELECTRICAL CHARACTERISTICS ABSTRACT

(unless otherwise specified, Tamb = 25°C, typical process)

<u>JOPA1</u> (programmable operationnal amplifier)  $V_{CC} \pm 6V$ ,  $I_{set} = 20\mu A$

| Symbol | Parameter              | Test Conditions               | Typical Value | Unit |

|--------|------------------------|-------------------------------|---------------|------|

| В      | Unity Gain Bandwidth   | RL = 5KΩ ; CL = 20pF          | 1             | MHz  |

| φM     | Phase Margin           | Av = 1 ; RL = 5KΩ ; CL = 20pF | 60            |      |

| Svo    | Slew Rate              | Av = 1 ; RL = 5KΩ ; CL = 20pF | 0.35          | V/µs |

| Av     | Open-loop Voltage Gain | $RL = 5K\Omega$ ; $CL = 20pF$ | 90            | dB   |

## JCOMP1 (programmable voltage comparator - LM139 type)

| Symbol | Parameter                  | Test Conditions                                        | Typical Value | Unit |

|--------|----------------------------|--------------------------------------------------------|---------------|------|

| tref   | Large Signal Response Time | $RL = 5K\Omega$ ; $CL = 2pF$ with<br>Overdrive : 100mV | 300           | ms   |

| tre    | Small Signal Response Time | $RL = 5K\Omega$ ; $CL = 2pF$ with<br>Overdrive : $5mV$ | 1             | μs   |

| AVD    | Large Signal Voltage Gain  |                                                        | 87            | dB   |