# N+1 and ORing Power Rail Controller

## **FEATURES**

- Control External FET for N+1 and ORing

- Wide Supply Voltage Range of 3 V to 16.5 V

- Controls Buses From 0.8 V to 16.5 V

- Linear or On/Off Control Method

- Internal Charge Pump for N-Channel MOSFET

- Rapid Device Turnoff Protects Bus Integrity

- Positive Gate Control on Hot Insertion

- Soft Turn on Reduces Bus Transients

- Industrial Temperature Range: –40°C to 85°C

- 8-Pin TSSOP and SOIC Packages

### **APPLICATIONS**

- N+1 Power Supplies

- Server Blades

- Telecom Systems

- High Availability Systems

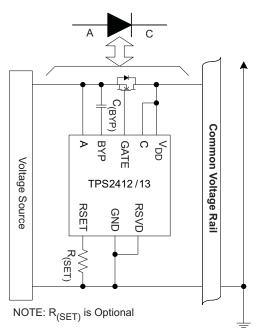

Figure 1. Typical Application

# DESCRIPTION

The TPS2412/13 controller, in conjunction with an external N-channel MOSFET, emulates the function of a low forward voltage diode. The TPS2412/13 can be used to combine multiple power supplies to a common bus in an N+1 configuration, or to combine redundant input power buses. The TPS2412 provides a linear turn-on control while the TPS2413 has an on/off control method.

Applications for the TPS2412/13 include a wide range of systems including servers and telecom. These applications often have either N+1 redundant power supplies, redundant power buses, or both. Redundant power sources must have the equivalent of a diode OR to prevent reverse current during faults and hotplug. A TPS2412/13 and N-channel MOSFET provide this function with less power loss than a schottky diode.

Accurate voltage sensing and a programmable turn-off threshold allows operation to be tailored for a wide range of implementations and bus characteristics. The TPS2412/13 are lower pin count, reduced feature versions of the TPS2410/11.

|                               |              | -            |              |              |

|-------------------------------|--------------|--------------|--------------|--------------|

|                               | TPS2410      | TPS2411      | TPS2412      | TPS2413      |

| Linear gate control           | $\checkmark$ |              | $\checkmark$ |              |

| ON/OFF gate<br>control        |              | $\checkmark$ |              | $\checkmark$ |

| Adjustable turn-off threshold | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Fast comparator filtering     | $\checkmark$ | $\checkmark$ |              |              |

| Voltage monitoring            | $\checkmark$ | $\checkmark$ |              |              |

| Enable control                | $\checkmark$ | $\checkmark$ |              |              |

| Mosfet fault monitoring       | √            | $\checkmark$ |              |              |

| Status pin                    | $\checkmark$ | $\checkmark$ |              |              |

#### Table 1. Family Features

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# TPS2412 TPS2413

1 Kon

SLVS728B-JANUARY 2007-REVISED SEPTEMBER 2008

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| DEVICE  | TEMPERATURE  | PACKAGE <sup>(1)</sup> | MOSFET GATE<br>CONTROL | MARKING |

|---------|--------------|------------------------|------------------------|---------|

| TPS2412 | 40°C to 85°C | PW (TSSOP-8)           | LINEAR                 | TPS2412 |

| 1952412 |              | D (SO-8)               | LINEAR                 | TPS2412 |

| TPS2413 |              | PW (TSSOP-8)           |                        | TPS2413 |

|         |              | D (SO-8)               | ON/OFF                 | TPS2413 |

#### **PRODUCT INFORMATION**<sup>(1)</sup>

(1) For package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range, voltage are referenced to GND (unless otherwise noted)

|     |                                       | VALUE              | UNIT |

|-----|---------------------------------------|--------------------|------|

|     | A, C, FLTR, V <sub>DD</sub> , voltage | -0.3 to 18         | V    |

|     | A above C voltage                     | 7.5                | V    |

|     | C above A voltage                     | 18                 | V    |

|     | GATE <sup>(2)</sup> , BYP voltage     | -0.3 to 30         | V    |

|     | BYP to A voltage                      | -0.3 to 13         | V    |

|     | GATE above BYP <sup>(2)</sup> voltage | 0.3                | V    |

|     | RSET <sup>(2)</sup> voltage           | –0.3 to 7          | V    |

|     | GATE short to A or C or GND           | Indefinite         |      |

| ESD | Human body model                      | 2                  | kV   |

| E2D | Charged device model                  | 500                | V    |

| TJ  | Maximum junction temperature          | Internally limited | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Voltage should not be applied to these pins.

### **DISSIPATION RATINGS**

| PACKAGE    | θ <sub>JA</sub> – Low k °C/W | θ <sub>JA</sub> – High k °C/W | POWER RATING<br>High k<br>T <sub>A</sub> = 85°C (mW) |  |  |

|------------|------------------------------|-------------------------------|------------------------------------------------------|--|--|

| PW (TSSOP) | 258                          | 159                           | 250                                                  |  |  |

| D (SO)     | 176                          | 97.5                          | 410                                                  |  |  |

#### **RECOMMENDED OPERATING CONDITIONS**

voltages are referenced to GND (unless otherwise noted)

|                     |                                      |                           |  | MIN | NOM  | MAX  | UNIT |  |

|---------------------|--------------------------------------|---------------------------|--|-----|------|------|------|--|

| A, C                | Input voltogo rongo TDC2442          | $V_{DD} = V_{j}^{(1)}$    |  | 3   |      | 16.5 | V    |  |

|                     | Input voltage range TPS2412          | $3 \le V_{DD} \le 16.5 V$ |  | 0.8 |      | 16.5 | V    |  |

| A to C              | Operational voltage                  |                           |  |     |      | 5    | V    |  |

| R <sub>(RSET)</sub> | Resistance range <sup>(2)</sup>      |                           |  | 1.5 |      | ∞    | kΩ   |  |

| C <sub>(BYP)</sub>  | Capacitance Range <sup>(2) (3)</sup> |                           |  | 800 | 2200 | 10k  | pF   |  |

| TJ                  | Operating junction temperature       |                           |  | -40 |      | 125  | °C   |  |

| T <sub>A</sub>      | Operating free-air temperature       |                           |  | -40 |      | 85   | °C   |  |

$V_{\text{DD}}$  must exceed 3 V to meet gate drive specification (1)

Voltage should not be applied to these pins. (2)

Capacitors should be X7R, 20% or better (3)

# ELECTRICAL CHARACTERISTICS<sup>(1)(2)</sup> (3) (4) (5) (6)

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                           | MIN  | TYP    | MAX  | UNIT |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|

| V <sub>(A)</sub> , V <sub>(C)</sub> , V <sub>DD</sub> |                                                                                                                                                                                           |      |        |      |      |

| V 1040                                                | V <sub>DD</sub> rising                                                                                                                                                                    | 2.25 |        | 2.5  | V    |

| V <sub>DD</sub> UVLO                                  | Hysteresis                                                                                                                                                                                |      | 0.25   |      | v    |

| A current                                             | I <sub>(A)</sub>  , Gate in active region                                                                                                                                                 |      | 0.66   | 1    |      |

| A current                                             | I <sub>(A)</sub>  , Gate saturated high                                                                                                                                                   |      | 0.1    |      | mA   |

| C current                                             | $  I_{(C)}  , V_{(AC)} \le 0.1 \text{ V}$                                                                                                                                                 |      |        | 10   | μA   |

| V ourroot                                             | Worst case, gate in active region                                                                                                                                                         |      | 4.25   | 6    |      |

| V <sub>DD</sub> current                               | Gate saturated high                                                                                                                                                                       |      | 1.2    |      | mA   |

| TURN ON                                               |                                                                                                                                                                                           |      |        |      |      |

| TPS2412 forward turn-on and regulation voltage        |                                                                                                                                                                                           | 7    | 10     | 13   | mV   |

| TPS2412 forward turn-on / turn-off difference         | R <sub>(RSET)</sub> = open                                                                                                                                                                |      | 7      |      | mV   |

| TPS2413 forward turn-on voltage                       |                                                                                                                                                                                           | 7    | 10     | 13   | mV   |

| TURN OFF                                              |                                                                                                                                                                                           |      |        |      |      |

|                                                       | Gate sinks > 10 mA at $V_{(GATE-A)} = 2 V$                                                                                                                                                | 1    | 3      | F    |      |

|                                                       | V <sub>(A-C)</sub> falling, R <sub>(RSET)</sub> = open                                                                                                                                    | 1    | 3      | 5    | mV   |

| Fast turn-off threshold voltage                       | $V_{(A-C)}$ falling, $R_{(RSET)} = 28.7 \text{ k}\Omega$                                                                                                                                  | -17  | -13.25 | -10  | mv   |

|                                                       | $V_{(A-C)}$ falling, $R_{(RSET)} = 3.24 \text{ k}\Omega$                                                                                                                                  | -170 | -142   | -114 |      |

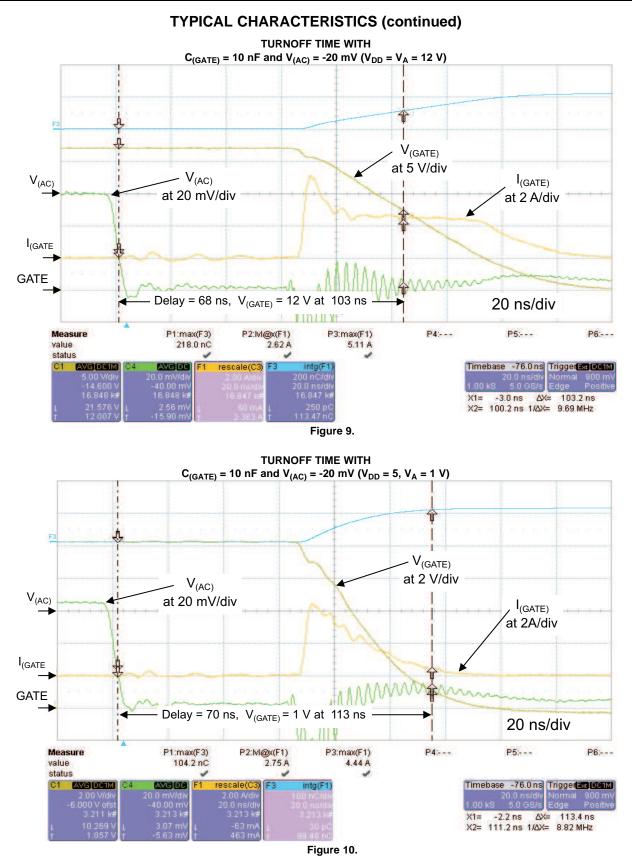

| Turn-off delay                                        | $ \begin{array}{l} V_{(A)} = 12 \ V, \ V_{(A-C)} : 20 \ mV \rightarrow  -20 \ mV, \\ V_{(GATE-A)} \ begins \ to \ decrease \end{array} $                                                  |      | 70     |      | ns   |

| Turn-off time                                         | $ \begin{array}{l} V_{(A)} = 12 \ V, \ C_{(GATE-GND)} = 0.01 \ \mu F, \ V_{(A-C)}: \\ 20 \ mV \rightarrow \ -20 \ mV, \ measure \ the \ period \ to \\ V_{(GATE)} = V_{(A)} \end{array} $ |      | 130    |      | ns   |

| GATE                                                  |                                                                                                                                                                                           |      |        |      |      |

| Gate positive drive voltage, V <sub>(GATE-A)</sub>    | $V_{DD} = 3 \text{ V}, V_{(A-C)} = 20 \text{ mV}$                                                                                                                                         | 6    | 7      | 8    | V    |

| Cale positive unive voltage, v(GATE-A)                | $5 \text{ V} \le \text{V}_{\text{DD}} \le 18 \text{ V}, \text{ V}_{(\text{A-C})} = 20 \text{ mV}$                                                                                         | 9    | 10.2   | 11.5 | v    |

| Gate source current                                   | $V_{(A-C)} = 50 \text{ mV}, V_{(GATE-A)} = 4 \text{ V}$                                                                                                                                   | 250  | 290    | 350  | μΑ   |

| Soft turn-off sink current (TPS2412)                  | $V_{(A-C)} = 4 \text{ mV}, V_{(GATE-A)} = 2 \text{ V}$                                                                                                                                    | 2    | 5      |      | mA   |

$[3 \ V \le V_{(A)} \le 18 \ V \text{ and } V_{(C)} = V_{DD}] \text{ or } [0.8 \ V \le V_{(A)} \le 3 \ V \text{ and } 3 \ V \le V_{DD} \le 18 \ V] \\ C_{(BYP)} = 2200 \ pF, \ R_{(RSET)} = \text{open} \\ -40^{\circ}C \le T_J \le 125^{\circ}C$ (1)

- (2)

- (3)

- Positive currents are into pins (4)

- (5)Typical values are at 25°C

- (6) All voltages are with respect to GND.

Copyright © 2007-2008, Texas Instruments Incorporated

Submit Documentation Feedback

SLVS728B-JANUARY 2007-REVISED SEPTEMBER 2008

www.ti.com

# ELECTRICAL CHARACTERISTICS (continued)

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                  | TEST CONDITIONS                                                                                                                                         | MIN  | TYP  | MAX | UNIT |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|------|

| East turn-off pulsed current lighter       | $V_{(A-C)} = -0.1 V$                                                                                                                                    |      |      |     |      |

| Fact turn off nulacid current              | $V_{(GATE)} = 8 V$                                                                                                                                      | 1.75 | 2.35 |     | А    |

| Fast turn-off pulsed current, $I_{(GATE)}$ | $V_{(GATE)} = 5 V$                                                                                                                                      | 1.25 | 1.75 |     |      |

|                                            | Period                                                                                                                                                  | 7.5  | 12.5 |     | μs   |

| Sustain turn-off current, I(GATE)          | $ \begin{array}{l} V_{(A-C)} = -0.1 \ V, \ V_{(C)} \leq V_{DD}, \ 3 \ V \leq V_{DD} & \leq 18 \ V, \\ 2 \ V \leq V_{(GATE)} & \leq 18 \ V \end{array} $ | 15   | 19.5 |     | mA   |

| MISCELLANEOUS                              |                                                                                                                                                         |      |      |     |      |

| Thermal shutdown temperature               | Temperature rising, T <sub>J</sub>                                                                                                                      |      | 135  |     | °C   |

| Thermal hysteresis                         |                                                                                                                                                         |      | 10   |     | °C   |

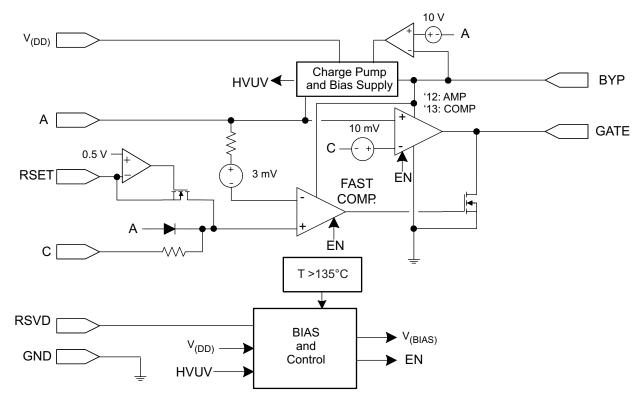

### FUNCTIONAL BLOCK DIAGRAM

4

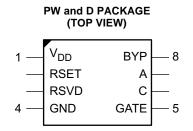

#### **TERMINAL FUNCTIONS**

| TERMINAL        |     | 1/0 | DESCRIPTION                                                                                                                                                                                       |

|-----------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                       |

| V <sub>DD</sub> | 1   | PWR | Input power for the gate drive charge pump and internal controls. $V_{DD}$ must be connected to a supply voltage $\ge 3 \text{ V}$ .                                                              |

| RSET            | 2   | I   | Connect a resistor to ground to program the turn-off threshold. Leaving RSET open results in a slightly positive $V_{(A-C)}$ turn-off threshold.                                                  |

| RSVD            | 3   | PWR | This pin must be connected to GND.                                                                                                                                                                |

| GND             | 4   | PWR | Device ground.                                                                                                                                                                                    |

| GATE            | 5   | 0   | Connect to the gate of the external MOSFET. Controls the MOSFET to emulate a low forward-voltage diode.                                                                                           |

| С               | 6   | I   | Voltage sense input that connects to the simulated diode cathode. Connect to the MOSFET drain in the typical configuration.                                                                       |

| А               | 7   | I   | Voltage sense input that connects to the simulated diode anode. A also serves as the reference for the charge-pump bias supply on BYP. Connect to the MOSFET source in the typical configuration. |

| BYP             | 8   | I/O | Connect a storage capacitor from BYP to A to filter the gate drive supply voltage.                                                                                                                |

5

TPS2412 TPS2413 SLVS728B-JANUARY 2007-REVISED SEPTEMBER 2008

www.ti.com

### DETAILED DESCRIPTION

The following descriptions refer to the pinout and the functional block diagram.

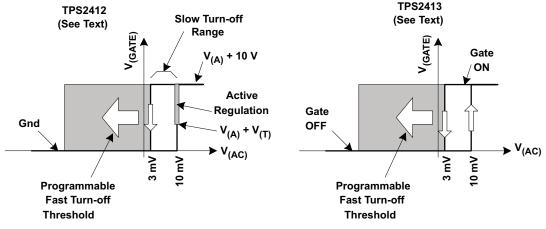

**A**, **C**: The A pin serves as the simulated diode anode and the C as the cathode. GATE is driven high when  $V_{(AC)}$  exceeds 10 mV. Both devices provide a strong GATE pull-down when  $V_{(AC)}$  is less than the programmable fast turn-off threshold. The TPS2412 has a soft pull-down when  $V_{(AC)}$  is less than 10 mV but above the fast turn-off threshold.

Several internal comparator and amplifier circuits monitor these two pins. The inputs are protected from excess differential voltage by a clamp diode and series resistance. If C falls below A by more than about 0.7 V, a small current flows out of C. Protect the internal circuits with an external clamp if C can be more than 6 V lower than A.

The internal charge pump output, which provides bias power to the comparators and voltage to drive GATE, is referenced to A. Some charge pump current appears on A due to this topology. The A and C pins should be Kelvin connected to the MOSFET source and drain. A and C connections should also be short and low impedance, with special attention to the A connection. Residual noise from the charge pump can be reduced with a bypass capacitor at A if the application permits.

**BYP:** BYP is the internal charge pump output, and the positive supply voltage for internal comparator circuits and GATE driver. A capacitor must be connected from BYP to A. While the capacitor value is not critical, a 2200-pF ceramic is recommended. Traces to this part must be kept short and low impedance to provide adequate filtering. Shorting this pin to a voltage below A damages the TPS2412/13.

**GATE:** Gate controls the external N channel MOSFET gate. GATE is driven positive with respect to A by a driver operating from the voltage on BYP. A time-limited high current discharge source pulls GATE to GND when the fast turn-off comparator is activated. The high-current discharge is followed by a sustaining pull-down. The turn-off circuits are disabled by the thermal shutdown, leaving a resistive pull-down to keep the gate from floating. The gate connection should be kept low impedance to maximize turn-off current.

**GND:** This is the input supply reference. GND should have a low impedance connection to the ground plane. It carries several Amperes of rapid-rising discharge current when the external MOSFET is turned off, and also carries significant charge pump currents.

**RSET:** A resistor connected from this pin to GND sets the fast  $V_{(A-C)}$  comparator turn-off threshold. The threshold is slightly positive when the RSET pin is left open. Current drawn by the resistor programs the turn-off voltage to increasing negative values. The TPS2413 must have a negative threshold programmed to avoid an unstable condition at light load. The expression for  $R_{(RSET)}$  in terms of the trip voltage,  $V_{(OFF)}$ , follows.

$$\mathsf{R}(\mathsf{RSET}) = \left(\frac{-470.02}{\mathsf{V}(\mathsf{OFF}) - 0.00314}\right) \tag{1}$$

The units of the numerator are (V × V/A).  $V_{(OFF)}$  is positive for  $V_{(A)}$  greater than  $V_{)}$ ,  $V_{(OFF)}$  is less than 3 mV, and  $R_{(RSET)}$  is in ohms.

**RSVD:** Connect to ground.

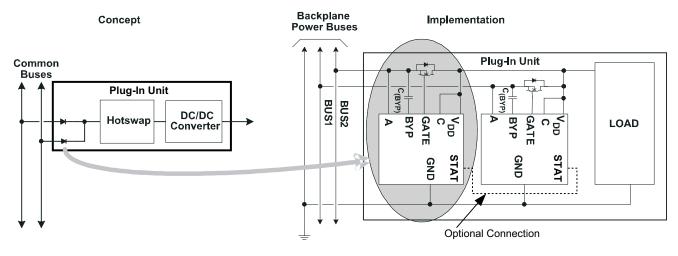

$V_{DD}$ :  $V_{DD}$  is the primary supply for the gate drive charge pump and other internal circuits. This pin must be connected a source that is 3 V or greater when the external MOSFET is to be turned on.  $V_{DD}$  may be greater or lower than the controlled bus voltage.

A 0.01- $\mu$ F bypass capacitor, or 10- $\Omega$  and a 0.01- $\mu$ F filter, is recommended because charge pump currents are drawn through V<sub>DD</sub>.

TPS2412 TPS2413 SLVS728B-JANUARY 2007-REVISED SEPTEMBER 2008

#### www.ti.com

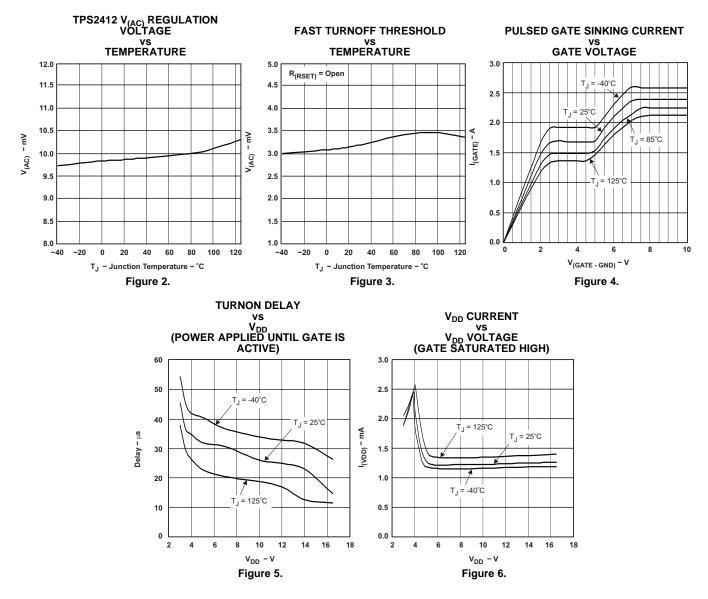

#### **TYPICAL CHARACTERISTICS**

7

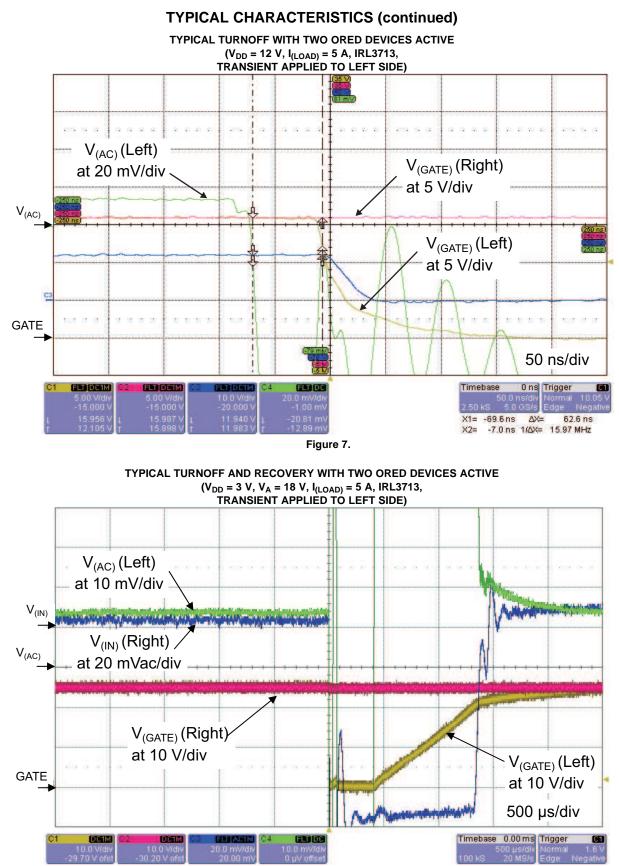

Figure 8.

Copyright © 2007–2008, Texas Instruments Incorporated

Copyright © 2007–2008, Texas Instruments Incorporated

# **APPLICATION INFORMATION**

#### **OVERVIEW**

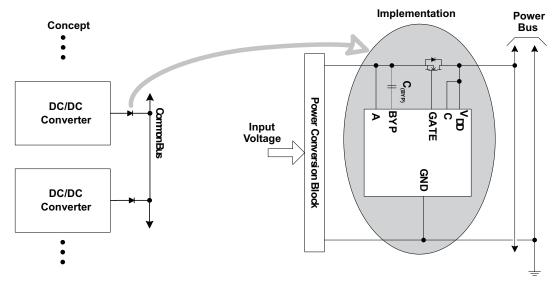

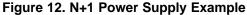

The TPS2412/13 is designed to allow an output ORing in N+1 power supply applications (see Figure 12), and an input-power bus ORing in redundant source applications (see Figure 13). The TPS2412/13 and external MOSFET emulate a discrete diode to perform this unidirectional power combining function. The advantage to this emulation is lower forward voltage drop and the ability to tune the operation.

The TPS2412 turns the MOSFET on with a linear control loop that regulates  $V_{(AC)}$  to 10 mV as shown in Figure 11. With the gate low, and  $V_{(AC)}$  increasing to 10 mV, the amplifier drives GATE high with all available output current until regulation is reached. The regulator controls  $V_{(GATE)}$  to maintain  $V_{(AC)}$  at 10 mV as long as the MOSFET  $r_{DS(on)} \times I_{(DRAIN)}$  is less than this the regulated voltage. The regulator drives GATE high, turning the MOSFET fully ON when the  $r_{DS(on)} \times I_{(DRAIN)}$  exceeds 10 mV; otherwise,  $V_{(GATE)}$  will be near  $V_{(A)}$  plus the MOSFET gate threshold voltage. If the external circuits force  $V_{(AC)}$  below 10 mV and above the programmed fast turnoff, GATE is slowly turned off. GATE is rapidly pulled to ground if  $V_{(AC)}$  falls to the RSET programmed fast turn-off threshold.

The TPS2413 turns the MOSFET on and off like a comparator with hysteresis as shown in Figure 11. GATE is driven high when  $V_{(AC)}$  exceeds 10 mV, and rapidly turned off if  $V_{(AC)}$  falls to the RSET programmed fast turn-off threshold.

System designs should account for the inherent delay between a TPS2412/13 circuit becoming forward biased, and the MOSFET actually turning ON. The delay is the result of the MOSFET gate capacitance charge from ground to its threshold voltage by the 290  $\mu$ A gate current. If there are no additional sources holding the ORed rail voltage up, the MOSFET internal diode will conduct and maintain voltage on the ORed output, but there will be some voltage droop. This condition is analogous to the power source being ORed in this case. The DC/DC converter output voltage droops when its load increases from zero to a high value. Load sharing techniques that keep all ORed sources active solve this condition.

Figure 11. TPS2412/13 Operation

The operation of the two parts is summarized in Table 2.

| Table 2. | Operation | as a | Function | of V <sub>AC</sub> |

|----------|-----------|------|----------|--------------------|

|----------|-----------|------|----------|--------------------|

|         |                                                      | Turnoff Thres                    |                                                              |                           |

|---------|------------------------------------------------------|----------------------------------|--------------------------------------------------------------|---------------------------|

|         | V <sub>(AC)</sub> ≤ Turnoff Threshold <sup>(1)</sup> | V <sub>(AC)</sub> Forced < 10 mV | (MOSFET<br>r <sub>DS(on)</sub> × I <sub>LOAD</sub> ) ≤ 10 mV | V <sub>(AC)</sub> > 10 mV |

| TPS2412 | Strong GATE pull-down (OFF)                          | Weak GATE pull-down<br>(OFF)     | $V_{(AC)}$ regulated to 10 mV                                | GATE pulled high (ON)     |

| TPS2413 | Strong GATE pull-down (OFF)                          | Depends on previous state (H     | GATE pulled high (ON)                                        |                           |

(1) Turnoff threshold is established by the value of RSET.

#### TPS2412 vs TPS2413 – MOSFET CONTROL METHODS

The TPS2412 control method yields several benefits. First, the low-current GATE driver provides a gentle turn-on and turn-off for slowly rising and falling input voltage. Second, it reduces the tendency for on/off cycling of a comparator based solution at light loads. Third, it avoids reverse currents if the fast turn-off threshold is left positive. The drawback to this method is that the MOSFET appears to have a high resistance at light load when the regulation is active. A momentary output voltage droop occurs when a large step load is applied from a light-load condition. The TPS2412 is a better solution for a mid-rail bus that is re-regulated.

The TPS2413 turns the MOSFET on if  $V_{(AC)}$  is greater than 10 mV, and the rapid turn-off is activated at the programmed negative threshold. There is no linear control range and slow turn-off. The disadvantage is that the turn-off threshold must be negative (unless a minimum load is always present) permitting a continuous reverse current. Under a dynamic reverse voltage fault, the lower threshold voltage may permit a higher peak reverse current. There are a number of advantages to this control method. Step loads from a light load condition are handled without a voltage droop beyond I × R. If the redundant converter fails, applications with redundant synchronous converters may permit a small amount of reverse current at light load in order to assure that the MOSFET is all ready on. The TPS2413 is a better solution for low-voltage buses that are not re-regulated, and that may see large load steps transients.

These applications recommendations are meant as a starting point, with the needs of specific implementations over-riding them.

#### N+1 POWER SUPPLY – TYPICAL CONNECTION

The N+1 power supply configuration shown in Figure 12 is used where multiple power supplies are paralleled for either higher capacity, redundancy or both. If it takes N supplies to power the load, adding an extra, identical unit in parallel permits the load to continue operation in the event that any one of the N supplies fails. The supplies are ORed together, rather than directly connected to the bus, to isolate the converter output from the bus when it is plugged-in or fails short. The TPS2412/13 with an external MOSFET emulates the function of the ORing diode.

It is possible for a malfunctioning converter in an ORed topology to create a bus overvoltage if the loading is less than the converter's capacity (e.g. N = 1). The ORed topology shown cannot protect the bus from this condition, even if the ORing MOSFET can be turned off. One common solution is to use two MOSFETs in a back-to-back configuration to provide bidirectional blocking. The TPS2412/13 does not have a provision for forcing the gate off when the overvoltage condition occurs, use of the TPS2410/11 is recommended.

ORed supplies are usually designed to share power by various means, although the desired operation could implement an active and standby concept. Sharing approaches include both passive, or voltage droop, and active methods. Not all of the output ORing devices may be ON depending on the sharing control method, bus loading, distribution resistances, and TPS2412/13 settings.

SLVS728B-JANUARY 2007-REVISED SEPTEMBER 2008

#### **INPUT ORing – TYPICAL CONNECTION**

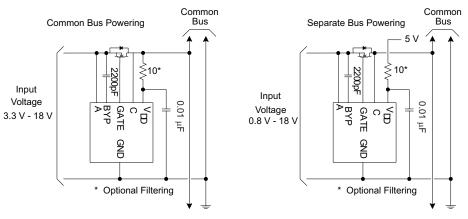

Figure 13 shows how redundant buses may be ORed to a common point to achieve higher reliability. It is possible to have both MOSFETs ON at once if the bus voltages are matched, or the combination of tolerance and regulation causes both TPS2412/13 circuits to see a forward voltage. The ORing MOSFET disconnects the lower-voltage bus, protecting the remaining bus from potential overload by a fault.

Figure 13. Example ORing of Input Power Buses

#### SYSTEM DESIGN AND BEHAVIOR WITH TRANSIENTS

The power system, perhaps consisting of multiple supplies, interconnections, and loads, is unique for every product. A power distribution has low impedance, and low loss, which yields high Q by its nature. While the addition of lossy capacitors helps at low frequencies, their benefit at high frequencies is compromised by parasitics. Transient events with rise times in the 10 ns range may be caused by inserting or removing units, load fluctuations, switched loads, supply fluctuations, power supply ripple, and shorts. These transients cause the distribution to ring, creating a situation where ORing controllers may trip off unnecessarily. In particular, when an ORing device turns off due to a reverse current fault, there is an abrupt interruption of the current, causing a fast ringing event. Since this ringing occurs at the same point in the topology as the other ORing controllers, they are the most likely to be effected.

The ability to operate in the presence of noise and transients is in direct conflict with the goal of precise ORing with rapid response to actual faults. A fast response reduces peak stress on devices, reduces transients, and promotes un-interrupted system operation. However, a control with small thresholds and high speed is most likely to be falsely tripped by transients that are not the result of a fault. The power distribution system should be designed to control the transient voltages seen by fast-responding devices such as ORing and hotswap devices.

While some applications may find it possible to use RSET to avoid false tripping, the TPS2410/11 provides features beyond the TPS2412/13 including fast-comparator input filtering and STAT to dynamically shift the turn-off threshold.

#### **RECOMMENDED OPERATING RANGE**

The maximum recommended bus voltage is lower than the absolute maximum voltage ratings on A, C, and  $V_{DD}$  solely to provide some margin for transients on the bus. Most power systems experience transient voltages above the normal operating level. Short transients, or voltage spikes, may be clamped by the ORing MOSFET to an output capacitor and/or voltage rail depending on the system design. Transient protection, e.g. a TVS diode (transient voltage suppressor, a type of Zener diode), may be required on the input or output if the system design does not inherently limit transient voltages below the TPS2412/13 absolute maximum ratings. If a TVS is required, it must protect to the absolute maximum ratings at the worst case clamping current. The TPS2412/13 will operate properly up to the absolute maximum voltage ratings on A, C, and  $V_{DD}$ .

### TPS2412 REGULATION-LOOP STABILITY

The TPS2412 uses an internal linear error amplifier to keep the external MOSFET from saturating at light load. This feature has the benefits of setting a turn-off above 0 V, providing a soft turn-off for slowly decaying input voltages, and helps droop-sharing redundancy at light load.

Although the control loop has been designed to accommodate a wide range of applications, there are a few guidelines to be followed to assure stability.

- Select a MOSFET C<sub>(ISS)</sub> of 1 nF or greater

- Use low ESR bulk capacitors on the output C terminal, typically greater than 100 $\mu F$  with less than 50 m $\Omega$  ESR

- Maintain some minimum operational load (e.g. 10 mA or more)

Symptoms of stability issues include  $V_{(AC)}$  undershoot and possible fast turn-off on large-transient recovery, and a worst-case situation where the gate continually cycles on and off. These conditions are solved by following the rules above. Loop stability should not be confused with tripping the fast comparator due to  $V_{(AC)}$  tripping the gate off.

Although not common, a condition may arise where the dc/dc converter transient response may cause the GATE to cycle on and off at light load. The converter experiences a load spike when GATE transitions from OFF to ON because the ORed bus capacitor voltage charges abruptly by as much as a diode drop. The load spike may cause the supply output to droop and overshoot, which can result in the ORed capacitor peak charging to the overshoot voltage. When the supply output settles to its regulated value, the ORed bus may be higher than the source, causing the TPS2412/13 to turn the GATE off. While this may not actually cause a problem, its occurrence may be mitigated by control of the power supply transient characteristic and increasing its output capacitance while increasing the ORed load to capacitance ratio. Adjusting the TPS2412/13 turn-off threshold to desensitize the redundant ORing device may help as well. Careful attention to layout and charge-pump noise around the TPS2412/13 helps with noise margin.

The linear gate driver has a pull-up current of 290 µA and pull-down current of 3 mA typical.

### MOSFET SELECTION AND R(RSET)

MOSFET selection criteria include voltage rating, voltage drop, power dissipation, size, and cost. The voltage rating consists of both the ability to withstand the rail voltage with expected transients, and the gate breakdown voltage. The MOSFET gate rating should be the minimum of 12 V, or the controlled rail voltage. Typically this requires a ±20-V GATE voltage rating.

While  $r_{DS(on)}$  is often chosen with the power dissipation, voltage drop, size and cost in mind, there are several other factors to be concerned with in ORing applications. When using the TPS2412, the minimum voltage across the device is 10 mV. A device that would have a lower voltage drop at full-load would be overspecified. When using a TPS2413 or TPS2412 with RSET programmed to a negative voltage, the permitted static reverse current is equal to the turn-off threshold divided by the  $r_{DS(on)}$ . While this current may actually be desirable in some systems, the amount may be controlled by selection of  $r_{DS(on)}$  and RSET. The practical range of  $r_{DS(on)}$  for a single MOSFET runs from the low milliohms to 40 m $\Omega$  for a single MOSFET.

MOSFETs may be paralleled for lower voltage drop (power loss) at high current. For TPS2412 operation, one should plan for only one of the MOSFETs to carry current until the 10 mV regulation point is exceeded and the loop forces GATE fully ON. TPS2413 operation does not rely on linear range operation, so the MOSFETs are all ON or OFF together except for short transitional times. Beyond the control issues, current sharing depends on the resistance match including both the  $r_{DS(on)}$  and the connection resistance.

The TPS2412 may be used without a resistor on RSET. In this case, the turnoff  $V_{(AC)}$  threshold is about 3 mV. The TPS2413 may only be operated without an RSET programming resistor if the loading provides a higher  $V_{(AC)}$ . A larger negative turnoff threshold reduces sensitivity to false tripping due to noise on the bus, but permits larger static reverse current. Installing a resistor from RSET to ground creates a negative shift in the fast turn-off threshold per Equation 2.

$R_{(RSET)} = \left(\frac{-470.02}{V_{(OFF)} - 0.00314}\right)$

(2)

(3)

To obtain a -10 mV fast turnoff (  $V_{(A)}$  is less than  $V_{(C)}$  by 10 mV ),  $R_{(RSET)} = (-470.02/(-0.01-0.00314)) \approx 35,700\Omega$ . If a 10 m $\Omega$  r<sub>DS(on)</sub> MOSFET was used, the reverse turnoff current would be calculated as follows.

$$I_{(TURN_OFF)} = \frac{V_{(THRESHOLD)}}{r_{DS(on)}}$$

$$I_{(TURN_OFF)} = \frac{-10 \text{ mV}}{10 \text{ m}\Omega}$$

$$I_{(TURN_OFF)} = -1 \text{ A}$$

The sign indicates that the current is reverse, or flows from the MOSFET drain to source (C to A).

The turn-off speed of a MOSFET is influenced by the effective gate-source and gate-drain capacitance <sub>ISS</sub>). Since these capacitances vary a great deal between different vendor parts and technologies, they should be considered when selecting a MOSFET where the fastest turn-off is desired.

### GATE DRIVE, CHARGE PUMP AND C(BYP)

Gate drive of 270  $\mu$ A typical is generated by an internal charge pump and current limiter. A separate supply, V<sub>DD</sub>, is provided to avoid having the large charge pump currents interfere with voltage sensing by the A and C pins. The GATE drive voltage is referenced to V<sub>(A)</sub> as GATE will only be driven high when V<sub>(A)</sub> > V<sub>)</sub>. The recommended capacitor on BYP (bypass) must be used in order to form a quiet supply for the internal high-speed comparator. V<sub>(GATE)</sub> must not exceed V<sub>(BYP)</sub>.

#### V<sub>DD</sub>, BYP, and POWERING OPTIONS

The separate  $V_{DD}$  pin provides flexibility for operational power and controlled rail voltage. While the internal UVLO has been set to 2.5 V, the TPS2412/13 requires at least 3 V to generate the specified GATE drive voltage. Sufficient BYP voltage to run internal circuits occurs at  $V_{DD}$  voltages between 2.5 V and 3 V. There are three choices for power, A, C, or a separate supply, two of which are demonstrated in Figure 14. One choice for voltage rails over 3.3 V is to power from C, since it is typically the source of reliable power. Voltage rails below 3.3 V nominal, e.g. 2.5 V and below, should use a separate supply such as 5 V. A separate  $V_{DD}$  supply can be used to control voltages above it, for example 5 V powering  $V_{DD}$  to control a 12-V bus.

$V_{DD}$  is the main source of power for the internal control circuits. The charge pump that powers BYP draws most of its power from  $V_{DD}$ . The input should be low impedance, making a bypass capacitor a preferred solution. A 10- $\Omega$  series resistor may be used to limit inrush current into the bypass capacitor, and to provide noise filtering for the supply.

BYP is the interconnection point between a charge pump,  $V_{(AC)}$  monitor amplifiers and comparators, and the gate driver.  $C_{(BYP)}$  must be used to filter the charge pump. A 2200 pF is recommended, but the value is not critical.

Figure 14. V<sub>DD</sub> Powering Examples

#### **ORing Examples**

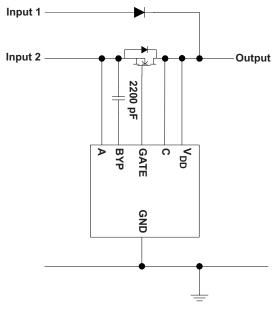

Applications with the TPS2412/13 are not limited to ORing of identical sections. The TPS2412/13 and external MOSFET form a general purpose function block. Figure 15 shows a circuit with ORing between a discrete diode and a TPS2412/MOSFET section. This circuit can be used to combine two different voltages in cases where the output is regulated, and the additional voltage drop in the Input 1 path is not a concern. An example is ORing of an ac adapter on Input 1 with a lower voltage on Input 2.

Figure 15. ORing Circuit

The TPS2412 may be a better choice in applications where inputs may be removed, causing an open-circuit input. If the MOSFET was ON when the input is removed,  $V_{AC}$  will be virtually zero. If the reverse turn-off threshold is programmed negative, the TPS2412/13 will not pull GATE low. A system interruption could then be created if a short is applied to the floating input. For example, if an ac adapter is first connected to the unit, and then connected to the ac mains, the adapter's output capacitors will look like a momentary short to the unit. A TPS2412 with RSET open will turn the MOSFET OFF when the input goes open circuit.

## SUMMARIZED DESIGN PROCEDURE

The following is a summarized design procedure:

- 1. Choose between the TPS2412 or 2413, see TPS2412 vs TPS2413 MOSFET Control Methods

- 2. Choose the V<sub>DD</sub> source. Table 3 provides a guide for where to connect V<sub>DD</sub> that covers most cases. V<sub>DD</sub> may be directly connected to the supply, but an  $R_{(VDD)}$  and  $C_{(VDD)}$  of 10  $\Omega$  and 0.01  $\mu$ F is recommended.

#### Table 3. V<sub>DD</sub> Connection Guide

| V <sub>A</sub> < 3 V | $3 V \leq V_A \leq 3.6 V$                         | V <sub>A</sub> > 3.6 V                                 |

|----------------------|---------------------------------------------------|--------------------------------------------------------|

| Bias Supply > 3 V    | $V_A$ or Bias Supply > 3 V. $V_C$ if always > 3 V | $V_{C}$ , $V_{A}$ , or Bias for special configurations |

- 3. Noise voltage and impedance at the A pin should be kept low.  $C_{(A)}$  may be required if there is noise on the bus, or A is not low impedance. If either of these is a concern, a  $C_{(A)}$  of 0.01  $\mu$ F or more may be required.

- 4. Select C<sub>(BYP)</sub> as 2200 pF, X7R, 25-V or 50-V ceramic capacitor.

- 5. Select the MOSFET based on considerations of voltage drop, power dissipated, voltage ratings, and gate capacitance. See sections: MOSFET Selection and RSET and TPS2412 Regulation-Loop Stability.

- Select R<sub>(RSET)</sub> based on which MOSFET was chosen and reverse current considerations see MOSFET Selection and RSET. If the noise and transient environment is not well known, make provision for R<sub>(RSET)</sub> even when using the TPS2412.

- 7. Make sure to connect RSVD to ground

#### **Layout Considerations**

- 1. The TPS2412/13, MOSFET, and associated components should be used over a ground plane.

- 2. The GND connection should be short, with multiple vias to ground.

- 3.  $C_{(VDD)}$  should be adjacent to the V<sub>DD</sub> pin with a minimal ground connection length to the plane.

- 4. The GATE connection should be short and wide (e.g., 0.025" minimum).

- 5. The C pin should be Kelvin connected to the MOSFET.

- 6. The A pin should be a short, wide, Kelvin connection to the MOSFET.

- 7. R<sub>(SET)</sub> should be kept immediately adjacent to the TPS2412/13 with short leads.

- 8.  $C_{(BYP)}$  should be kept immediately adjacent to the TPS2412/13 with short leads.

24-Jan-2013

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan<br>(2)            | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|---------------|--------------|--------------------|------|-------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

| TPS2412D         | ACTIVE        | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2412D             | Samples |

| TPS2412DG4       | ACTIVE        | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2412D             | Samples |

| TPS2412DR        | ACTIVE        | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2412D             | Samples |

| TPS2412DRG4      | ACTIVE        | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2412D             | Samples |

| TPS2412PW        | ACTIVE        | TSSOP        | PW                 | 8    | 150         | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2412              | Samples |

| TPS2412PWG4      | ACTIVE        | TSSOP        | PW                 | 8    | 150         | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2412              | Samples |

| TPS2412PWR       | ACTIVE        | TSSOP        | PW                 | 8    | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2412              | Samples |

| TPS2412PWRG4     | ACTIVE        | TSSOP        | PW                 | 8    | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2412              | Samples |

| TPS2413D         | ACTIVE        | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2413D             | Samples |

| TPS2413DG4       | ACTIVE        | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2413D             | Samples |

| TPS2413DR        | ACTIVE        | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2413D             | Samples |

| TPS2413DRG4      | ACTIVE        | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2413D             | Samples |

| TPS2413PW        | ACTIVE        | TSSOP        | PW                 | 8    | 150         | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2413              | Samples |

| TPS2413PWG4      | ACTIVE        | TSSOP        | PW                 | 8    | 150         | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2413              | Samples |

| TPS2413PWR       | ACTIVE        | TSSOP        | PW                 | 8    | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2413              | Samples |

| TPS2413PWRG4     | ACTIVE        | TSSOP        | PW                 | 8    | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | 2413              | Samples |

<sup>(1)</sup> The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

24-Jan-2013

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

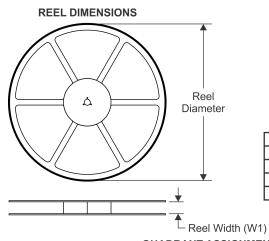

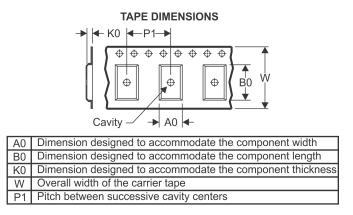

## TAPE AND REEL INFORMATION

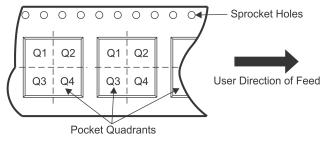

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nomina<br>Device | 1     | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------------------------|-------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS2412DR                            | SOIC  | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2412PWR                           | TSSOP | PW                 | 8 | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

| TPS2413DR                            | SOIC  | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS2413PWR                           | TSSOP | PW                 | 8 | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

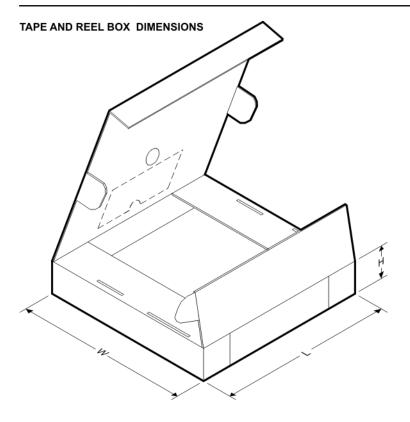

# PACKAGE MATERIALS INFORMATION

26-Jan-2013

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS2412DR  | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| TPS2412PWR | TSSOP        | PW              | 8    | 2000 | 367.0       | 367.0      | 35.0        |

| TPS2413DR  | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| TPS2413PWR | TSSOP        | PW              | 8    | 2000 | 367.0       | 367.0      | 35.0        |

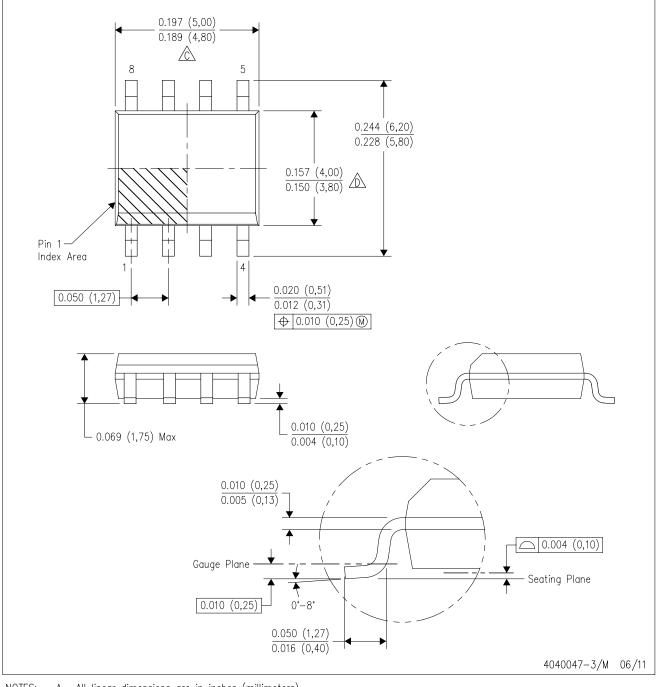

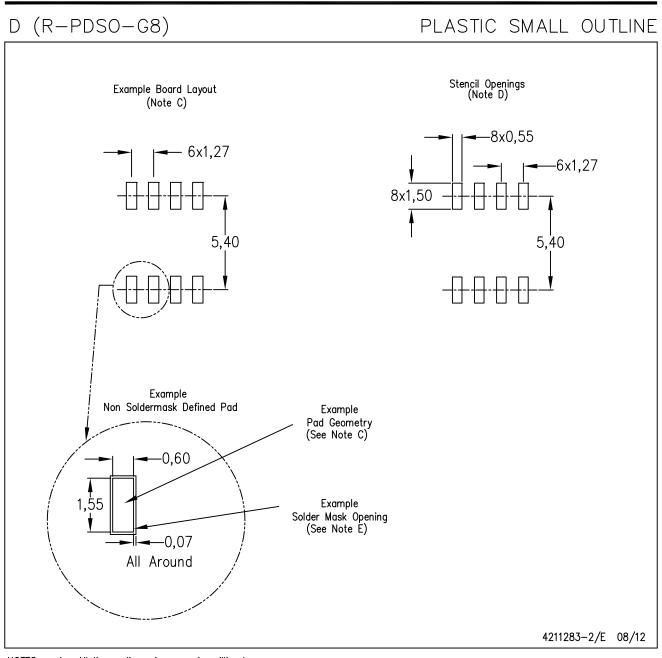

D (R-PDSO-G8)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

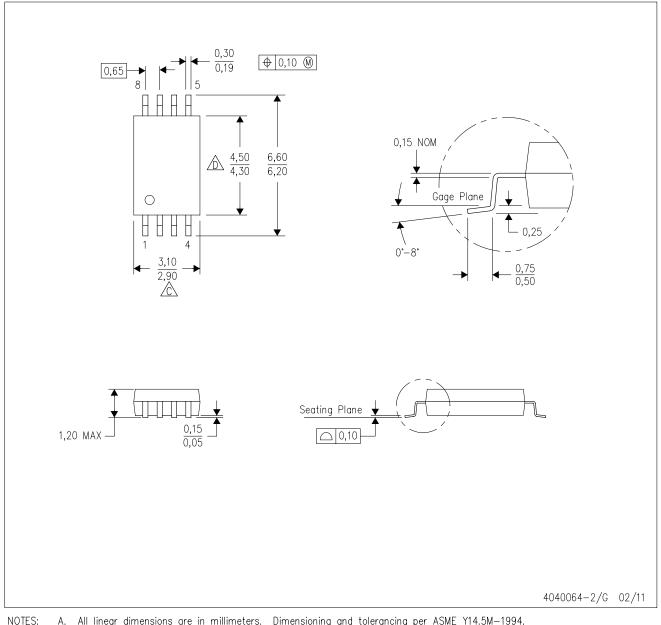

PW (R-PDSO-G8)

PLASTIC SMALL OUTLINE

Α. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994. Ŗ. This drawing is subject to change without notice.

🖄 Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

E. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |  |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|--|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |  |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |  |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |  |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |  |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |  |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |  |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |  |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |  |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |  |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |  |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |  |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |  |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated