# **TAS5036**Six Channel Digital Audio PWM Processor

## Data Manual

#### **Contents**

| Se | ction        |                |                                                        |   |              |                 | Page                                                   |

|----|--------------|----------------|--------------------------------------------------------|---|--------------|-----------------|--------------------------------------------------------|

| 1  | Introdu<br>1 | uction         |                                                        |   | 2.4          | Pulse Wi<br>19  | idth Modulator (PWM)                                   |

|    | 1.1          | Features<br>1  |                                                        |   |              | 2.4.1           | Clipping Indicator                                     |

|    | 1.2          | Functiona<br>2 | ll Block Diagram                                       |   |              | 2.4.2           | Error Recovery                                         |

|    | 1.3          | 3              | Assignments                                            |   |              | 2.4.3           | Individual Channel Error Recovery                      |

|    | 1.4          | 4              | Information                                            |   |              | 2.4.4           | PWM DC-Offset Correction 20                            |

|    | 1.5          | 4              | Functions                                              |   |              | 2.4.5           | Inter-Channel Delay                                    |

| 2  | 6            |                | erview                                                 |   |              | 2.4.6           | ABD Delay20                                            |

|    | 2.1          | 6              | I Serial Data Interface                                |   |              | 2.4.7           | PWM/H-Bridge and Discrete<br>H-Bridge Driver Interface |

|    |              | 2.1.1          | Normal-Speed, Double-Speed, and Quad-Speed Selection 6 |   | 2.5          | I2C Seria       | 21 al Control Interface                                |

|    |              | 2.1.2          | Clock Master/Slave Mode (M_S)                          |   |              | 2.5.1           | Single Byte Write                                      |

|    |              | 2.1.3          | 7 Clock Master Mode                                    |   |              | 2.5.2           | Multiple Byte Write 22                                 |

|    |              | 2.1.4          | 7 Clock Slave Mode                                     |   |              | 2.5.3           | Single Byte Read                                       |

|    |              | 2.1.5          | 8 PLL Filter                                           |   |              | 2.5.4           | Multiple Byte Read 23                                  |

|    |              | 246            | 10<br>DCLK                                             | 3 | Serial<br>24 | Control Ir      | nterface Register Definitions .                        |

|    |              | 2.1.6          | 10                                                     |   | 3.1          | General 25      | Status Register (x00)                                  |

|    | 0.0          | 2.1.7          | Serial Data Interface                                  |   | 3.2          |                 | atus Register (x01)                                    |

|    | 2.2          | 15             | ower Down, and Status                                  |   | 3.3          |                 | Control Register 0 (x02)                               |

|    |              | 2.2.1          | Reset—RESET                                            |   | 3.4          |                 | Control Register 1 (x03)                               |

|    |              | 2.2.2          | Power Down—PDN                                         |   | 3.5          |                 | covery Register (x04)                                  |

|    |              | 2.2.3          | Status Registers                                       |   | 3.6          | Automute<br>26  | e Delay Register (x05)                                 |

|    | 2.3          | 17             | ocessing                                               |   | 3.7          | DC-Offse<br>27  | et Control Registers (x06-x0B) .                       |

|    |              | 2.3.1          | Volume Control                                         |   | 3.8          | Interchar<br>27 | nnel Delay Registers (x0C-x11)                         |

|    |              | 2.3.2          | Mute<br>18                                             |   | 3.9          | ABD Dela<br>27  | ay Register (x12)                                      |

|    |              | 2.3.3          | Auto Mute                                              |   | 3.10         | 27              | l Channel Mute Register (x19) .                        |

|    |              | 2.3.4          | Individual Channel Mute 18                             | 4 | 28           |                 | ation                                                  |

|    |              | 2.3.5          | De-Emphasis Filter                                     | 5 | Specif<br>29 | ications .      |                                                        |

| 5.1       |              | e Maximum Ratings Over Operat-<br>perature Ranges                                                |     | 5.4          | Switchir<br>30        | ng Characteristics                                       |  |  |

|-----------|--------------|--------------------------------------------------------------------------------------------------|-----|--------------|-----------------------|----------------------------------------------------------|--|--|

| 5.2       | Recomr       | mended Operating Conditions (Fs z)                                                               |     |              | 5.4.1                 | Command Sequence Timing . 30                             |  |  |

|           | 29           | ,                                                                                                |     |              | 5.4.2                 | Serial Audio Port                                        |  |  |

| 5.3       |              | al Characteristics Over Recom-                                                                   |     |              |                       | 34                                                       |  |  |

|           | mended<br>29 | Operating Conditions                                                                             |     |              | 5.4.3                 | Serial Control Port—I2C Operation                        |  |  |

|           | 5.3.1        | Static Digital Specifications                                                                    |     |              |                       | 37                                                       |  |  |

|           |              | Over Recommended Operating Conditions                                                            | 6   | Appli        | olication Information |                                                          |  |  |

|           |              | 29                                                                                               |     | 38           |                       |                                                          |  |  |

| PW<br>mei |              | Digital Interpolation Filter and PWM Modulator Over Recommended Operating Conditions Fs = 48 kHz |     | 6.1          |                       | udio Interface Clock Master and<br>terface Configuration |  |  |

|           |              | 29                                                                                               |     |              | 6.1.1                 | Slave Configuration                                      |  |  |

|           | 5.3.3        | TAS5036/TAS5100 System<br>Performance Measured at the                                            |     |              |                       |                                                          |  |  |

|           |              | Speaker Terminals Over Recommended Operating                                                     |     |              | 6.1.2                 | Master Configuration 39                                  |  |  |

|           |              | Conditions                                                                                       | Apı | pendix<br>41 | A—Volui               | me Table                                                 |  |  |

#### **List of Illustrations**

| Figure                                  | Title Page                                                |

|-----------------------------------------|-----------------------------------------------------------|

| 2–1 Crystal Circuit                     | 2–12 PWM Outputs and H-Bridge Driven in BTL Configuration |

| 2–2 External PLL Loop Filter            | 2–13 Typical I2C Sequence                                 |

| 2–3 I2S 64-Fs Format                    | 2–14 Single Byte Write Transfer                           |

| 2–4 I2S 48-Fs Format                    | 2–15 Multiple Byte Write Transfer                         |

| 2–5 Left-Justified 64-Fs Format         | 2–16 Single Byte Read                                     |

| 2–6 Left-Justified 48-Fs Format         | 2–17 Multiple Byte Read                                   |

| 2–7 Right-Justified 64-Fs Format        | 4–1 RESET During System Initialization                    |

| 2–8 Right-Justified 48-Fs Format        | 5–1 RESET Timing                                          |

| 14                                      | 5–2 Power-Down and Power-Up Timing—RESET                  |

| 2–9 DSP Format                          | Preceding PDN                                             |

| 2–10 Attenuation Curve                  | 5–3 Power-Down and Power-Up Timing—RESET Following PDN    |

| 2–11 De-Emphasis Filter Characteristics | 5–4 Error Recovery Timing                                 |

SLES044B

| 5–5 Mute Timing                                                 | 5–11 DSP Absolute Timing                                    |

|-----------------------------------------------------------------|-------------------------------------------------------------|

| 5–6 Right-Justified, IIS, Left-Justified Serial Protocol Timing | 5–12 SCL and SDA Timing                                     |

| 34 5–7 Right, Left, and IIS Serial Mode Timing                  | 5–13 Start and Stop Conditions Timing                       |

| Requirement                                                     | 6–1 Typical TAS5036 Application                             |

| 5–8 Serial Audio Ports Master Mode Timing 35                    | 6–2 TAS5036 Serial Audio Port—Slave Mode Connection Diagram |

| 5–9 DSP Serial Port Timing                                      | 39                                                          |

| 35                                                              | 6-3 TAS5036 Serial Audio Port—Master Mode                   |

| 5–10 DSP Serial Port Expanded Timing                            | Connection Diagram                                          |

#### **List of Tables**

| Tab | le                                                   | Title | Pag                                 | e |

|-----|------------------------------------------------------|-------|-------------------------------------|---|

| 2–1 | Normal-Speed, Double-Speed, and Quad-Speed Operation | 3–1   | I2C Register Map24                  |   |

| 2–2 | Master and Slave Clock Modes                         | 3–2   | General Status Register (Read Only) |   |

| 2–3 | LRCLK, MCLK_IN, and External PLL Rates               | 3–3   | Error Status Register25             |   |

| 2–4 | DCLK                                                 | 3–4   | System Control Register 0           |   |

| 2–5 | 10 Supported Word Lengths                            | 3–5   | System Control Register 1           |   |

| 2–6 | Device Outputs During Reset                          | 3–6   | Error Recovery Register26           |   |

| 2–7 | Values Set During Reset                              | 3–7   | Automute Delay Register             |   |

| 2–8 | Device Outputs During Power Down                     | 3–8   | DC-Offset Control Registers27       |   |

| 2–9 | Volume Register                                      | 3–9   | Six Inter-Channel Delay Registers   |   |

| 2–1 | De-Emphasis Filter Characteristics                   | 3–10  | 0 ABD Delay Register27              | ı |

| 2–1 | 1 Device Outputs During Error Recovery               | 3–11  | 1 Individual Channel Mute Register  |   |

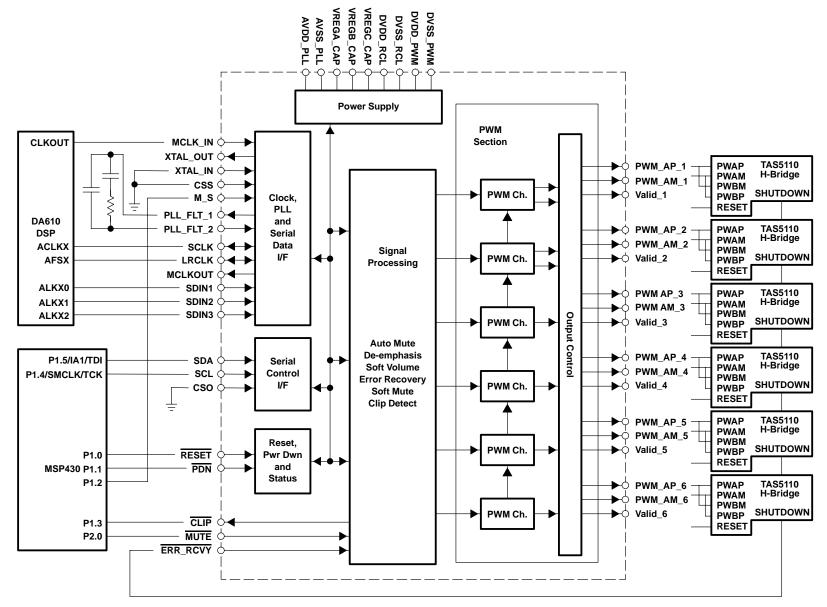

#### 1 Introduction

The TAS5036 is an innovative, cost-effective, high-performance 24-bit six-channel digital pulse width modulator (PWM) based on Equibit™ technology. Combined with a TI digital amplifier power stage, these devices use noise-shaping and sophisticated error correction algorithms to achieve high power efficiency and high-performance digital audio reproduction. The TAS5036 is designed to drive up to six digital power devices to provide six channels of digital audio amplification. The digital power devices can be six conventional monolithic power stages (such as the TAS5110) or six discrete differential power stages using gate drivers and MOSFETs.

The TAS5036 has six independent volume controls and mute. It is designed to drive a digital amplifier power stage (such as the TAS5182) in an H-bridge (bridge tied load) configuration. The device operates in AD and BD modes. This all-digital audio system contains only two analog components in the signal chain—an LC low-pass filter at each speaker terminal and can provide up to 96-dB SNR at the speaker terminals. The TAS5036 has a wide variety of serial input options including right justified (16, 20, or 24 bit), I2S (16, 20, or 24 bit) left justified, or DSP (16-bit) data formats. The device is fully compatible with AES standard sampling rates of 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, 176.4 kHz, and 192 kHz including de-emphasis for 44.1-kHz and 48-kHz sample rates. The TAS5036 plus the TAS51xx power stage device combination was designed for home theater applications such as DVD minicomponent systems, home theater in a box (HTIB), DVD receiver, A/V receiver, or TV sets.

#### 1.1 Features

- True Digital Audio Amplifier

- High Quality Audio

- 96-dB SNR

- <0.1% THD+N</p>

- Six-Channel Volume Control

- Patented Soft Volume

- Patented Soft Mute

- 16-, 20-, or 24-Bit Input Data

- Sampling Rates: 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, 176.4 kHz, and 192 kHz

- Supports Master and Slave Modes

- 3.3-V Power Supply Operation

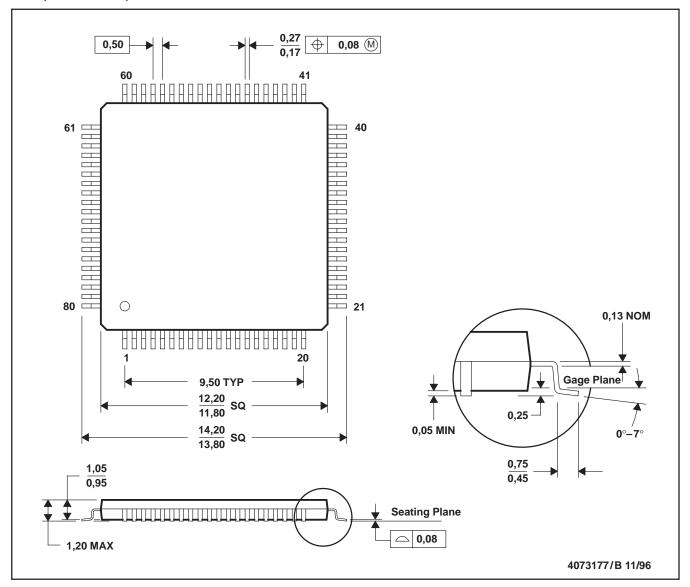

- Economical 80-Pin TQFP Package

- De-Emphasis: 32 kHz, 44.1 kHz, and 48 kHz

- High Power Efficiency

- Clock Oscillator Circuit for Master Modes

- Low Jitter Internal PLL

- Soft Volume and Mute Update

- Excellent PSRR

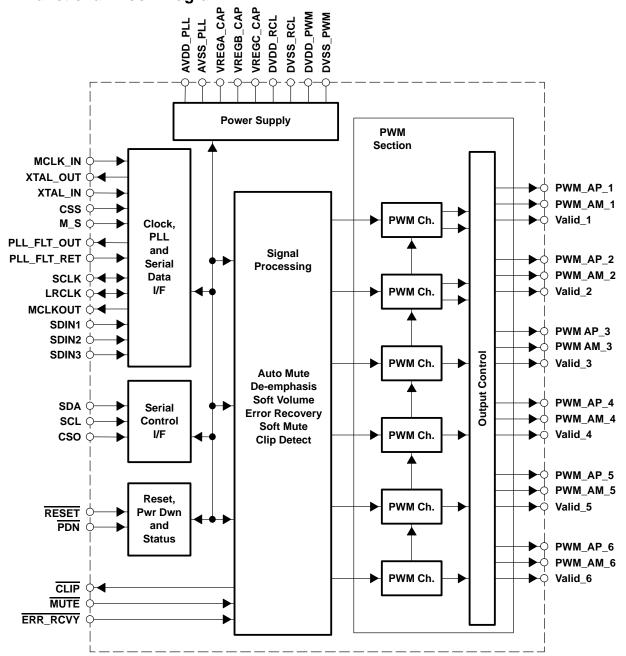

#### 1.2 Functional Block Diagram

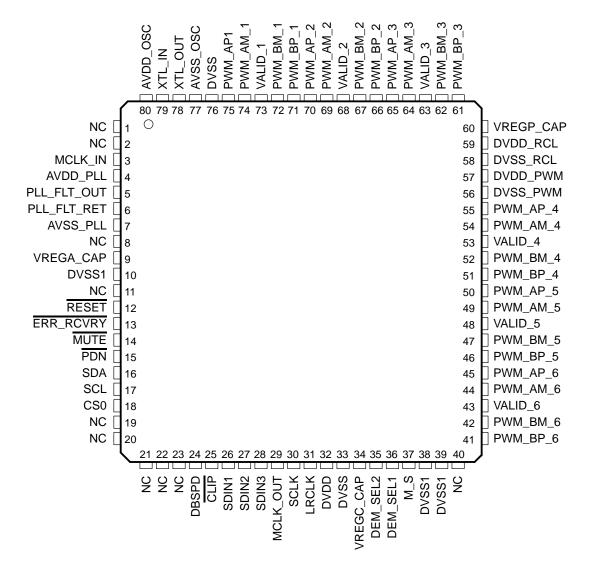

#### 1.3 Terminal Assignments

#### PAG PACKAGE (TOP VIEW)

NC - No internal connection

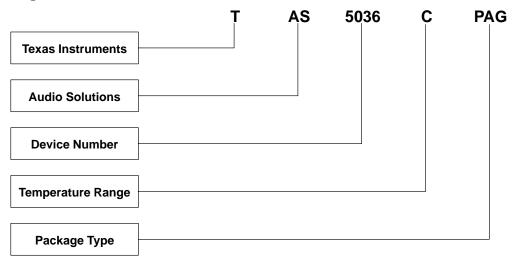

#### 1.4 Ordering Information

#### **AVAILABLE OPTIONS**

|             | PACKAGE                      |

|-------------|------------------------------|

| TA          | PLASTIC 80-PIN TQFP<br>(PAG) |

| 0°C to 70°C | TAS5036CPAG                  |

#### 1.5 Terminal Functions

| TERMI     | NAL                       |     |                                                                                                      |  |  |  |  |  |

|-----------|---------------------------|-----|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME NO.  |                           | 1/0 | DESCRIPTION                                                                                          |  |  |  |  |  |

| AVDD_OSC  | 80                        | Р   | Analog power supply for internal oscillator cells                                                    |  |  |  |  |  |

| AVDD_PLL  | 4                         | Р   | Analog power supply for PLL                                                                          |  |  |  |  |  |

| AVSS_OSC  | 77                        | AO  | Analog ground for internal oscillator cells                                                          |  |  |  |  |  |

| AVSS_PLL  | 7                         | Р   | Analog ground for PLL                                                                                |  |  |  |  |  |

| CLIP      | 25                        | DO  | Digital clipping indicator, active low                                                               |  |  |  |  |  |

| CS0       | 18                        | DI  | I <sup>2</sup> C serial control chip address select input, active high                               |  |  |  |  |  |

| DBSPD     | 24                        | DI  | Sample rate is double speed (88.2 kHz or 96 kHz), active high                                        |  |  |  |  |  |

| DM_SEL1   | 36                        | DI  | De-emphasis select bit 2, 10 = 48 kHz, 11= undefined (none)                                          |  |  |  |  |  |

| DM_SEL2   | 35                        | DI  | De-emphasis select bit 1 (0 = none, 01 = 32 kHz, 10 = 44.1 kHz                                       |  |  |  |  |  |

| DVDD      | 32                        | Р   | Digital power supply                                                                                 |  |  |  |  |  |

| DVDD_PWM  | 57                        | Р   | Digital power supply for PWM                                                                         |  |  |  |  |  |

| DVDD_RCL  | 59                        | Р   | Digital power supply for reclocker                                                                   |  |  |  |  |  |

| DVSS      | 33, 76                    | Р   | Digital ground for digital core and most of I/O buffers                                              |  |  |  |  |  |

| DVSS1     | 10, 38, 39                | DIO | Digital ground for digital core and most of I/O buffers                                              |  |  |  |  |  |

| DVSS_PWM  | 56                        | Р   | Digital ground for PWM                                                                               |  |  |  |  |  |

| DVSS_RCL  | 58                        | Р   | Digital ground for reclocker                                                                         |  |  |  |  |  |

| ERR_RCVRY | 13                        | DI  | Error recovery input, active low                                                                     |  |  |  |  |  |

| LRCLK     | 31                        | DIO | Serial audio data left / right clock (sampling rate clock) (input when M_S = 0; output when M_S = 1) |  |  |  |  |  |

| M_S       | 37                        | DI  | Master/slave mode input signal (master = 1, slave = 0)                                               |  |  |  |  |  |

| MCLK_IN   | 3                         | DI  | MCLK input, slave mode (or master / double-speed mode)                                               |  |  |  |  |  |

| MCLK_OUT  | 29                        | DO  | MCLK output buffered system clock output if M_S = 1; otherwise set to 0                              |  |  |  |  |  |

| MUTE      | 14                        | DI  | Mute input signal, active low (muted signal = 0, normal mode = 1)                                    |  |  |  |  |  |

| N/C       | 1, 2, 8, 11,<br>19–23, 40 |     | Not connected                                                                                        |  |  |  |  |  |

| PDN       | 15                        | DI  | Power down, active low                                                                               |  |  |  |  |  |

| TERMINAL               |    | I/O | DESCRIPTION                                                       |  |  |  |  |

|------------------------|----|-----|-------------------------------------------------------------------|--|--|--|--|

| NAME NO. PLL_FLT_OUT 5 |    |     |                                                                   |  |  |  |  |

|                        |    | AO  | PLL external filter                                               |  |  |  |  |

| PLL_FLT_RET            | 6  | AO  | PLL external filter (internally connected to AVSS_PLL)            |  |  |  |  |

| PWM_AM_1               | 74 | DO  | PWM 1 output (differential -); {positive H-bridge side}           |  |  |  |  |

| PWM_AM_2               | 69 | DO  | PWM 2 output (differential -); {positive H-bridge side}           |  |  |  |  |

| PWM_AM_3               | 64 | DO  | PWM 3 output (differential -); {positive H-bridge side}           |  |  |  |  |

| PWM_AM_4               | 54 | DO  | PWM 4 output (differential -); {positive H-bridge side}           |  |  |  |  |

| PWM_AM_5               | 49 | DO  | PWM 5 output (differential -); {positive H-bridge side}           |  |  |  |  |

| PWM_AM_6               | 44 | DO  | PWM 6 output (differential -); {positive H-bridge side}           |  |  |  |  |

| PWM_AP_1               | 75 | DO  | PWM 1 output (differential +); {positive H-bridge side}           |  |  |  |  |

| PWM_AP_2               | 70 | DO  | PWM 2 output (differential +); {positive H-bridge side}           |  |  |  |  |

| PWM_AP_3               | 65 | DO  | PWM 3 output (differential +); {positive H-bridge side}           |  |  |  |  |

| PWM_AP_4               | 55 | DO  | PWM 4 output (differential +); {positive H-bridge side}           |  |  |  |  |

| PWM_AP_5               | 50 | DO  | PWM 5 output (differential +); {positive H-bridge side}           |  |  |  |  |

| PWM_AP_6               | 45 | DO  | PWM 6 output (differential +); {positive H-bridge side}           |  |  |  |  |

| PWM_BM_1               | 72 | DO  | PWM 1 output (differential -); {negative H-bridge side}           |  |  |  |  |

| PWM_BM_2               | 67 | DO  | PWM 2 output (differential -); {negative H-bridge side}           |  |  |  |  |

| PWM_BM_3               | 62 | DO  | PWM 3 output (differential -); {negative H-bridge side}           |  |  |  |  |

| PWM_BM_4               | 52 | DO  | PWM 4 output (differential -); {negative H-bridge side}           |  |  |  |  |

| PWM_BM_5               | 47 | DO  | PWM 5 output (differential -); {negative H-bridge side}           |  |  |  |  |

| PWM_BM_6               | 42 | DO  | PWM 6 output (differential -); {negative H-bridge side}           |  |  |  |  |

| PWM_BP_1               | 71 | DO  | PWM 1 output (differential +); {negative H-bridge side}           |  |  |  |  |

| PWM_BP_2               | 66 | DO  | PWM 2 output (differential +); {negative H-bridge side}           |  |  |  |  |

| PWM_BP_3               | 61 | DO  | PWM 3 output (differential +); {negative H-bridge side}           |  |  |  |  |

| PWM_BP_4               | 51 | DO  | PWM 4 output (differential +); {negative H-bridge side}           |  |  |  |  |

| PWM_BP_5               | 46 | DO  | PWM 5 output (differential +); {negative H-bridge side}           |  |  |  |  |

| PWM_BP_6               | 41 | DO  | PWM 6 output (differential +); {negative H-bridge side}           |  |  |  |  |

| RESET                  | 12 | DI  | System reset input, active low                                    |  |  |  |  |

| SCL                    | 17 | DI  | I <sup>2</sup> C serial control clock input                       |  |  |  |  |

| SCLK                   | 30 | DIO | Serial audio data clock (shift clock)                             |  |  |  |  |

| SDA                    | 16 | DIO | I <sup>2</sup> C serial control data input/ output                |  |  |  |  |

| SDIN1                  | 26 | DI  | Serial audio data 1 input                                         |  |  |  |  |

| SDIN2                  | 27 | DI  | Serial audio data 2 input                                         |  |  |  |  |

| SDIN3                  | 28 | DI  | Serial audio data 3 input                                         |  |  |  |  |

| VALID_1                | 73 | DO  | Output indicating validity of PWM outputs, channel 1, active high |  |  |  |  |

| VALID_2                | 68 | DO  | Output indicating validity of PWM outputs, channel 2, active high |  |  |  |  |

| VALID_3                | 63 | DO  | Output indicating validity of PWM outputs, channel 3, active high |  |  |  |  |

| VALID_4                | 53 | DO  | Output indicating validity of PWM outputs, channel 4, active high |  |  |  |  |

| VALID_5                | 48 | DO  | Output indicating validity of PWM outputs, channel 5, active high |  |  |  |  |

| VALID_6                | 43 | DO  | Output indicating validity of PWM outputs, channel 6, active high |  |  |  |  |

| VREGA_CAP              | 9  | Р   | C05 voltage regulator capacitor                                   |  |  |  |  |

| VREGB_CAP              | 60 | Р   | C05 voltage regulator capacitor                                   |  |  |  |  |

| VREGC_CAP              | 34 | Р   | C05 voltage regulator capacitor                                   |  |  |  |  |

| XTL_IN                 | 79 | Al  | Crystal or TTL level clock input                                  |  |  |  |  |

| XTL_OUT                | 78 | AO  | Crystal output (not for external usage)                           |  |  |  |  |

|                        |    |     | 1 - 3                                                             |  |  |  |  |

#### 2 Architecture Overview

The TAS5036 is composed of six functional elements:

- Clock, PLL, and serial data interface (IIS)

- Reset/power down circuitry

- Serial control interface (IIC)

- Signal processing unit

- Pulse width modulator (PWM)

- Power supply

#### 2.1 Clock and Serial Data Interface

The TAS5036 clock and serial data interface contains an input serial data slave and the clock master/ slave interface.

The serial data slave interface receives information from a digital source such as a DSP, S/PDIF receiver, analog-to-digital converter (ADC), digital audio processor (DAP) such as the TAS3103, or other serial bus master at sample rates of for sample rates of 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz,176.4 kHz, and 192 kHz. The serial data interface has three serial data inputs that can accept up to six channels of data. The serial data interfaces support left justified and right justified for 16-, 20-, and 24-bits. In addition, the serial data interfaces support the DSP protocol for 16 bits and the I2S protocal for 24 bits. The received data is data passed to the TAS5036 signal-processing unit.

The TAS5036 can function as a receiver or a generator for the MCLK\_IN (master clock), SCLK (shift clock), and LRCLK (left/right clock) signals that control the flow of data on the three serial data interfaces. The TAS5036 is a clock master when it generates these clocks and is a clock slave when it receives these clocks.

The TAS5036 is a synchronous design that relies upon master clock to provide a reference clock for all of the device operations. When operating as a slave, this reference clock is MCLK\_IN. When operating as a master, the reference clock is either TTL clock input to XTAL\_IN or a crystal attached across XTAL\_IN and XTAL\_OUT.

If the master clock stops, the TAS5036 will perform a clock error recovery sequence. The clock error recovery sequence temporarily suspends processing, places the PWM outputs in a hard mute (PWM P outputs are low; PWM M outputs are high, and all VALID signals are low), resets all internal processes, sets the volumes to mute, and suspends all I<sup>2</sup>C operations.

When the master clock is resumed, the TAS5036 exits the clock error recovery sequence by performing a 4.3-ms partial re—initialization, noiselessly restarting the PWM output, and ramping the volume up to the level specified in the volume control registers. The volume update is performed over a 43 ms. interval. The TAS5036 will preserve all control register settings that were set prior to the clock interruption.

Quad—speed mode is used to support sampling rates of 176.4 kHz and 192 kHz. Quad—speed mode is auto detected supported in slave mode and invoked by control in master mode in slave mode. If the device is not in double speed mode, quad—speed mode is automatically detected when MCLK\_IN is 128Fs. In master mode, the PWM is placed in quad—speed mode by setting the quad—speed bit in the system control register through the serial control interface.

The clock and serial data interface has two control parameters: data sample rate and clock master or slave.

#### 2.1.1 Normal-Speed, Double-Speed, and Quad-Speed Selection

The sampling rate is selected through a pin (DBSPD) or the serial control register 0 (X02). When a sample rate is selected, the system automatically performs an error recovery sequence and switches to the new sampling rate. As shown in subsequent sections, the sample rate control sets the frequencies of the SCLK and LRCLK in clock slave mode and the output frequencies of SCLK and LRCLK in clock master mode.

The reference clock for the PLL can be provided by either an external clock source (attached to XTAL\_IN) or a crystal (connected across terminals XTAL\_IN and XTAL\_OUT). The external source attached to MCLK\_IN is 256 times (128 in quad mode) the data sample rate (Fs). The SCLK frequency is 64 times the data sample rate and the SCLK frequency of 48 times the data sample rate is not supported in the master mode. The LRCLK frequency is the data sample rate.

There are three data rates: normal speed, double speed, and quad speed.

Normal-speed mode supports data rates of 32 kHz, 44.1 kHz, and 48 kHz. Normal speed is supported in the master and slave modes. The PWM is placed in normal speed by setting the DBSPD terminal low or by setting the normal mode bits in the system control register through the serial control interface. Following this operation, the PWM performs an error recovery sequence automatically and operates in the normal speed mode.

Double-speed mode is used to support sampling rates of 88.2 kHz and 96 kHz. Double speed is supported in master and slave modes. The PWM is placed in double speed mode by setting the DBSPD terminal high or by setting the double speed bits in the system control register through the serial control interface. Following this operation, the PWM performs an error recovery sequence automatically and operates in the double speed mode.

Quad-speed mode is used to support sampling rates of 176.4 kHz and 192 kHz. Quad-speed mode is auto detected supported in slave mode and invoked by control in master mode in slave mode. If the device is not in double speed mode, quad-speed mode is automatically detected when MCLK\_IN is 128Fs. In master mode, the PWM is placed in quad-speed mode by setting the quad-speed bit in the system control register through the serial control interface.

|                                    | - · · · · · · · · · · · · · · · · · · ·   | •               | -                             |

|------------------------------------|-------------------------------------------|-----------------|-------------------------------|

| QUAD-SPEED CONTROL<br>REGISTER BIT | DBSPD TERMINAL OR<br>CONTROL REGISTER BIT | MODE            | SPEED SELECTION               |

| 0                                  | 0                                         | Master or slave | Normal speed                  |

| 0                                  | 1                                         | Master or slave | Double speed                  |

| 1                                  | 0                                         | Master or slave | Quad speed                    |

| 0                                  | 0                                         | Slave           | Quad speed if MCLK_IN = 128Fs |

| 1                                  | 1                                         | Master or slave | Error                         |

Table 2–1. Normal-Speed, Double-Speed, and Quad-Speed Operation

#### 2.1.2 Clock Master/Slave Mode (M\_S)

Clock master and slave mode can be invoked using the M S (master slave) terminal.

This terminal specifies the default mode that is set immediately following a device RESET. The serial data interface setting permits the clock generation mode to be changed during normal operation.

The transition to master mode occurs:

Following a RESET when M\_S terminal has a logic high applied

The transition to slave mode occurs:

Following a RESET when M\_S terminal has a logic low applied

#### 2.1.3 Clock Master Mode

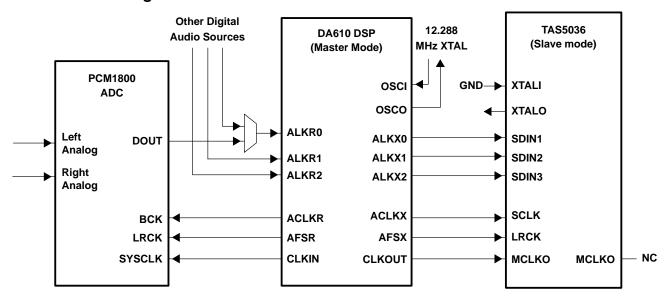

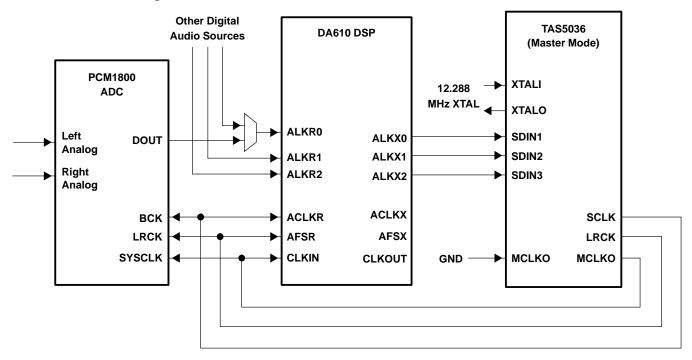

When M\_S = 1 following a RESET, the TAS5036 provides the master clock, SCLK, and LRCLK to the rest of the system. In the master mode, the TAS5036 outputs the audio system clocks MCLK\_OUT, SCLK, and LRCLK.

The TAS5036 device generates these clocks plus its internal clocks from the internal phase-locked loop (PLL). The reference clock for the PLL can be provided by either an external clock source (attached to XTAL\_IN) or a crystal (connected across terminals XTAL\_IN and XTAL\_OUT). The external source attached to MCLK\_IN is 256 times (128 in quad mode) the data sample rate (Fs). The SCLK frequency is 64 times the data sample rate and the SCLK frequency of 48 times the data sample rate is not supported in the master mode. The LRCLK frequency is the data sample rate.

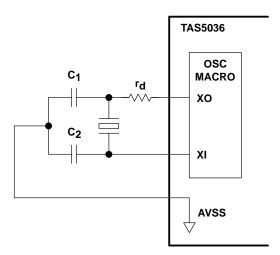

#### 2.1.3.1 Crystal Type and Circuit

In clock master mode the TAS5036 can derive the MCLKOUT, SCLK, and LRCLK from a crystal. In this case, the TAS5036 uses a parallel-mode fundamental-mode crystal. This crystal is connected to the TAS5036 as shown in Figure 2–1.

$r_d$  = Drive level control resistor – crystal vendor specified  $C_L$  = Crystal load capacitance (capacitance of circuitry between the two terminals of the crystal)  $C_L$  =  $(C_1 \times C_2)/(C_1 + C_2) + C_S$  (where  $C_S$  = board stray capacitance ~ 3 pF) Example: Vendor recommended  $C_L$  = 18 pF,  $C_S$  = 3 pF  $\geq$   $C_1$  =  $C_2$  = 2 x (18–3) = 30 pF

Figure 2-1. Crystal Circuit

#### 2.1.4 Clock Slave Mode

In the slave mode ( $M_S = 0$ ), the master clock, LRCLK, and SCLK are inputs to the TAS5036. The master clock is supplied through the MCLK\_IN terminal.

As in the master mode, the TAS5036 device developed its internal timing from internal phase-locked loop (PLL). The reference clock for the PLL is provided by the input to the MCLK\_IN terminal. This input is at a frequency of 256 times (128 in quad mode) the input data rate. The SCLK frequency is 48 or 64 times the data sample rate. The LRCLK frequency is the data sample rate. The TAS5036 does not require any specific phase relationship between SRCLK and MCLK\_IN, but there must be synchronization.

The TAS5036 monitors the relationship between MCLK, SCLK and LRCLK. The TAS5036 will detect if any of the three clocks are absent, if LRCLK rate changes more the  $\pm 10$  MCLK cycles since the last device reset or clock error recovery, or if MCLK frequency is changing substantially with respect to the PLL frequency. When a clock error is detected the TAS5036 will perform a clock error recovery sequence. If one or more of the clock signals are absent, the TAS5036 is held with the outputs in hard mute until the clock is resumed. Once the clock is resumed, the clock error recover sequence is completed.

Note. The detection of a clock error causes the TAS5036 to perform an immediate hard mute and suspension of all processes. This abrupt transition can produce a faint click as the outputs are muted.

Since the clocks are removed when changing media or during input selection, it is possible to use this knowledge to completely eliminate clicks in these conditions. In this case, the click is prevented by muting the outputs by using the MUTE terminal or the I<sup>2</sup>C/MUTE command 43 ms in advance of the clocks being removed.

In slave mode operation, when a crystal is connected to XTAL\_IN and XTAL\_OUT pins, the internal oscillator of the TAS5036 is turned off.

In the slave mode, MCLK\_OUT is driven low.

Table 2–2 shows all the possible master and slave modes. When operating in quad mode (Fs = 176.4 kHz or 192 kHz), the device works in slave mode only with MCLK\_IN = 128 Fs.

Table 2–3 shows the clocks speed for normal, double and guad modes.

Table 2-2. Master and Slave Clock Modes

| DESCRIPTION                        | M_S | DBSPD | XTL_IN<br>(MHz)† | MCLK_IN<br>(MHz)‡ | SCLK<br>(MHz)¶ | LRCLK<br>(kHz)¶ | MCLK_OUT<br>(MHz)# |

|------------------------------------|-----|-------|------------------|-------------------|----------------|-----------------|--------------------|

| Internal PLL, master, normal speed | 1   | 0     | 8.192            | -                 | 2.048          | 32              | 8.192              |

| Internal PLL, master, normal speed | 1   | 0     | 11.2896          | -                 | 2.8224         | 44.1            | 11.2896            |

| Internal PLL, master, normal speed | 1   | 0     | 12.288           | -                 | 3.072          | 48              | 12.288             |

| Internal PLL, master, double speed | 1   | 1     | -                | 22.5792§          | 5.6448         | 88.2            | 22.5792            |

| Internal PLL, master, double speed | 1   | 1     | -                | 24.576§           | 6.144          | 96              | 24.576             |

| Internal PLL, master, quad speed   | 1   | 0     | -                | 22.5792           | 11.2896        | 176.4           | 22.5792            |

| Internal PLL, master, quad speed   | 1   | 0     | -                | 24.576            | 12.288         | 192             | 24.576             |

| Internal PLL, slave, normal speed  | 0   | 0     | -                | 8.192§            | 2.0484         | 32              | Digital GND        |

| Internal PLL, slave, normal speed  | 0   | 0     | -                | 11.2896§          | 2.8224         | 44.1            | Digital GND        |

| Internal PLL, slave, normal speed  | 0   | 0     | -                | 12.288§           | 3.072          | 48              | Digital GND        |

| Internal PLL, slave, double speed  | 0   | 1     | -                | 22.5792           | 5.6448         | 88.2            | Digital GND        |

| Internal PLL, slave, double speed  | 0   | 1     | -                | 24.576§           | 6.144          | 96              | Digital GND        |

| Internal PLL, slave, quad speed    | 0   | 0     | -                | 22.5792§          | 11.2896        | 176             | Digital GND        |

| Internal PLL, slave, quad speed    | 0   | 0     | -                | 24.576§           | 12.288         | 192             | Digital GND        |

| External PLL, master, normal speed | 1   | 0     | -                | -                 | 2.048          | 32              | 8.192              |

| External PLL, master, normal speed | 1   | 0     | -                | -                 | 2.8224         | 44.1            | 11.2896            |

| External PLL, master, normal speed | 1   | 0     | -                | -                 | 3.072          | 48              | 12.288             |

| External PLL, master, double speed | 1   | 1     | -                | -                 | 5.6448         | 88.2            | 22.5792            |

| External PLL, master, double speed | 1   | 1     | -                | -                 | 6.144          | 96              | 24.576             |

| External PLL, master, quad speed   | 1   | 0     | -                | -                 | 11.2896        | 176.4           | 22.5792            |

| External PLL, master, quad speed   | 1   | 0     | -                | -                 | 12.288         | 192             | 24.576             |

| External PLL, slave, normal speed  | 0   | 0     | -                | 8.192§            | 2.0484         | 32              | Digital GND        |

| External PLL, slave, normal speed  | 0   | 0     | -                | 11.2896§          | 2.8224         | 44.1            | Digital GND        |

| External PLL, slave, normal speed  | 0   | 0     | -                | 12.288§           | 3.072          | 48              | Digital GND        |

| External PLL, slave, double speed  | 0   | 1     | -                | 22.5792           | 5.6448         | 88.2            | Digital GND        |

| External PLL, slave, double speed  | 0   | 1     | -                | 24.576§           | 6.144          | 96              | Digital GND        |

| External PLL, slave, quad speed    | 0   | 0     | -                | 22.5792§          | 11.2896        | 176             | Digital GND        |

| External PLL, slave, quad speed    | 0   | 0     | -                | 24.576§           | 12.288         | 192             | Digital GND        |

Table 2-3. LRCLK, MCLK\_IN, and External PLL Rates

|          | NOR    | MAL SPEED | (kHz)    |        | DOUBLE SPEED (kHz) |        |          |        | QUAD SPEED (kHz) |          |        |

|----------|--------|-----------|----------|--------|--------------------|--------|----------|--------|------------------|----------|--------|

| LRCLK    | 1FS    | 32        | 44.1     | 48     | 1FS                | 64     | 88.2     | 96     | 1FS              | 176.4    | 192    |

| MCLK_IN  | 256FS  | 8,192     | 11,289.6 | 12,288 | 256FS              | 16,384 | 22,579.2 | 24,576 | 128FS            | 22,579.2 | 24,576 |

| EXT. PLL | 2048FS | 65,536    | 90,316.8 | 98,304 | 1024FS             | 65,536 | 90,316.8 | 98,304 | 512FS            | 90,316.8 | 98,304 |

<sup>†</sup> A crystal oscillator is connected to XTL\_IN.

‡ MCLK\_IN tied low when input to XTL\_IN is provided; XTL\_IN tied low when MCLK\_IN\_IN is provided.

<sup>§</sup> External MCLK\_IN connected to MCLK\_IN\_IN input

$<sup>\</sup>P$  SCLK and LRCLK are outputs when M\_S=1, and inputs when M\_S=0.

<sup>#</sup> MCLK\_OUT is driven low when M\_S=0.

<sup>||</sup> Quad-speed mode is detected automatically.

**<sup>★</sup>SCLK** can be 48 or 64 times Fs

#### 2.1.5 PLL Filter

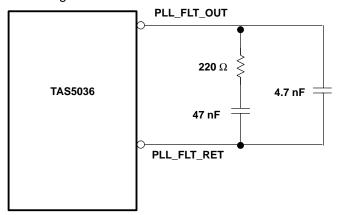

A low jitter PLL produces the internal timing of the TAS5036 (when in master mode), the master clock, SCLK, and LRCLK. Connections for the PLL external loop filter are provided through PLL\_FLT\_OUT and PLL FLT RET as shown in Figure 2–2.

Figure 2-2. External PLL Loop Filter

#### 2.1.6 DCLK

DCLK is the internal high frequency clock that is produced by the PLL circuitry from MCLK. The TAS5036A uses the DCLK to control all internal operations. DCLK is 8 times the speed of MCLK in normal speed mode, 4 times MCLK in double speed, and 2 times MCLK in quad speed. With respect to the I<sup>2</sup>C addressable registers, DCLK clock cycles are used to specify Interchannel delay and to detect when the MCLK is frequency is drifting. Table 2–4 DCLK shows the relationship between Sample Rate, MCLK and DCLK.

| FS<br>(kHz) | MCLK<br>(MHz) | DCLK<br>(MHz) | DCK Period<br>(ns) |

|-------------|---------------|---------------|--------------------|

| 32          | 8.1920        | 65.5360       | 15.3               |

| 44.1        | 11.2896       | 90.3168       | 11.1               |

| 48          | 12.2880       | 98.3040       | 10.2               |

| 88          | 22.5280       | 90.1120       | 11.1               |

| 96          | 24.5760       | 98.3040       | 10.2               |

| 192         | 49.1520       | 98.3040       | 10.2               |

Table 2-4. DCLK

#### 2.1.7 Serial Data Interface

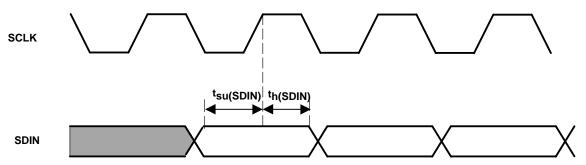

The TAS5036 operates as a slave only/receive only serial data interface in all modes. The TAS5036 has three PCM serial data interfaces to accept six channels of digital data though the SDIN1, SDIN2, SDIN3 inputs. The serial audio data is in MSB first; 2s complement format.

The serial data interfaces of the TAS5036 can be configured in right justified, I<sup>2</sup>S, left-justified, or DSP modes. This interface supports 32-kHz, 44.1-kHz, 48-kHz, 88-kHz, 96-kHz, 176.4-kHz, and 192-kHz data sample rates. The serial data interface format is specified using the data interface control register. The supported word lengths are shown in Table 2–5.

During normal operating conditions if the serial data interface settings change state, an error recovery sequence is initiated.

| Table 2 3. Supported Word Lengths |                 |      |      |      |  |  |  |  |  |  |  |

|-----------------------------------|-----------------|------|------|------|--|--|--|--|--|--|--|

| DATA MODES                        | WORD<br>LENGTHS | MOD2 | MOD1 | MOD0 |  |  |  |  |  |  |  |

| Right justified, MSB first        | 16              | 0    | 0    | 0    |  |  |  |  |  |  |  |

| Right justified, MSB first        | 20              | 0    | 0    | 1    |  |  |  |  |  |  |  |

| Right justified, MSB first        | 24              | 0    | 1    | 0    |  |  |  |  |  |  |  |

| l <sup>2</sup> S                  | 16              | 0    | 1    | 1    |  |  |  |  |  |  |  |

| l <sup>2</sup> S                  | 20              | 1    | 0    | 0    |  |  |  |  |  |  |  |

| I <sup>2</sup> S                  | 24              | 1    | 0    | 1    |  |  |  |  |  |  |  |

| Left justified, MSB first         | 24              | 1    | 1    | 0    |  |  |  |  |  |  |  |

16

Table 2-5. Supported Word Lengths

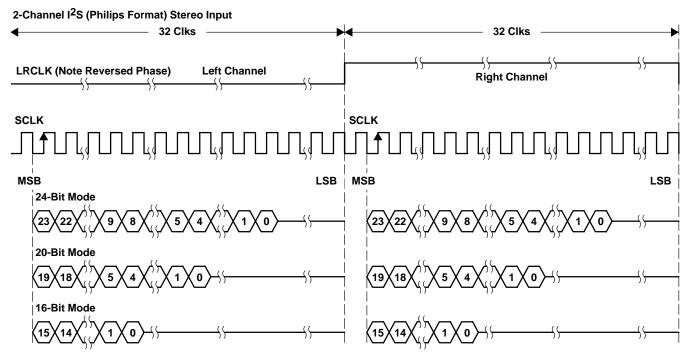

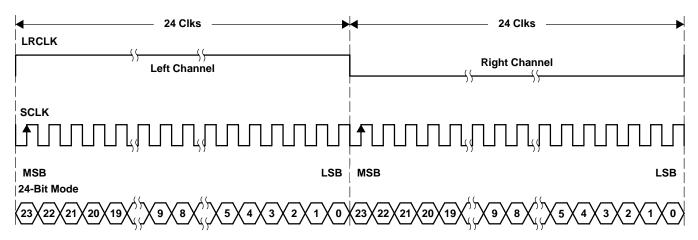

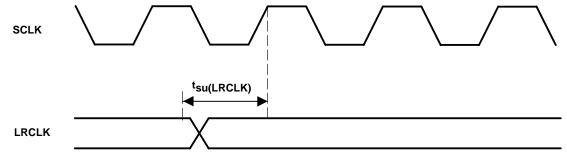

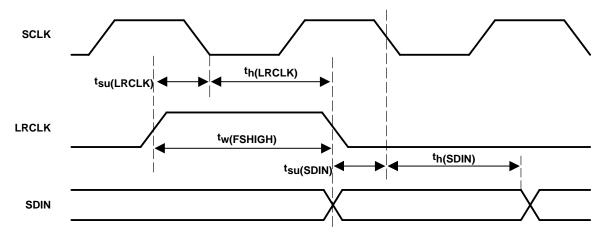

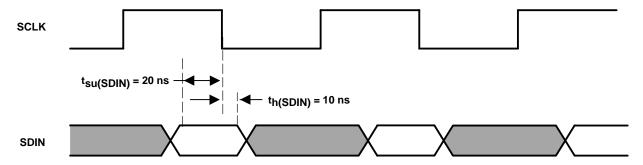

#### 2.1.7.1 I<sup>2</sup>S Timing

DSP frame

I<sup>2</sup>S timing uses an LRCLK to define when the data being transmitted is for the left channel or the right channel. The LRCLK is low for the left channel and high for the right channel. A bit clock running at 48 or 64 times Fs is used to clock in the data. There is a delay of one bit clock from the time the LRCLK signal changes state to the first bit of data on the data lines. The data is written MSB first and is valid on the rising edge of the bit clock. The TAS5036 masks unused trailing data bit positions. Master mode only supports a 64 times Fs bit clock.

Figure 2-3. I<sup>2</sup>S 64-Fs Format

Figure 2-4. I<sup>2</sup>S 48-Fs Format

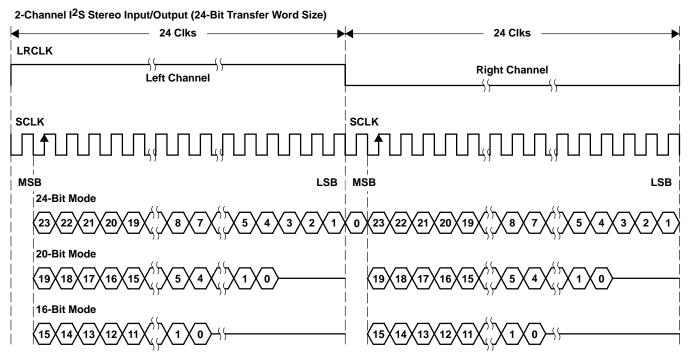

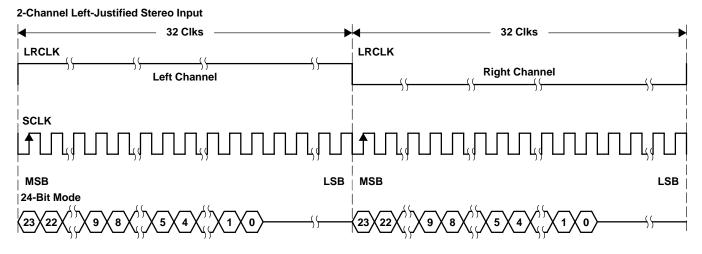

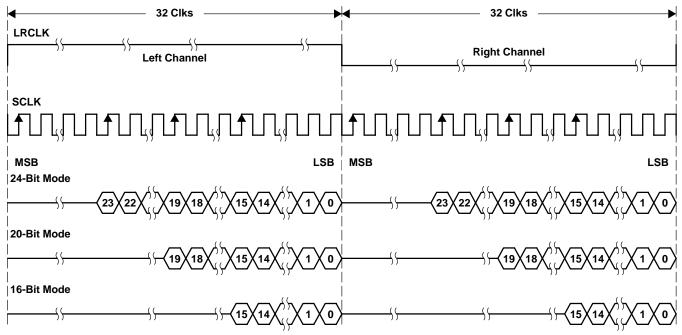

#### 2.1.7.2 Left-Justified Timing

Left-justified (LJ) timing uses an LRCLK to define when the data being transmitted is for the left channel and the right channel. The LRCLK is high for the left channel and low for the right channel. A bit clock running at 48 or 64 times Fs is used to clock in the data. The first bit of data appears on the data lines at the same time the LRCLK toggles. The data is written MSB first and is valid on the rising edge of the bit clock. The TAS5036 masks unused trailing data bit positions. Master mode only supports a 64 times Fs bit clock.

NOTE: All data presented in 2s complement form with MSB first.

Figure 2–5. Left-Justified 64-Fs Format

#### 2-Channel Left-Justified Stereo Input/Output (24-Bit Transfer Word Size)

Figure 2-6. Left-Justified 48-Fs Format

#### 2.1.7.3 Right-Justified Timing

Right-justified (RJ) timing uses an LRCLK to define when the data being transmitted is for the left channel and the right channel. The LRCLK is high for the left channel and low for the right channel. A bit clock running at 48 or 64 times Fs is used to clock in the data. The first bit of data appears on the data 8-bit clock periods (for 24-bit data) after LRCLK toggles. In RJ mode, the last bit clock before LRCLK transitions always clocks the LSB of data. The data is written MSB first and is valid on the rising edge of bit clock. The TAS5036 masks unused leading data bit positions. Master mode only supports a 64 times Fs bit clock.

#### 2-Channel Right-Justified (Sony Format) Stereo Input

NOTE: All data presented in 2s complement form with MSB first.

Figure 2-7. Right-Justified 64-Fs Format

2-Channel Right-Justified Stereo Input/Output (24-Bit Transfer Word Size)

NOTE: All data presented in 2s complement form with MSB first.

Figure 2-8. Right-Justified 48-Fs Format

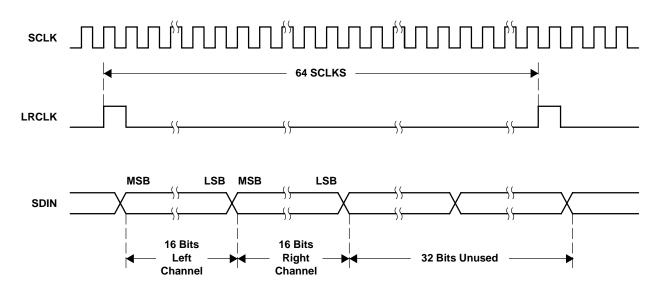

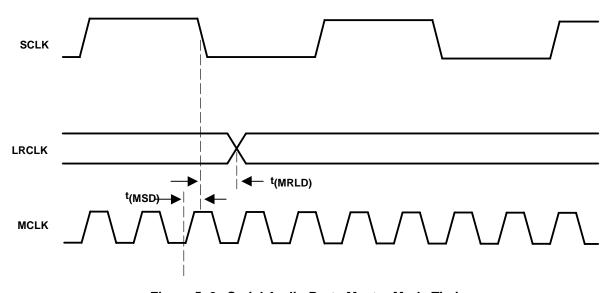

#### 2.1.7.4 DSP Mode Timing

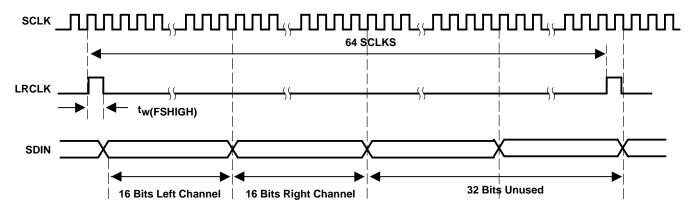

DSP mode timing uses an LRCLK to define when data is to be transmitted for both channels. A bit clock running at  $64 \times Fs$  is used to clock in the data. The first bit of the left channel data appears on the data lines following the LRCLK transition. The data is written MSB first and is valid on the rising edge of the bit clock. The TAS5036 masks unused trailing data bit positions.

Figure 2-9. DSP Format

#### 2.2 Reset, Power Down, and Status

The reset, power down, and status circuitry provides the necessary controls to bring the TAS5036 to the initial inactive condition, achieve low power standby, and report system status.

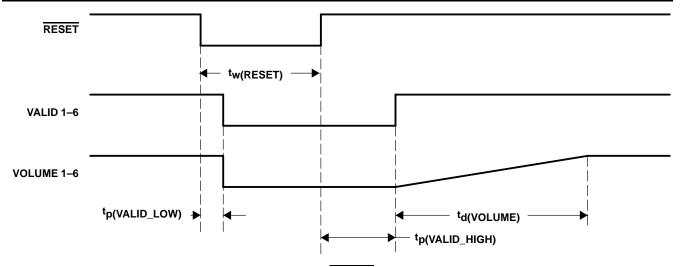

#### 2.2.1 Reset—RESET

The TAS5036 is placed in the reset mode by setting the RESET terminal low.

RESET is an asynchronous control signal that restores the TAS5036 to its default conditions, sets the valid 1–6 outputs low, and places the PWM in the hard mute state. Volume is immediately set to full attenuation (there is no ramp down).

As long as the RESET terminal is held low, the device is in the reset state. During reset, all I<sup>2</sup>C and serial data bus operations are ignored. Table 2–6 shows the device output signals while RESET is active.

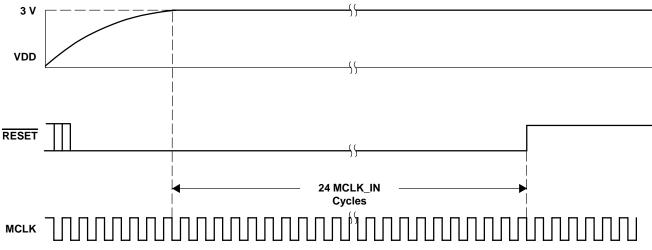

Upon the release of RESET, if POWER\_DWN is high, the system performs a 4-ms to 5-ms device initialization and then ramps the volume up to 0 db using a soft volume update sequence. If MCLK\_IN is not active when RESET is released high, then a 4-ms to 5-ms initialization sequence is produced once MCLK\_IN becomes active.

During device initialization all controls are reset to their initial states. Table 2–7 shows the control settings that are changed during initialization.

RESET should be applied during power-up initialization or while changing the master slave clock states.

| SIGNAL          | MODE   | SIGNAL STATE |

|-----------------|--------|--------------|

| Valid 1-Valid 6 | All    | Low          |

| PWM P-outputs   | All    | Low          |

| PWM M-outputs   | All    | Low          |

| MCLKOUT         | All    | Low          |

| SCLK            | Master | Low          |

| SCLK            | Slave  | Signal input |

| LRCLK           | Master | Low          |

| LRCLK           | Slave  | Signal input |

| SDA             | All    | Signal input |

| CLIP            | All    | High         |

Table 2-6. Device Outputs During Reset

Because the RESET is an asynchronous control signal, small clicks and pops can be produced during the application (the leading edge) of this control. However, when RESET is released, the transition from the hard mute state back to normal operation is performed synchronously using a quiet sequence.

If a completely quiet reset sequence is desired, MUTE should be applied before applying RESET.

Table 2-7. Values Set During Reset

| CONTROL            | SETTING                                                     |

|--------------------|-------------------------------------------------------------|

| Volume             | 0 dB                                                        |

| MCLK_IN frequency  | 256                                                         |

| Master/slave mode  | M_S terminal state                                          |

| Auto mute          | Enabled                                                     |

| De-emphasis        | None                                                        |

| DC offset          | 0                                                           |

| Interchannel delay | Each channel set at 16 clocks higher then preceding channel |

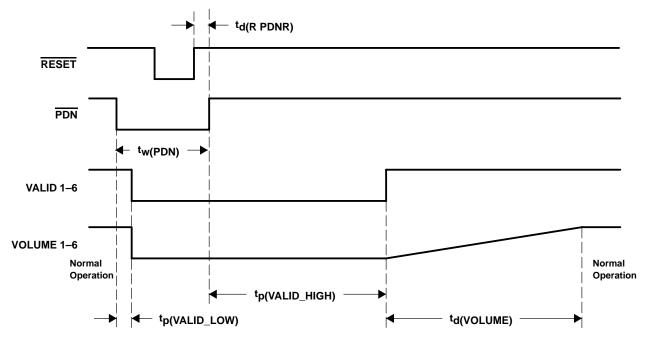

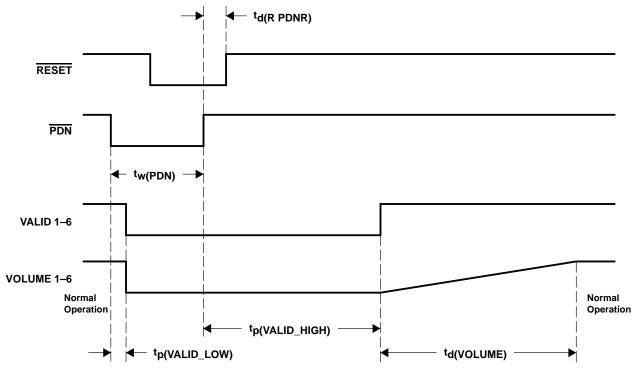

#### 2.2.2 Power Down—PDN

The TAS5036 can be placed into the power-down mode by holding the  $\overline{PDN}$  terminal low. When power-down mode is entered, both the PLL and the oscillator are shut down. Volume is immediately set to full attenuation (there is no ramp down). The valid 1–6 outputs are immediately asserted low and the PWM outputs are placed in the hard mute state.  $\overline{PDN}$  initiates device power down without clock inputs. As long as the  $\overline{PDN}$  terminal is held low—the device is in the power-down (hard mute) state.

During power down, all I<sup>2</sup>C and serial data bus operations are ignored. Table 2–8 shows the device output signals while PDN is active.

|                 | •      | •            |

|-----------------|--------|--------------|

| SIGNAL          | MODE   | SIGNAL STATE |

| Valid 1-Valid 6 | All    | Low          |

| PWM P-outputs   | All    | Low          |

| PWM M-outputs   | All    | Low          |

| MCLKOUT         | All    | Low          |

| SCLK            | Master | Low          |

| SCLK            | Slave  | Signal input |

| LRCLK           | Master | Low          |

| LRCLK           | Slave  | Signal input |

| SDA             | All    | Signal input |

| CLIP            | All    | High         |

Table 2-8. Device Outputs During Power Down

To place the device in total power-down mode, both RESET and power-down modes must be enabled. Prior to bringing PDN high, RESET must be brought low for a minimum of 50 ns.

Because  $\overline{PDN}$  is an asynchronous control signal, small clicks and pops can be produced during the application (the leading edge) of this control. However, when  $\overline{PDN}$  is released, the transition from the hard mute state back to normal operation is performed synchronously using a quiet sequence.

If a completely quiet reset sequence is desired, MUTE should be applied before applying PDN.

#### 2.2.2.1 Recovery Time Options

To support the requirements of various system configurations, the TAS5036 can come up to the normal state after either a long (100 ms) or a short (5 ms) delay.

1. In the first case, a slow system (95 ms to 100 ms) start-up occurs at the end of the power-down sequence when:

RESET is high for at least 16 MCLK IN periods before PDN goes high.

2. Otherwise a fast (4 ms to 5 ms) start up occurs.

**NOTE:** If MCLK\_IN is not active when both of these signals are released high, then a a fast (4 ms to 5 ms) start up occurs once MCLK\_IN becomes active.

#### 2.2.3 Status Registers

The TAS5036 provides device identification and operational status information that is accessible through the serial control interface status registers that provide general device information.

**Device ID**—The TAS5036 provides a device identification code that is accessible through the serial control interface

Volume Update is in Progress—Whenever a volume change is in progress, this status bit is high.

**No Internal Errors (All Valid Signals are High)**—When there are no internal errors in the TAS5036 and all outputs are valid, this status bit is high.

**LRCLK Error**—When there are the MCLK\_IN rate changes more than ±10 MCLK\_IN cycles from the correct number of cycles (128 or 256) per LRCLK cycle

**MCLK\_IN Error**—When the MCLK\_IN frequency changes such that it is out of synchronization with internal PLL generated clock

#### 2.3 Signal Processing

This section contains the signal processing functions that are contained in the TAS5036. The signal processing is performed using a high-speed 24-bit signal processing architecture. The TAS5036 performs the following signal processing features:

- Individual channel soft volume with a range of 24 dB to −114 dB plus mute

- Soft mute

- Auto mute

- 50-μs/15-μs de-emphasis filter supported in the sampling rates 32 kHz, 44.1 kHz, and 48 kHz

#### 2.3.1 Volume Control

The gain of each output can be adjusted by a soft digital volume control for each channel. Volume adjustments are performed using a soft gain update s-curve, which is approximated using a second order filter fit. The curve fit is performed over a transition interval between 41 ms and 65 ms.

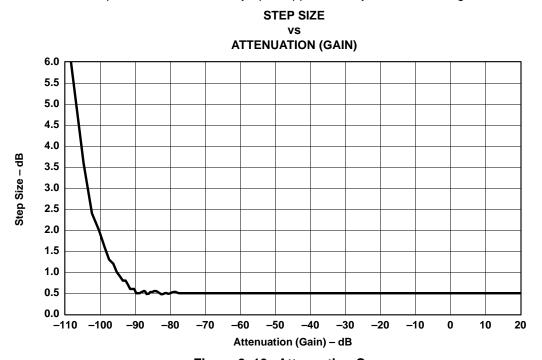

The volume of each channel can be adjusted from mute to 24 dB to –114 dB in 0.5 dB steps. Because of the numerical representation that is used to control the volume, at very low volume levels the step size increases for gains of that are less than –96 dB. The default volume setting following power up or reset is 0 dB for all channels. The step size increases linearly up to approximately –90 dB, see Figure 2–10.

Figure 2–10. Attenuation Curve

The volume control format for each channel is expressed in 8 bits. The volume for each channel is set by writing 8 bits via the serial control interface. The MSB bit is written first as in the bit position 0 (LSB position).

The volume for each channel can be set using a single or multiple address write operation to the volume control register via the serial control interface. To change the volume of all six channels requires that 6 registers be updated.

To coordinate the volume adjustment of multiple channels simultaneously, the TAS5036 performs a delayed volume update upon receiving a volume change command. Following the completion of the register volume write operations, the TAS5036 waits for 5 ms for another volume command to be given. If no volume command is issued in that period of time, the TAS5036 starts adjusting the volume of the channels that received volume settings.

While a volume update is being performed, the system status register indicates that the update is in progress. During the update, all subsequent volume control setting requests that are sent to the TAS5036 are received and stored as a single next value for a subsequent update. If more than one volume setting request is sent, only the last is retained.

Table 2-9. Volume Register

|       | VOLUME REGISTER |       |       |       |       |       |       |  |  |  |

|-------|-----------------|-------|-------|-------|-------|-------|-------|--|--|--|

| D 7   | D 6             | D 5   | D 4   | D 3   | D 2   | D 1   | D 0   |  |  |  |

| Vol   | Vol             | Vol   | Vol   | Vol   | Vol   | Vol   | Vol   |  |  |  |

| Bit 7 | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

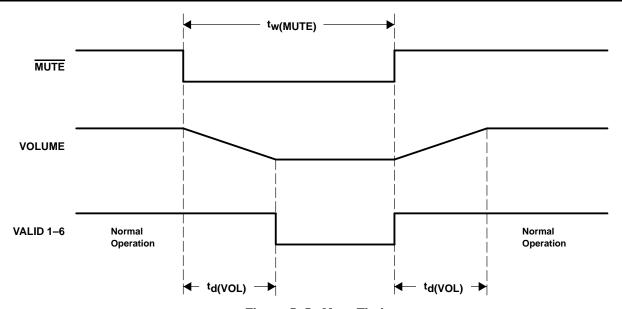

#### 2.3.2 Mute

The application of mute ramps the volume from any setting to noiseless hard mute state. There are two methods in which the TAS5036 can be placed into mute. The TAS5036 is placed in the noiseless mute when the  $\overline{\text{MUTE}}$  terminal is asserted low for a minimum of 3 MCLK\_IN cycles. Alternatively, the mute mode can be initiated by setting the mute bit in the system control register through the serial control interface. The TAS5036 is held in mute state as long as the terminal is low or I<sup>2</sup>C mute setting is active. This command uses quiet entry and exit sequences to and from the hard mute state.

If an error recovery (described in the PWM section) occurs after a mute request has been received, the device returns from error recovery with the channel volume set as specified by the mute command.

#### 2.3.3 Auto Mute

Auto mute is an automatic sequence that can be enabled or disabled via the serial control interface. The default for this control is enabled. When enabled, the PWM auto mutes an individual channel when a channel receives from 5 ms to 50 ms of consecutive zeros. This time interval can be selectable using the auto mute delay register. The default interval is 5 ms at 48 kHz. This duration is independent of the sample rate. The auto mute state is exited when two consecutive samples of nonzero data are received.

This mode uses the valid low to provide a low-noise floor while maintaining a short startup time. Noise free entry and exit is achieved by using the PWM quiet start and stop sequences.

#### 2.3.4 Individual Channel Mute

Individual channel mute is invoked through the serial interface. Individual channel mute permits each channel of the TAS5036 to be individually muted and unmuted. The operation that is performed is identical to the mute operation; however, it is performed on a per channel basis. A TAS5036 channel is held in the mute state as long as the serial interface mute setting for that channel is set.

#### 2.3.5 De-Emphasis Filter

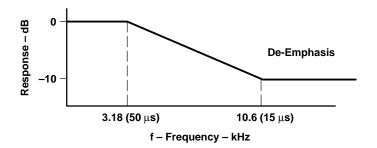

For audio sources that have been pre-emphasized, a precision 50-μs/15-μs de-emphasis filter is provided to support the sampling rates of 32 kHz, 44.1 kHz, and 48 kHz. See Figure 2–11 for a graph showing the de-emphasis filtering characteristics. De-emphasis is set using two bits in the system control register.

Table 2–10. De-Emphasis Filter Characteristics

| DEM_SEL2 (MSB) | DEM_SEL1 | DESCRIPTION                         |

|----------------|----------|-------------------------------------|

| 0              | 0        | De-emphasis disabled                |

| 0              | 1        | De-emphasis enabled for Fs = 48 kHz |

| 1              | 0        | De-emphasis enabled for Fs = 44 kHz |

| 1              | 1        | De-emphasis enabled for Fs = 32 kHz |

Following the change of state of the de-emphasis bits, the PWM outputs go into the soft mute state. After 128 LRCLK periods for initialization, the PWM outputs are driven to the normal (unmuted) mode.

Figure 2-11. De-Emphasis Filter Characteristics

#### 2.4 Pulse Width Modulator (PWM)

The TAS5036 contains six channels of high performance digital Equibit PWM modulators that are designed to drive switching output stages (back ends) in both single-ended (SE) and H-bridge (bridge tied load) configuration. The TAS5036 device uses noise shaping and sophisticated error correction algorithms to achieve high power efficiency and high-performance digital audio reproduction.

The PWM provides six pseudo-differential outputs to drive six monolithic power stages (such as TAS5110) or six discrete differential power stages using gate drivers (such as the TAS5182) and MOSFETs in single-ended or bridged configurations. The TAS5036 also provides a high performance differential output that can be used to drive an external analog headphone amplifier.

#### 2.4.1 Clipping Indicator

The clipping output is designed to indicate clipping. When any of the six PWM outputs exceeds the maximum allowable amplitude, the clipping indicator is asserted. The clipping indicator is cleared every 10 ms.

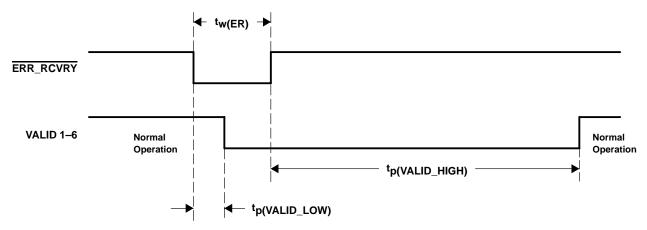

#### 2.4.2 Error Recovery

Error recovery is used to provide error management and to permit the PWM output to be reset while preserving all inter-volume, inter-channel delay, dc offsets, and the other internal settings. Error recovery is initiated by bringing the /ERR\_RCVRY terminal low for a minimum 5 MCLK\_IN cycles or by setting the error recovery bit in control register 1. Error recovery is a level sensitive signal.

The device also performs an error recovery automatically:

- When the speed configuration is changed to normal, double, or quad speed

- Following a change in the serial data bus interface configuration

When ERR\_RCVRY is brought low, all valid signals go low, and the PWM-P and PWM-M outputs go low. If there are any pending speed configurations, these changes are then performed. When ERR\_RCVRY is brought high, a delay of 4 ms to 5 ms is performed before the system starts the output re-initialization sequence. After the initialization time, the TAS5036 begins normal operation. During error recovery, all controls and device settings that were not updated are maintained in their current configurations.

To permit error recovery to be used to provide TAS5100 error management and recovery, the delay between the start of (falling edge) error recovery and the falling edge of valid 1 though valid 6 is selectable. This delay can be selected to be either 6  $\mu$ s or 47  $\mu$ s.

During error recovery all serial data bus operations are ignored. At the conclusion of the sequence, the error recovery register bit is returned to normal operation state. Table 2–11 shows the device output signal states while during error recovery.

Table 2-11. Device Outputs During Error Recovery

| SIGNAL          | MODE   | SIGNAL STATE |

|-----------------|--------|--------------|

| Valid 1-Valid 6 | All    | Low          |

| PWM P-outputs   | All    | Low          |

| PWM M-outputs   | All    | Low          |

| MCLKOUT         | All    | Low          |

| SCLK            | Master | Low          |

| SCLK            | Slave  | Signal input |

| LRCLK           | Master | Low          |

| LRCLK           | Slave  | Signal input |

| SDA             | All    | Signal input |

| CLIP            | All    | High         |

The transitions are done using a quiet entrance and exit sequence to prevent pops and clicks.

#### 2.4.3 Individual Channel Error Recovery

Individual channel error recovery is used to provide error management and to permit the PWM output to be turned off. Error recovery is initiated by setting one or more of the six error recovery bits in the error recovery register to low.

While the error recover bits are brought low, the valid signals goes to the low state. When the error recovery bits are brought high, a delay of 4 ms to 5 ms occurs before the channels are returned to normal operation.

The delay between the falling edge of the error recover bit and the falling edge of valid 1 though valid 6 is selectable. This delay can be selected to be either 6  $\mu$ s or 47  $\mu$ s.

The TAS5036 controls the relative timing of the pseudo-differential drive control signals plus the valid signal to minimize the production of system noise during error recovery operations. The transitions to valid low and valid high are done using an almost quiet entrance and exit sequence to prevent pops and clicks.

#### 2.4.4 PWM DC-Offset Correction

An 8-bit value can be programmed to each of the six PWM offset correction registers to correct for any offset present in the output stages. The offset correction is divided into 256 intervals with a total offset correction of  $\pm 1.56\%$  of full scale. The default value is zero correction represented by 00 (hex). These values can be changed at any time through the serial control interface.

#### 2.4.5 Inter-Channel Delay

An 8-bit value can be programmed to each of the six PWM inter-channel delay registers to add a delay per channel from 0 to 255 clock cycles. The delays correspond to cycles of the high-speed internal clock, DCLK (or alternatively the external PLL clock frequency). Each subsequent channel has a default value that is N DCLKs larger than the preceding channel. The default values are 0 for the first channel and 16 for each successive channel.

These values can be updated upon power up through the serial control interface. This delay is generated in the PWM block with the appropriate control signals generated in the CTL block.

These values can be changed at any time through the serial control interface. The optimum performance of the TAS5036 can be achieved using an interchannel delay of 21.

#### 2.4.6 ABD Delay

A 5-bit value is used to delay the A PWM signals with respect to B PWM signals. The value is the same for all channels. It can be programmed from 0 to 31 DCLK clock cycles. The default values is 11 DCLK clock cycles (01011). This value is mask programmable. These values can be changed at any time through the serial control interface.

The optimum performance of the TAS5036 can be achieved with an ABD delay of 30.

#### 2.4.7 PWM/H-Bridge and Discrete H-Bridge Driver Interface

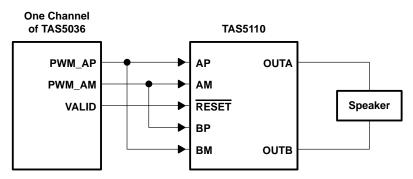

The TAS5036 provides six PWM outputs, which are designed to drive switching output stages (back-ends) in both single-ended (SE) and H-bridge (bridge tied load) configuration. The back-ends may be monolithic power stages (such as the TAS5110) or six discrete differential power stages using gate drivers (such as the TAS55182) and MOSFETs in single-ended or bridged configurations.

The TAS5110 device is optimised for bridge tied load (BTL) configurations. These devices require a pure differential PWM signal with a third signal (VALID) to control the MUTE state. In the MUTE state, the TAS5110 OUTA and OUTB are both low.

Figure 2-12. PWM Outputs and H-Bridge Driven in BTL Configuration

#### 2.5 I<sup>2</sup>C Serial Control Interface

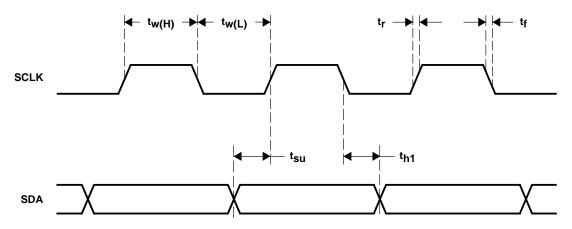

The TAS5036 has a bidirectional serial control interface that is compatible with the I<sup>2</sup>C (Inter IC) bus protocol and supports both 100 KBPS and 400 KBPS data transfer rates for single and multiple byte write and read operations. This is a slave only device that does not support a multi-master bus environment or wait state insertion. The control interface is used to program the registers of the device and to read device status.

The TAS5036 supports the standard-mode  $I^2C$  bus operation (100 kHz maximum) and the fast  $I^2C$  bus operation (400 kHz maximum). The TAS5036 performs all  $I^2C$  operations without  $I^2C$  wait cycles.

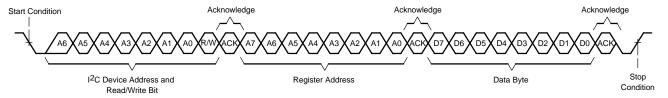

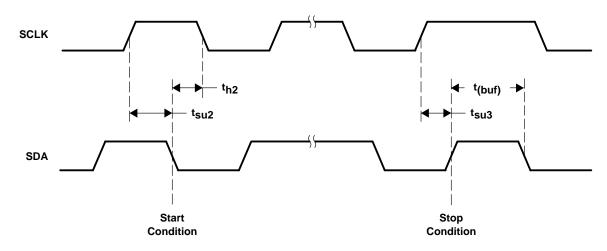

The I<sup>2</sup>C bus employs two signals; SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially one bit at a time. The address and data are transferred in byte (8 bit) format with the most significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is high to indicate a start and stop conditions. A high-to-low transition on SDA indicates a start, and a low-to-high transition indicates a stop. Normal data bit transitions must occur within the low time of the clock period. These conditions are shown in Figure 2–13. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The TAS5036 holds SDA low during acknowledge clock period to indicate an acknowledgement. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. I<sup>2</sup>C An external pullup resistor must be used for the SDA and SCL signals to set the high level for the bus.

Figure 2-13. Typical I<sup>2</sup>C Sequence

There are no limits on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is also shown in Figure 2–13.

The 7-bit address for the TAS5036 is 001101X, where X is a programmable address bit. Using the CS0 terminal on the device, the LSB address bit is programmable to permit two devices to be used in a system. These two addresses are licensed I<sup>2</sup>C addresses and do not conflict with other licensed I<sup>2</sup>C audio devices. To communicate with the TAS5036, the I<sup>2</sup>C master uses 0011010 if CS0=0 and 0011011 if CS0=1. In addition to the 7-bit device address, an 8-bit register address is used to direct communication to the proper register location within the device interface.

Read and write operations to the TAS5036 can be done using single byte or multiple byte data transfers.

#### 2.5.1 Single Byte Write

As shown in Figure 2–14, a single byte data write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a write data transfer, the read/write bit is 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the TAS5036 device responds with an acknowledge bit. Next, the master transmits the address byte or bytes corresponding to the TAS5036 internal memory address being accessed. After receiving the address byte, the TAS5036 again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the data byte, the TAS5036 again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single byte data write transfer.

Figure 2–14. Single Byte Write Transfer

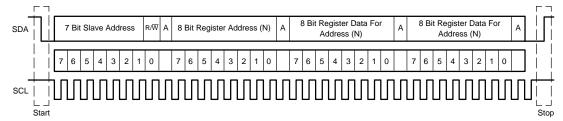

#### 2.5.2 Multiple Byte Write

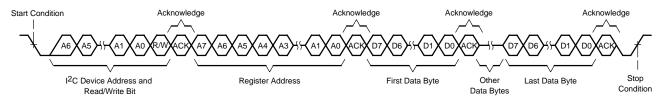

A multiple byte data write transfer is identical to a single byte data write transfer except that multiple data bytes are transmitted by the master device to TAS5036 as shown in Figure 2–15. After receiving each data byte, the TAS5036 responds with an acknowledge bit.

Figure 2-15. Multiple Byte Write Transfer

#### 2.5.3 Single Byte Read

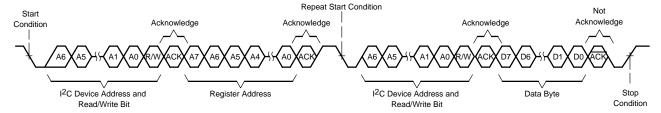

As shown in Figure 2–16, a single byte data read transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. For the data read transfer, a write followed by a read are actually done. Initially, a write is done to transfer the address byte or bytes of the internal memory address to be read. As a result, the read/write bit is 0. After receiving the TAS5036 address and the read/write bit, the TAS5036 responds with an acknowledge bit. Also, after sending the internal memory address byte or bytes, the master device transmits another start condition followed by the TAS5036 address and the read/write bit again. This time the read/write bit is a 1 indicating a read transfer. After receiving the TAS5036 and the read/write bit, the TAS5036 again responds with an acknowledge bit. Next, the TAS5036 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not acknowledge followed by a stop condition to complete the single byte data read transfer.

Figure 2-16. Single Byte Read

#### 2.5.4 Multiple Byte Read

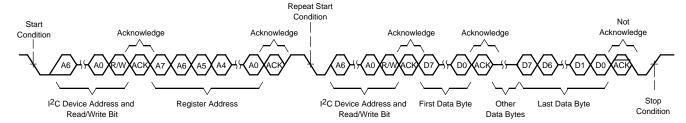

A multiple byte data read transfer is identical to a single byte data read transfer except that multiple data bytes are transmitted by the TAS5036 to the master device as shown in Figure 2–17. Except for the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

Figure 2-17. Multiple Byte Read

#### 3 Serial Control Interface Register Definitions

Table 3–1 shows the register map for the TAS5036. Default values in this section are in bold.

Table 3–1. I<sup>2</sup>C Register Map

| ADDR HEX | DESCRIPTION                           |

|----------|---------------------------------------|

| 00       | General status register               |

| 01       | Error status register                 |

| 02       | System control register 0             |

| 03       | System control register 1             |

| 04       | Error recovery register               |

| 05       | Automute delay                        |

| 06       | DC-offset control register channel 1  |

| 07       | DC-offset control register channel 2  |

| 08       | DC-offset control register channel 3  |

| 09       | DC-offset control register channel 4  |

| 0A       | DC-offset control register channel 5  |

| 0B       | DC-offset control register channel 6  |

| 0C       | Interchannel delay register channel 1 |

| 0D       | Interchannel delay register channel 2 |

| 0E       | Interchannel delay register channel 3 |

| 0F       | Interchannel delay register channel 4 |

| 10       | Interchannel delay register channel 5 |

| 11       | Interchannel delay register channel 6 |

| 12       | ABD delay register                    |

| 13       | Volume control register channel 1     |

| 14       | Volume control register channel 2     |

| 15       | Volume control register channel 3     |

| 16       | Volume control register channel 4     |

| 17       | Volume control register channel 5     |

| 18       | Volume control register channel 6     |

| 19       | Individual channel mute               |

The volume table is contained in Appendix A.

Default values are shown in bold in the following tables

#### NOTE:

The performance of a TDAA system is optimized by setting the PWM timing based upon the type of back-end device that is used and, to a lesser extent, the layout. These values are set during initialization using the I<sup>2</sup>C serial interface. The specific timing parameter values for each PWM and back-end configuration is contained in the EVM User Manual, Reference Design User Manual, and design application note for these devices. Please refer to the appropriate EVM User Manual, Reference Design user manual, or design application note for these values.

#### 3.1 General Status Register (x00)

Table 3-2. General Status Register (Read Only)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | FUNCTION                                                               |

|----|----|----|----|----|----|----|----|------------------------------------------------------------------------|

| 0  | -  | -  | -  | -  | -  | -  | -  | No volume update is in progress.                                       |

| 1  | -  | -  | ı  | -  | ı  | -  | -  | Volume update is in progress.                                          |

| -  | 0  |    |    |    | •  | -  | -  | Always 0                                                               |