# **TAS3002** Digital Audio Processor With Codec

Digital Audio: Digital Speakers

# **1** Introduction

# 1.1 Description

The TAS3002 device is a system-on-a-chip that replaces conventional analog equalization to perform digital parametric equalization, dynamic range compression, and loudness contour. Additionally, this device provides high-quality, soft digital volume, bass, and treble control. All control parameters are uploaded from an outside MCU through the I<sup>2</sup>C slave port or from an external EEPROM through the I<sup>2</sup>C master port.

The TAS3002 device also has an integrated 24-bit stereo codec with two I<sup>2</sup>C-selectable, single-ended inputs per channel.

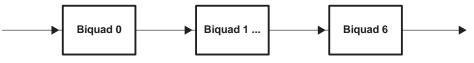

The digital parametric equalization consists of seven cascaded, independent biquad filters per channel. Each biquad filter has five 24-bit coefficients that can be configured into many different filter functions (such as band-pass, high-pass, and low-pass).

The internal loudness contour algorithm can be controlled and programmed with an I<sup>2</sup>C command.

Dynamic range compression/expansion (DRCE) is programmable through the I<sup>2</sup>C port. The system designer can set the threshold, energy estimation time constant, compression ratio, and attack and decay time constants.

The TAS3002 device supports 13 serial interface formats ( $I^2S$ , left justified, right justified) with data word lengths of 16, 18, 20, or 24 bits. The sampling frequency ( $f_S$ ) may be set to 32 kHz, 44.1 kHz, or 48 kHz. The 13 serial interface formats are listed and described in Section 2.1.

The TAS3002 device uses a system clock generated by the internal phase-locked loop (PLL). The reference clock for the PLL is provided by an external master clock (MCLK) of 256f<sub>S</sub> or 512f<sub>S</sub>, or a 256f<sub>S</sub> crystal.

The TAS3002 device has six internally configurable general-purpose input (GPI) terminals that control volume, bass, treble, and equalization. Each GPI terminal has a debounce algorithm that is programmed into the TAS3002 internal microcontroller.

#### 1.2 Features

- Programmable seven-band parametric equalization

- Programmable digital volume control

- Programmable digital bass and treble control

- Programmable dynamic range compression/expansion (DRCE)

- Programmable loudness contour/dynamic bass control

- Configurable serial port for audio data

- Two input data channels that can be mixed with digital data from the analog-to-digital converter (ADC) of the codec (analog input). These channels are controlled by I<sup>2</sup>C commands.

- Three output data channels: Left and right data go through equalization; bass, treble, DRCE, and volume to SDOUT1; SDOUT2 mixes left and right data. SDOUT2 operates as a center channel or subwoofer channel. The output of the ADC is available for additional processing.

- Capability to digitally mix left and right input channels for a monaural output to facilitate subwoofer operation

- Serial I<sup>2</sup>C master/slave port that allows:

- Downloading of control data to the device externally from the EEPROM or an I<sup>2</sup>C master

- Controlling other I<sup>2</sup>C devices

- Two I<sup>2</sup>C-selectable, single-ended analog input stereo channels

- Equalization bypass mode

- Single 3.3-V power supply

- Power down without reloading the coefficients

- Sampling rates of 32 kHz, 44.1 kHz, or 48 kHz

- Master clock frequency of 256f<sub>S</sub> or 512f<sub>S</sub>

- Can have crystal input to replace MCLK. Crystal input frequency is 256 fs.

- Six GPI terminals for volume, bass, treble up/down control, mute, and selection of equalization filters

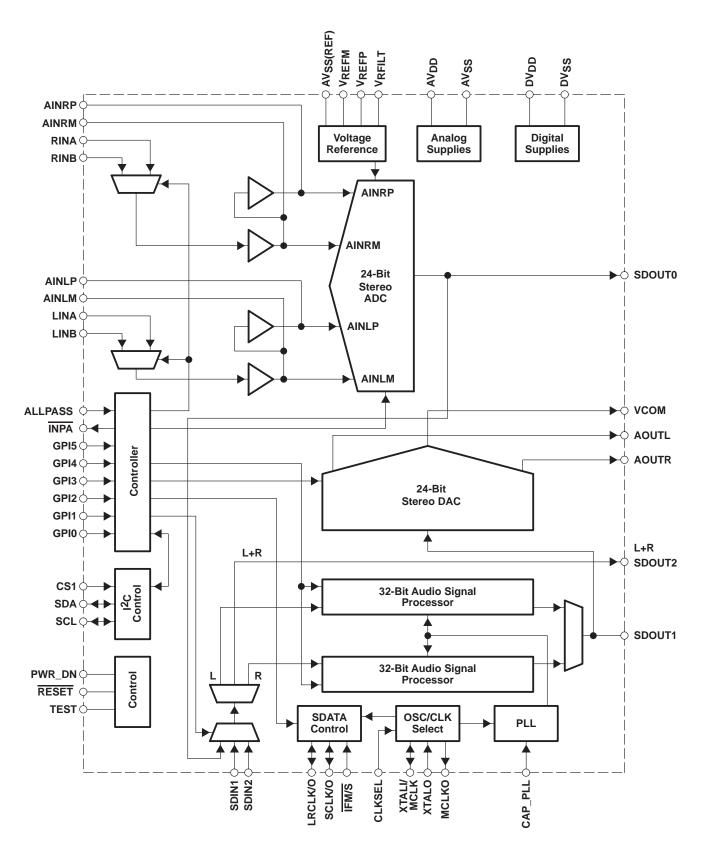

# 1.3 Functional Block Diagram

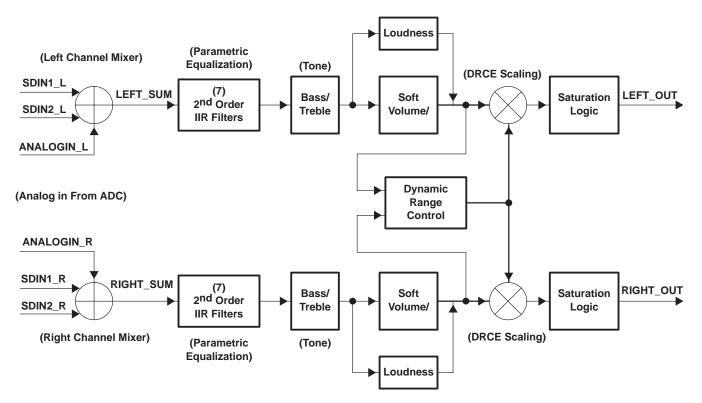

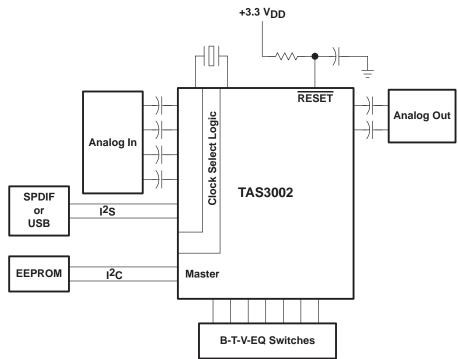

Figure 1–1 is a block diagram showing the major functions of the TAS3002.

Figure 1–1. TAS3002 Block Diagram

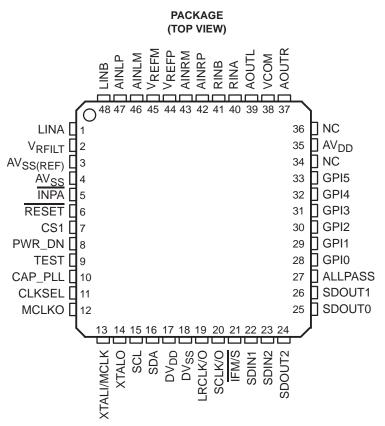

# 1.4 Terminal Assignments

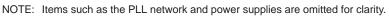

Figure 1–2 shows the terminal locations on the package outline, along with the signal name assigned to each terminal.

Figure 1–2. TAS3002 Terminal Assignments

#### **1.5 Terminal Functions**

Table 1–1 lists the terminals in alphanumeric order by signal name, along with the terminal number, terminal type, and a description of the terminal function.

| TERMINAL  |     | 1/0 | DECODIPTION                                          |  |  |  |  |

|-----------|-----|-----|------------------------------------------------------|--|--|--|--|

| NAME      | NO. | I/O | DESCRIPTION                                          |  |  |  |  |

| AINLM     | 46  | Ι   | ADC left channel analog input (antialias capacitor)  |  |  |  |  |

| AINLP     | 47  | Ι   | ADC left channel analog input (antialias capacitor)  |  |  |  |  |

| AINRM     | 43  | Ι   | ADC right channel analog input (antialias capacitor) |  |  |  |  |

| AINRP     | 42  | Ι   | ADC right channel analog input (antialias capacitor) |  |  |  |  |

| ALLPASS   | 27  | Ι   | Logic high bypasses equalization filters             |  |  |  |  |

| AOUTL     | 39  | 0   | Left channel analog output                           |  |  |  |  |

| AOUTR     | 37  | 0   | Right channel analog output                          |  |  |  |  |

| AVDD      | 35  | Ι   | Analog power supply (3.3 V)                          |  |  |  |  |

| AVSS      | 4   | I   | Analog voltage ground                                |  |  |  |  |

| AVSS(REF) | 3   | I   | nalog ground voltage reference                       |  |  |  |  |

Table 1–1. TAS3002 Terminal Functions

| TERMINAL          |          |     |                                                                                                                             |  |  |  |  |

|-------------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME              | NO.      | I/O | DESCRIPTION                                                                                                                 |  |  |  |  |

| CAP_PLL           | 10       | Ι   | Loop filter for internal phase-locked loop (PLL)                                                                            |  |  |  |  |

| CLKSEL            | 11       | Ι   | Logic low selects 256 fs; logic high selects 512 fs MCLK                                                                    |  |  |  |  |

| CS1               | 7        | I   | $I^2C$ address bit A0; low = 68h, high = 6Ah                                                                                |  |  |  |  |

| DV <sub>DD</sub>  | 17       | I   | Digital power supply (3.3 V)                                                                                                |  |  |  |  |

| DVSS              | 18       | 1   | Digital ground                                                                                                              |  |  |  |  |

| GPI0              | 28       |     | Switch input terminals                                                                                                      |  |  |  |  |

| GPI1              | 29       |     |                                                                                                                             |  |  |  |  |

| GPI2              | 30       |     |                                                                                                                             |  |  |  |  |

| GPI3<br>GPI4      | 31<br>32 |     |                                                                                                                             |  |  |  |  |

| GPI5              | 32       |     |                                                                                                                             |  |  |  |  |

| IFM/S             | 21       | I   | Digital audio I/O control (low = input; high = output)                                                                      |  |  |  |  |

| INPA              | 5        | 0   | Low when analog input A is selected (will sink 4 mA)                                                                        |  |  |  |  |

| LINA              | 1        | I   | Left channel analog input 1                                                                                                 |  |  |  |  |

| LINB              | 48       | Ι   | Left channel analog input 2                                                                                                 |  |  |  |  |

| LRCLK/O           | 19       | I/O | Left/right clock input/output (output when IFM/S is high)                                                                   |  |  |  |  |

| MCLKO             | 12       | 0   | MCLK output for slave devices                                                                                               |  |  |  |  |

| NC                | 34       |     | No connection; Can be used as a printed circuit board routing channel                                                       |  |  |  |  |

| NC                | 36       |     | No connection; Can be used as a printed circuit board routing channel                                                       |  |  |  |  |

| PWR_DN            | 8        | Ι   | Logic high places the TAS3002 device in power-down mode                                                                     |  |  |  |  |

| RESET             | 6        | Ι   | Logic low resets the TAS3002 device to the initial state                                                                    |  |  |  |  |

| RINA              | 40       | Ι   | Right channel analog input 1                                                                                                |  |  |  |  |

| RINB              | 41       | Ι   | Right channel analog input 2                                                                                                |  |  |  |  |

| SCL               | 15       | I/O | I <sup>2</sup> C clock connection                                                                                           |  |  |  |  |

| SCLK/O            | 20       | I/O | Shift (bit) clock input (output when IFM/S is high)                                                                         |  |  |  |  |

| SDA               | 16       | I/O | I <sup>2</sup> C data connection                                                                                            |  |  |  |  |

| SDIN1             | 22       | Ι   | Serial data input 1                                                                                                         |  |  |  |  |

| SDIN2             | 23       | I   | Serial data input 2                                                                                                         |  |  |  |  |

| SDOUT0            | 25       | 0   | Serial data output from ADC                                                                                                 |  |  |  |  |

| SDOUT1            | 26       | 0   | Serial data output (from internal audio processing)                                                                         |  |  |  |  |

| SDOUT2            | 24       | 0   | Serial data output (a monaural mix of left and right, before processing)                                                    |  |  |  |  |

| TEST              | 9        | Ι   | Reserved manufacturing test terminal; connect to DV <sub>SS</sub>                                                           |  |  |  |  |

| VCOM              | 38       | 0   | Digital-to-analog converter mid-rail supply (decouple with parallel combination of 10- $\mu$ F and 0.1- $\mu$ F capacitors) |  |  |  |  |

| VREFM             | 45       | Ι   | ADC minus voltage reference                                                                                                 |  |  |  |  |

| V <sub>REFP</sub> | 44       | I   | ADC plus voltage reference                                                                                                  |  |  |  |  |

| VRFILT            | 2        | 0   | Voltage reference low pass filter                                                                                           |  |  |  |  |

| XTALI/MCLK        | 13       | I   | Crystal or external MCLK input                                                                                              |  |  |  |  |

| XTALO             | 14       | Ι   | Crystal input (crystal is connected between terminals 13 and 14)                                                            |  |  |  |  |

## Table 1–1. TAS3002 Terminal Functions (Continued)

# 2 Audio Data Formats

## 2.1 Serial Interface Formats

The TAS3002 device works in master or slave mode.

In the master mode, terminal 21 (IFM/S) is tied high. This activates the master clock (MCLK) circuitry. A crystal can be connected across terminals 13 (XTALI/MCLK) and 14 (XTALO), or an external, TTL-compatible MCLK can be connected to XTALI/MCLK. In that case, MCLK is outputs on terminal 12 (MCLKO), with terminals 19 (LRCLK/O) and 20 (SCLK/O) becoming outputs to drive slave devices.

In the slave mode,  $\overline{IFM/S}$  is tied low. LRCLK/O and SCLK/O are inputs and the interface operates as a slave device requiring externally supplied MCLK, LRCLK (left/right clock), and SCLK (shift clock) inputs. There are two options for selecting the clock rates. If the 512f<sub>S</sub> MCLK rate is selected, terminal 11 (CLKSEL) is tied high and an MCLK rate of 512f<sub>S</sub> must be supplied. If the 256f<sub>S</sub> MCLK is selected, CLKSEL is tied low and an MCLK of 256f<sub>S</sub> must be supplied. In both cases, an LRCLK of 64 SCLK must be supplied.

- MCLK and SCLK must be synchronous and their edges must be at least 3 ns apart.

- If the LRCLK phase changes by more than 10 cycles of MCLK, the codec automatically resets.

The TAS3002 device is compatible with 13 different serial interfaces. Available interface options are  $I^2S$ , right justified, and left justified. Table 2–1 indicates how the 13 options are selected using the  $I^2C$  bus and the main control register (MCR,  $I^2C$  address 01h). All serial interface options at either 16, 18, 20, or 24 bits operate with SCLK at  $64f_S$ . Additionally, the 16-bit mode operates at  $32f_S$ .

| MODE | MCR BIT (6) | MCR BIT (5-4) | MCR BIT (1-0) | SERIAL INTERFACE<br>SDIN1, SDIN2, SDOUT1, SDOUT2, AND SDOUT0 |

|------|-------------|---------------|---------------|--------------------------------------------------------------|

| 0    | 0           | 00            | 00            | 16-bit, 32fS                                                 |

| 1    | 1           | 00            | 00            | 16-bit, left justified, 64 fs                                |

| 2    | 1           | 01            | 00            | 16-bit, right justified, 64fS                                |

| 3    | 1           | 10            | 00            | 16-bit, I <sup>2</sup> S, 64f <sub>S</sub>                   |

| 4    | 1           | 00            | 01            | 18-bit, left justified, 64 fS                                |

| 5    | 1           | 01            | 01            | 18-bit, right justified, 64fS                                |

| 6    | 1           | 10            | 01            | 18-bit, I <sup>2</sup> S, 64f <sub>S</sub>                   |

| 7    | 1           | 00            | 10            | 20-bit, left justified, 64 f <sub>S</sub>                    |

| 8    | 1           | 01            | 10            | 20-bit, right justified, 64fs                                |

| 9    | 1           | 10            | 10            | 20-bit, I <sup>2</sup> S, 64f <sub>S</sub>                   |

| 10   | 1           | 00            | 11            | 24-bit, left justified, 64 fS                                |

| 11   | 1           | 01            | 11            | 24-bit, right justified, 64f <sub>S</sub>                    |

| 12   | 1           | 10            | 11            | 24-bit, I <sup>2</sup> S, 64f <sub>S</sub>                   |

| Table 2–1. | Serial | Interface | Options |

|------------|--------|-----------|---------|

|            | Ochai  | menace    | options |

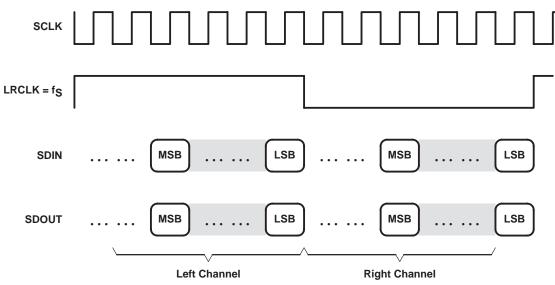

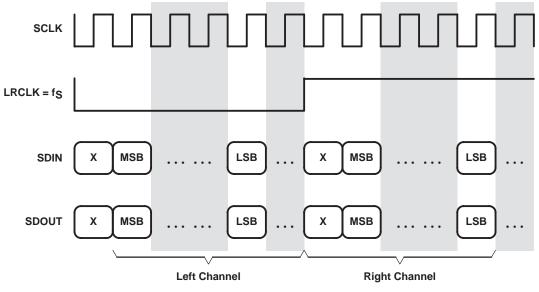

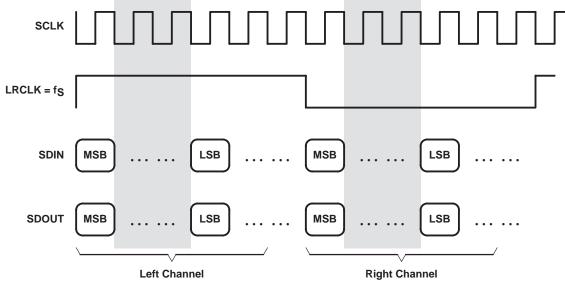

Figure 2–1 through Figure 2–3 illustrate the relationship between the SCLK, LRCLK, and the serial data I/O for the different interface protocols.

# 2.2 Digital Output Modes

The digital output modes (SDOUT1, SDOUT2, SDOUT0) are described in Sections 2.2.1 through 2.2.3.

#### 2.2.1 MSB-First, Right-Justified, Serial-Interface Format

The normal output mode for the MSB-first, right-justified, serial-interface format is for 16, 18, 20, or 24 bits. Figure 2–1 shows the following characteristics of this protocol:

- Left channel is transmitted when LRCLK is high.

- The SDIN(s) (recorded) data is justified to the trailing edge of the LRCLK.

- The SDOUT(s) MSB (playback) data is transmitted at the same time as LRCLK edge and captured at the next rising edge of SCLK.

- If the LRCLK phase changes by more than 10 cycles of MCLK, the codec automatically resets.

Figure 2–1. MSB-First, Right-Justified, Serial-Interface Format

## 2.2.2 I<sup>2</sup>S Serial-Interface Format

The normal output mode for the I<sup>2</sup>S serial-interface format is for 16, 18, 20, or 24 bits.

Figure 2–2 shows the following characteristics of this protocol:

- Left channel is transmitted when LRCLK is low.

- SDIN is sampled with the rising edge of SCLK.

- SDOUT is transmitted on the falling edge of SCLK.

- If the LRCLK phase changes by more than 10 cycles of MCLK, the codec automatically resets.

Figure 2–2. I<sup>2</sup>S Serial-Interface Format

#### 2.2.3 MSB-Left-Justified, Serial-Interface Format

The normal output mode for the MSB-left-justified, serial-interface format is for 16, 18, 20, or 24 bits.

Figure 2–3 shows the following characteristics of this protocol:

- Left channel is transmitted when LRCLK is high.

- The SDIN data is justified to the leading edge of the LRCLK.

- The MSBs are transmitted at the same time as LRCLK edge and captured at the next rising edge of SCLK.

Figure 2–3. MSB-Left-Justified, Serial-Interface Format

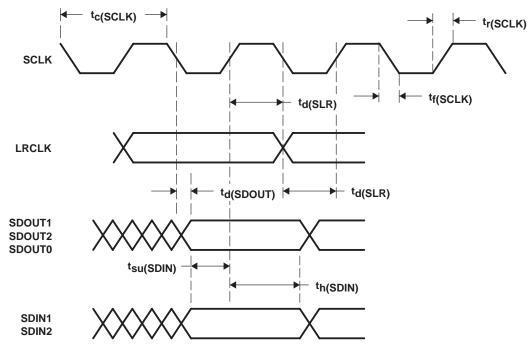

# 2.3 Switching Characteristics

|                        | PARAMETER                                       | MIN   | TYP  | MAX                         | UNIT |

|------------------------|-------------------------------------------------|-------|------|-----------------------------|------|

| tc(SCLK)               | SCLK cycle time                                 | 325.5 |      |                             | ns   |

| <sup>t</sup> d(SLR)    | SCLK rising to LRCLK edge                       | 20    |      |                             | ns   |

| td(SDOUT)              | SDOUT valid from SCLK falling edge (see Note 1) |       |      | (1/256f <sub>S</sub> ) + 10 | ns   |

| t <sub>su</sub> (SDIN) | SDIN setup before SCLK rising edge              | 20    |      |                             | ns   |

| <sup>t</sup> h(SDIN)   | SDIN hold after SCLK rising edge                | 100   |      |                             | ns   |

| f(LRCLK)               | LRCLK frequency                                 | 32    | 44.1 | 48                          | kHz  |

|                        | Duty cycle                                      |       | 50   |                             | %    |

NOTE 1: Maximum of 50-pF external load on SDOUT.

Figure 2–4. For Right-/Left-Justified and I<sup>2</sup>S Serial Protocols

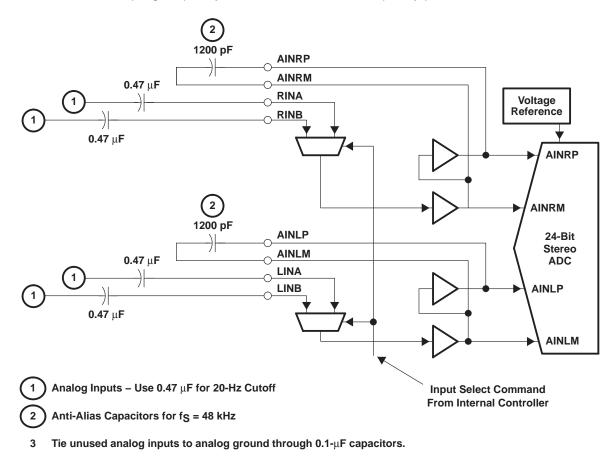

# 3 Analog Input/Output

The TAS3002 device contains a stereo 24-bit ADC with two single-ended inputs per channel. Selection of the A or B analog input is accomplished by setting a bit in the analog control register (ACR) by an I<sup>2</sup>C command. Additionally, the TAS3002 device has a stereo 24-bit digital-to-analog converter (DAC).

# 3.1 Analog Input

Figure 3–1 shows the technique and components required for analog input to the TAS3002 device. The maximum input signal must not exceed 0.7  $V_{rms}$ . Selection of the above component values gives a frequency response from 20 Hz to 20 kHz at a sampling frequency of 48 kHz without alias frequency problems.

Figure 3–1. Analog Input to the TAS3002 Device

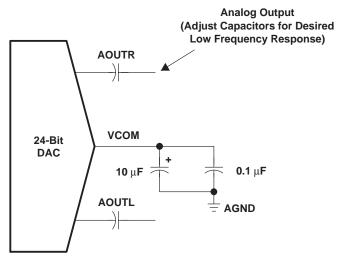

# 3.2 Analog Output

#### 3.2.1 Direct Analog Output

The full scale analog output from the TAS3002 device is 0.707  $V_{rms}$ . It is referenced to VCOM which is approximately 1.5 Vdc. VCOM must be decoupled with the network shown in Figure 3–2.

Figure 3–2. VCOM Decoupling Network

#### 3.2.2 Analog Output With Gain

Because the maximum analog output from the TAS3002 device is 0.707  $V_{rms}$ , the output level can be increased by using an external amplifier. The circuit shown in Figure 3–3 boosts the output level to 1  $V_{rms}$  (when it has a gain of 1.414) and provides improved signal-to-noise ratio (SNR). Since this circuit lowers the noise floor, THD + N is improved also.

Figure 3–3. Analog Output With External Amplifier

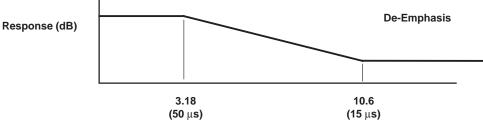

# 3.2.3 Reference Voltage Filter

Figure 3–4 shows the TAS3002 reference voltage filter.

Figure 3–4. TAS3002 Reference Voltage Filter

# **4 Audio Control/Enhancement Functions**

# 4.1 Soft Volume Update

The TAS3002 device implements a TI proprietary soft volume update. This feature allows a smooth and pleasant-sounding change from one volume level to another over the entire range of volume control (18 dB to mute).

The volume is adjustable by downloading a gain coefficient through the  $I^2C$  interface in 4.16 format—4 bits for the integer and 16 bits for the fractional part. NO TAG lists the 4.16 coefficients converted into dB for the range of -70 dB to 18 dB with 0.5-dB step resolution.

Right and left channel volumes can be unganged and set to different values. This feature implements a balance control.

Volume is changed by writing the desired value into the volume control registers. This is done by asserting the volume-up or volume-down GPI terminal (see Section 7.6.1) for a limited range of volume control. Alternatively, volume control settings can be sent to the TAS3002 device over the I<sup>2</sup>C bus.

# 4.2 Software Soft Mute

Soft mute is implemented by loading all zeros in the volume control register. This causes the volume to ramp down over a duration of 2048f<sub>S</sub> samples to a final output of 0 (– infinity dB).

Soft mute can be enabled by either asserting the mute GPI terminal (see Section 7.6.1) or sending a mute command over the  $I^2C$  bus. Subsequent assertions of the mute GPI terminal toggle soft mute off and on.

#### 4.3 Input Mixer Control

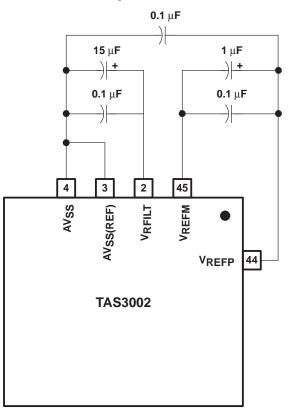

The TAS3002 device is capable of mixing and multiplexing three channels (SDIN1, SDIN2, and the ADC output) of serial audio data. The mixing is controlled through three mixer control registers. This is accomplished by loading values into the corresponding bytes of the mixer left gain (07h) and mixer right gain (08h) control registers. See Figure 4–1 for a functional block diagram of the input mixer.

The values loaded into these registers are in 4.20 format—4 bits for the integer and 20 bits for the fractional part. NO TAG lists the 4.20 numbers converted into dB for the range of -70 dB to 18 dB, although any positive 4.20 number may be used.

To mute any of the channels, 0s are loaded into the respective mixer control register.

Mixer controls are updated instantly and can cause audible artifacts for large changes in setting when updated dynamically outside of the fast load mode; therefore, it is desirable to use fast load in conjunction with the soft-volume mode.

SDIN1, SDIN2, and the ADC output can be mixed with a user-selectable gain for each channel. The gain control registers are represented in 4.20 format.

Figure 4–1. TAS3002 Mixer Function

# 4.4 Mono Mixer Control

The TAS3002 device contains a second mixer that performs the function of mixing left and right channel digital audio data from the input mixer in order to derive a monaural channel. This mixer has a fixed gain of -6 dB so that full scale inputs on L\_sum and R\_sum do not produce clipping on the resulting L+R\_sum.

The output of this mixer is present on terminal 24 (SDOUT2) and is generally used for a digitally-mixed subwoofer or center channel application.

# 4.5 Treble Control

The treble gain level may be adjusted within the range of 15 dB to -15 dB with 0.5-dB step resolution. The level changes are accomplished by downloading treble codes (shown in NO TAG) into the treble gain register. Alternatively, a limited range of treble control is available by asserting the treble-up or treble-down GPI terminal (see Section 7.6.1).

The treble control has a corner frequency of 6 kHz at a 48-kHz sample rate.

The gain values for treble control can be found in Section NO TAG.

# 4.6 Bass Control

The bass gain level can be adjusted within the range of 15 dB to -15 dB with 0.5-dB step resolution. The level changes are accomplished by downloading bass codes (shown in NO TAG) into the bass frequency control register. Alternatively, a limited range of bass control is available by asserting the bass-up or bass-down GPI terminal (see Section 7.6.1).

Bass control is a shelf filter with a corner frequency of 250 Hz at a 48-kHz sample rate.

The gain values for bass control can be found in Section NO TAG.

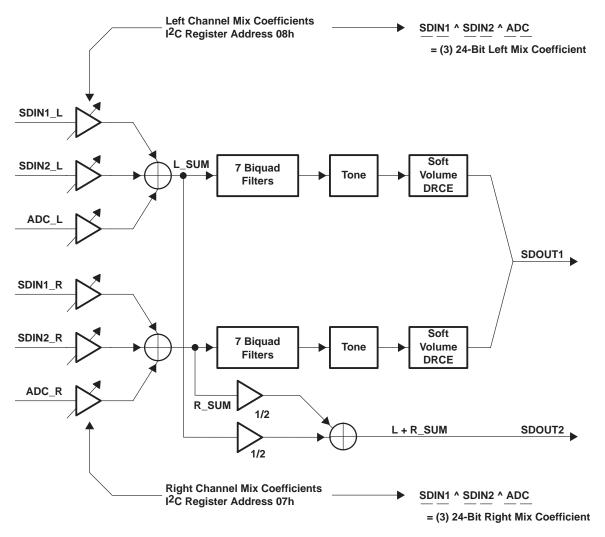

# 4.7 De-Emphasis Mode (DM)

De-emphasis is implemented in the DAC and is software controlled. De-emphasis is valid at 44.1 kHz and 48 kHz.

To enable de-emphasis, values are written into the analog control register via the I<sup>2</sup>C command. See Section 4.8 for analog control register operation.

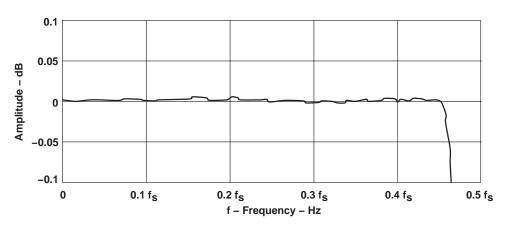

Figure 4–2 illustrates the frequency response of the de-emphasis mode.

Frequency (kHz)

Figure 4–2. De-Emphasis Mode Frequency Response

# 4.8 Analog Control Register (40h)

The analog control register (ACR) allows control of de-emphasis, selection of the analog input channel to the ADC, and analog power down.

An I<sup>2</sup>C master is required to write the appropriate command into the ACR. The ACR subaddress is 40h.

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Туре    | R/W |

| Default | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| BIT | FIELD NAME | TYPE | DESCRIPTION                                                                                                                                                             |

|-----|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved   | R/W  | Reset to 0                                                                                                                                                              |

| 6   | Reserved   | R/W  | Reset to 0                                                                                                                                                              |

| 5–4 | Reserved   | R/W  | Reserved. Bits 5 and 4 return 0s when read.                                                                                                                             |

| 3–2 | DM(1-0)    | R/W  | De-emphasis control                                                                                                                                                     |

|     |            |      | 00 = De-emphasis off (initial condition after reset)<br>01 = 48 kHz sample rate de-emphasis selected<br>10 = 44.1 kHz sample rate de-emphasis selected<br>11 = Reserved |

| 1   | INP        | R/W  | Analog input select                                                                                                                                                     |

|     |            |      | 0 = LINA and RINA selected (initial condition after reset)<br>1 = LINB and RINB selected                                                                                |

| 0   | APD        | R/W  | Analog power down                                                                                                                                                       |

|     |            |      | 0 = Normal operation (initial condition after reset)<br>1 = Power down                                                                                                  |

# Table 4–1. Analog Control Register Description

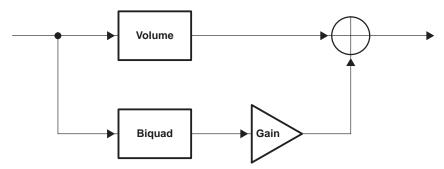

# 4.9 Dynamic Loudness Contour

The necessity for applying loudness compensation to playback systems to compensate for the fact that the ear perceives bass and treble less audibly at low levels than at high ones has been established since the first data was published by Fletcher and Munson in 1933.

There are many equal-loudness contours in publication, like Steven's contours, Robinson and Dadson contours. Some have even reached the acceptance level of ISO recommendation.

The TAS3002 device has a simplified loudness contour algorithm that diminishes the effect of weak bass at low listening levels. Since contour has volume level dependency, the user must define the relation between the gain of the contour circuit and the volume level.

Figure 4–3 is a block diagram of this circuit.

Figure 4–3. Dynamic Loudness Contour Block Diagram

The loudness contour is activated by sending an activation command via I<sup>2</sup>C from an external device. Optionally, a contour gain command can be sent by an external device to provide tracking with the system volume control.

#### 4.9.1 Loudness Biquads

Loudness biquad filters for the left and right channels are independently programmable via I<sup>2</sup>C. Their subaddresses are 21h and 22h, respectively. The digital filters are written as five 24-bit (4.20) hex coefficients for each channel.

#### 4.9.2 Loudness Gain

Loudness gain values for the left and right channels are independently programmable via I<sup>2</sup>C. Their subaddresses are 23h and 24h, respectively. The gain values are written as one 4.20 hex coefficient for each channel.

#### 4.9.3 Loudness Contour Operation

When the frequency of the loudness contour is determined, a digital filter must be developed. Then, the gain of the filter is determined. These values are placed in the storage area of the system controller (microcontroller) and sent to the TAS3002 device when it is desired to activate the loudness contour.

If it is necessary to change the frequency or gain of the contour, new gain and filter coefficients are sent by the system controller. This function is performed normally when the volume control is changed (that is, more volume, less contour). The gain of the loudness contour filter then tracks the volume control.

The loudness contour biquad filters are provided in addition to the seven equalization biquad filters.

See Section NO TAG for programming instructions.

# 4.10 Dynamic Range Compression/Expansion (DRCE)

The TAS3002 device provides the user with the ability to manage the dynamic range of the audio system. The DRCE receives data, and affects scaling after the volume/loudness block. As shown in Figure 4–4, the DRCE is applied after the volume/loudness control block as a DRCE scale factor. The DRCE must be adjusted such that the signal does not reach the hard limit value. However, if the signal does reach the maximum digital value, the saturation logic serves as a hard limiter that does not allow the signal to extend beyond the available range.

Figure 4–4. TAS3002 Digital Signal Processing Block Diagram

The DRCE instruction consists of eight bytes that must be sent each time in the order shown in the example code of NO TAG. Each instruction downloaded must be eight bytes. If only one byte is changed, all eight bytes must be transmitted. The first two bytes remain the same for every instruction, however the last six bytes can be programmed using hexadecimal values from the corresponding tables referred to in Section NO TAG.

With high compression ratios and fast attack times available, this function is suited for a *commercial killer* in a television set application.

#### 4.11 AllPass Function

This function is enabled by setting terminal 27 (ALLPASS) on the TAS3002 device to 1. When asserted, the internal equalization filters are set into AllPass (flat) mode. When this terminal is reset to 0, the equalization filters are returned to the equalization that was in use before the terminal was asserted.

In AllPass mode, the bass and treble controls are still functional.

This function is frequently used for headphones. When the headphone plug is inserted into its jack, a switched contact in the jack enables the AllPass function.

The AllPass function also can be activated by writing a 1 to bit 2 of the analog control register.

# 4.12 Main Control Register 1 (01h)

The TAS3002 device contains two main control registers: main control register 1 (MCR1) and main control register 2 (MCR2). The MCR1 register contains the bits associated with load speed, SCLK frequency, serial-port mode, and serial-port word length. It is accessed via I<sup>2</sup>C with the address 01h.

MCR1 (01h)

| Bit     | b7  | b6  | b5  | b4  | b3 | b2 | b1  | b0  |

|---------|-----|-----|-----|-----|----|----|-----|-----|

| Туре    | R/W | R/W | R/W | R/W | R  | R  | R/W | R/W |

| Default | 1   | Х   | Х   | Х   | Х  | Х  | Х   | Х   |

| BIT | FIELD NAME | TYPE | DESCRIPTION                                                                                               |

|-----|------------|------|-----------------------------------------------------------------------------------------------------------|

| 7   | FL         | R/W  | Fast load<br>0 = Normal operation mode<br>1 = Fast -load mode (default)                                   |

| 6   | SC         | R/W  | SCLK frequency<br>$0 = SCLK \text{ is } 32 \text{ f}_{S}.$<br>$1 = SCLK \text{ is } 64 \text{ f}_{S}.$    |

| 5–4 | E          | R/W  | Serial port mode<br>00 = Left justified<br>01 = Right justified<br>10 = I <sup>2</sup> S<br>11 = Reserved |

| 3–2 | Reserved   | R    | Reserved                                                                                                  |

| 1–0 | W          | R/W  | Serial port word length<br>00 = 16-bit<br>01 = 18-bit<br>10 = 20-bit<br>11 = 24-bit                       |

#### Table 4–2. Main Control Register 1 Description

# 4.13 Main Control Register 2 (43h)

The TAS3002 device contains two main control registers: main control register 1 (MCR1) and main control register 2 (MCR2). The MCR2 register contains the bits associated with the AllPass function and the download of bass and treble control information, and it is accessed via  $I^2C$  with the address 43h.

MCR2 (43h)

| Bit     | 7   | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

|---------|-----|---|---|---|---|---|-----|---|

| Туре    | R/W | R | R | R | R | R | R/W | R |

| Default | 0   | 0 | 0 | х | х | х | 0   | 0 |

| BIT | FIELD NAME | TYPE | DESCRIPTION                                                                                                     |

|-----|------------|------|-----------------------------------------------------------------------------------------------------------------|

| 7   | Reserved   | R/W  | 0 = Normal operation (initial condition after reset)<br>1 = Download bass and treble                            |

| 6–5 | Reserved   | R    | Reserved. Bits 6 and 5 return 0s when read.                                                                     |

| 4–2 | Reserved   | R    | Undefined.                                                                                                      |

| 1   | DM(1-0)    | R/W  | 0 = Normal operation (initial condition after reset)<br>1 = AllPass mode (bass and treble are still functional) |

| 0   | INP        | R    | Reserved. Bit 0 returns 0 when read.                                                                            |

#### Table 4–3. Main Control Register 2 Description

# 5 Filter Processor

# 5.1 Biquad Block

The biquad block consists of seven digital biquad filters per channel organized in a cascade structure, as shown in Figure 5–1. Each of these biquad filters has five downloadable 24-bit (4.20) coefficients. Each stereo channel has independent coefficients.

Figure 5–1. Biquad Cascade Configuration

#### 5.1.1 Filter Coefficients

The filter coefficients for the TAS3002 device are downloaded through the I<sup>2</sup>C port and loaded into the biquad memory space. Each biquad filter memory space has an independent address. Digital audio data coming into the device is processed by the biquad block and then converted into analog waveforms by the DAC. Alternatively, filters can be loaded by asserting terminals on the GPI port.

#### 5.1.2 Biquad Structure

The biquad structure that is used for the parametric equalization filters is as follows:

$$H(z) = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{a_0 + a_1 z^{-1} + a_2 z^{-2}}$$

(1)

**NOTE:** a<sub>0</sub> is fixed at value 1 and is not downloadable.

The coefficients for these filters are represented in 4.20 format—4 bits for the integer part and 20 bits for the fractional part. In order to transmit them over I<sup>2</sup>C, it is necessary to separate each coefficient into three bytes. The upper 4 bits of byte 2 comprise the integer part; the lower 4 bytes of byte 2 plus byte 1 and byte 0 comprise the fractional part.

The filters can be designed using the automatic loudspeaker equalization program (ALE) or a script running under MatLab named Filtermaker. Both of these tools are available from Texas Instruments.

# 6 I<sup>2</sup>C Serial Control Interface

## 6.1 Introduction

Control parameters for the TAS3002 device can be loaded from an I<sup>2</sup>C serial EEPROM by using the TAS3002 master interface mode. If no EEPROM is found, the TAS3002 device becomes a slave device and loads from another I<sup>2</sup>C master interface. Information loaded into the TAS3002 registers is defined in Appendix A.

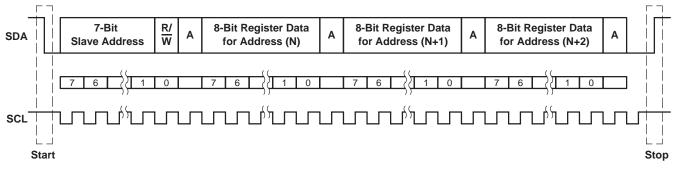

The I<sup>2</sup>C bus uses terminals 16 (SDA for data) and 15 (SCL for clock) to communicate between integrated circuits in a system. These devices can be addressed by sending a unique 7-bit slave address plus  $R/\overline{W}$  bit (1 byte). All compatible devices share the same terminals via a bidirectional bus using a wired-AND connection. An external pullup resistor must be used to set the high level on the bus. The TAS3002 device operates in standard mode up to 100 kbps with as many devices on the bus as desired up to the capacitance load limit of 400 pF.

Furthermore, the TAS3002 device supports a subset of the SMBus protocol. When it is attached to the SMBus, then byte, word, and block transfers are supported. The SMBus NAK function is not supported and care must be taken with the sequence of the instructions sent to the TAS3002 device.

Additionally, the TAS3002 device operates in either master or slave mode; therefore, at least one device connected to the I<sup>2</sup>C bus must operate in master mode.

# 6.2 I<sup>2</sup>C Protocol

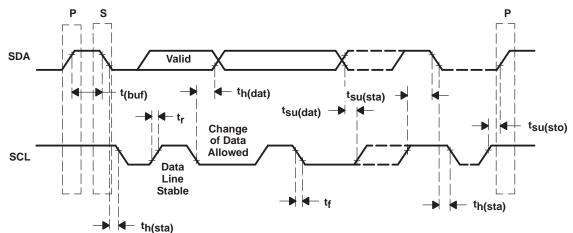

The bus standard uses transitions on SDA while the clock is high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data bit transitions must occur within the low time of the clock period. Figure 6–1 shows these conditions. These start and stop conditions for the I<sup>2</sup>C bus are required by standard protocol to be generated by the master. The master must also generate the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then wait for an acknowledge condition. The slave holds SDA low during acknowledge clock period to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence.

After each 8-bit word, an acknowledgment must be transmitted by the receiving device. There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. Figure 6–1 shows a generic data transfer sequence.

Figure 6–1. Typical I<sup>2</sup>C Data Transfer Sequence

Table 6–1 lists the definitions used by the  $I^{2}C$  protocol.

| DEFINITION      | DESCRIPTION                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends data                                                                           |

| Receiver        | The device that receives data                                                                        |

| Master          | The device that initiates a transfer, generates clock signals, and terminates the transfer           |

| Slave           | The device addressed by the master                                                                   |

| Multimaster     | More than one master can attempt to control the bus at the same time without corrupting the message. |

| Arbitration     | Procedure to ensure the message is not corrupted when two masters attempt to control the bus.        |

| Synchronization | Procedure to synchronize the clock signals of two or more devices                                    |

Table 6–1. I<sup>2</sup>C Protocol Definitions

#### 6.3 Operation

The 7-bit address for the TAS3002 device is 0110 10X R/W where X is a programmable address bit, set by terminal 7 (CS1). Combining CS1 and the R/W bit, the TAS3002 device can respond to four different I<sup>2</sup>C addresses (two read and two write). These two addresses are licensed I<sup>2</sup>C addresses that do not conflict with other licensed I<sup>2</sup>C audio devices. In addition to the 7-bit device address, subaddresses direct communication to the proper memory location within the device. A complete table of subaddresses and control registers is provided in Appendix A. For example, to change bass to 10-dB gain, Section 6.3.1 shows the data that is written to the I<sup>2</sup>C port:

|                               |        | coo byte rubie |     |

|-------------------------------|--------|----------------|-----|

| I <sup>2</sup> C ADDRESS BYTE | A6-A1  | CS1 (A0)       | R/W |

| 68h                           | 011010 | 0              | 0   |

| 69h                           | 011010 | 0              | 1   |

| 6Ah                           | 011010 | 1              | 0   |

| 6Bh                           | 011010 | 1              | 1   |

Table 6–2.

I<sup>2</sup>C Address Byte Table

#### 6.3.1 Write Cycle Example

Start Slave Address R/W A Subaddress A Data A Stop

| FUNCTION                             | DESCRIPTION                                            |

|--------------------------------------|--------------------------------------------------------|

| Start                                | Start condition as defined in I <sup>2</sup> C         |

| Slave address                        | 0110100 (CS1 = 0)                                      |

| R/W                                  | 0 (write)                                              |

| A                                    | Acknowledgement as defined in I <sup>2</sup> C (slave) |

| Subaddress (treble control register) | 0000 0101                                              |

| Data (0 dB gain)                     | 0111 0010                                              |

| Stop                                 | Stop condition as defined in I <sup>2</sup> C          |

NOTE: Table is for serial data (SDA); serial clock (SCL) is not shown but conditions apply as well.

Whenever writing to a subaddress, the correct number of data bytes must follow in order to complete the write cycle. For example, if the volume control register with subaddress 04h is written to, six bytes of data must follow; otherwise, the cycle is incomplete and errors occur.

#### 6.3.2 TAS3002 I<sup>2</sup>C Readback Example

The TAS3002 saves in a stack or first-in first-out (FIFO) buffer the last 7 bytes that were sent to it. When an I<sup>2</sup>C read command is sent to the device (LSB=high), it answers by popping the first byte off the stack. The TAS3002 then expects either a Send Ack command or an I<sup>2</sup>C Stop command from the host. If a Send Ack command is sent from the host then the TAS3002 pops another byte off the stack. If an I<sup>2</sup>C Stop is sent then the TAS3002 ends this transaction. The proper sequence for reading is described as follows:

| I <sup>2</sup> C Start                                                         |  |

|--------------------------------------------------------------------------------|--|

| Send I <sup>2</sup> C address byte with read bit set to 1 (LSB set equal to 1) |  |

| Receive Byte 0                                                                 |  |

| Send Ack                                                                       |  |

| Receive Byte 1                                                                 |  |

| Send Ack                                                                       |  |

| Receive Byte 2                                                                 |  |

| Send Ack                                                                       |  |

| Receive Byte 3                                                                 |  |

| Send Ack                                                                       |  |

| Receive Byte 4                                                                 |  |

| Send Ack                                                                       |  |

| Receive Byte 5                                                                 |  |

| Send Ack                                                                       |  |

| Receive Byte 6 (if an ACK is sent after byte 6 it locks up the TAS3002)        |  |

| I <sup>2</sup> C Stop                                                          |  |

Where:

- I<sup>2</sup>C Start is a valid I<sup>2</sup>C Start command.

- Receive Byte is a valid I<sup>2</sup>C command which reads a byte from the TAS3002.

- Send Ack is a a valid I<sup>2</sup>C command that informs the TAS3002 that a byte has been read.

- I<sup>2</sup>C Stop is a valid I<sup>2</sup>C Stop command.

- NOTES: 1. The TAS3002 will appear to be locked up, if a Send Ack is issued after the last byte read. It is required to send an I<sup>2</sup>C Stop command after the last byte and not a Send Ack.

- 2. The I<sup>2</sup>C Start and I<sup>2</sup>C Stop commands are the same for both I<sup>2</sup>C read and I<sup>2</sup>C write.

#### 6.3.3 I<sup>2</sup>C Wait States

The TAS3002 device performs interpolation algorithms for its volume and tone controls. If a volume or tone change is sent to the part via  $I^2C$ , the command sent after the volume or tone (bass and treble) change causes an  $I^2C$  wait state to occur. This wait state lasts from 41 ms to 231 ms, depending on the system clock rate, the command sent, and, in the case of bass or treble, the amount of the change.

Secondly, if a long series of commands is sent to the TAS3002 device, it may occasionally create a short wait state on the order of 150  $\mu$ s to 300  $\mu$ s while it loads and processes the commands.

When a sample rate of 32 kHz is used, longer wait states can occur, occasionally up to 15 ms.

The preferred way to take care of wait states is to use an I<sup>2</sup>C controller that recognizes wait states. During the wait state period, it stops sending data over I<sup>2</sup>C. If this function is not available on the system controller, fixed delays can be implemented in the system software to ensure that the controller is not trying to send more data while the TAS3002 device is busy. Sending I<sup>2</sup>C data while the TAS3002 device is busy causes errors and locks up the device, which must then be reset.

Table 6–3 gives typical values of the wait states that can be expected with the various functions of the part:

|              | SYSTEM S | SAMPLING FR | EQUENCY |                                 |

|--------------|----------|-------------|---------|---------------------------------|

|              | 32 kHz   | 44.1 kHz    | 48 kHz  | Comment                         |

| Volume       | 62 ms    | 49 ms       | 41 ms   | Not dependent on size of change |

| Bass         | 231 ms   | 167 ms      | 153 ms  | 0 to -18 dB                     |

| Treble       | 231 ms   | 167 ms      | 153 ms  | 0 to -18 dB                     |

| DRC on       | 300 μs   | 300 µs      | 300 µs  |                                 |

| Mixer        | None     | None        | None    |                                 |

| Loudness     | None     | None        | None    |                                 |

| Equalization | 15 ms    | 190 μs      | 300 µs  | Can occur with each filter      |

Table 6–3. I<sup>2</sup>C Wait States

#### 6.4 SMBus Operation

The TAS3002 device supports a subset of the SMBus protocol. With proper programming techniques, it is possible to use the SMBus to set up the TAS3002 device.

#### 6.4.1 Block Write Protocol

The TAS3002 device supports the block write protocol that allows up to 32 bytes to be sent as a block. To send a command using this format, the most significant bit (MSB) of the TAS3002 subaddress must be set high and the subaddress (also with MSB set high) must be programmed into the SMBus command byte. This operation signals the TAS3002 device that the next byte is the SMBus byte-count byte. The next byte after the byte count is then entered into the device as the first byte of data.

|                    | SMBus<br>Command Byte          |                            |      |      |      |

|--------------------|--------------------------------|----------------------------|------|------|------|

| 68h                | 8rh                            | ХХ                         | dd   | dd   | dd   |

| TAS3002<br>Address | Subaddress<br>(r = subaddress) | Byte Count<br>(Don't Care) | Data | Data | Data |

#### 6.4.2 Write Byte Protocol

The TAS3002 device also supports the SMBus write byte protocol. Writing to the main control register (MCR), bass, and treble registers requires using the byte write protocol. To send a command using this protocol, the most significant bit (MSB) of the TAS3002 subaddress must be set high and the subaddress (also with MSB set high) must be programmed into the SMBus command byte. The next byte after the command byte is then entered into the device as the first byte of data.

| SMBus<br>Command Byte |                                |      |  |  |  |  |  |

|-----------------------|--------------------------------|------|--|--|--|--|--|

| 68h                   | 8rh                            | dd   |  |  |  |  |  |

| TAS3002<br>Address    | Subaddress<br>(r = subaddress) | Data |  |  |  |  |  |

#### 6.4.3 Wait States

If separate I<sup>2</sup>C/SMBus commands are sent too frequently, the TAS3002 device can generate a bus wait state. This happens when the device is busy while performing smoothing operations and changing volume, bass, and treble. The wait occurs after the bus acknowledge on the first data byte and can exceed the maximum allowable time allowed according to the SMBus specification (worst case 200 ms).

The following is a possible bus wait state scenario:

| CODE   | Start | 68 | 84 | 06 | 01 | 00                | 00 | 01 | 00 | 00 | Stop |      |

|--------|-------|----|----|----|----|-------------------|----|----|----|----|------|------|

| ACTUAL | Start | 68 | 84 | 06 | 01 | Wait <sup>†</sup> | 00 | 00 | 01 | 00 | 00   | Stop |

<sup>†</sup> If the master does not recognize bus waiting or if the master times out on a long wait, the master must not send consecutive I<sup>2</sup>C/SMBus commands without a time interval of 200 ms between transactions.

#### 6.4.4 TAS3002 SMBus Readback

The TAS3002 device supports a subset of SMBus readback. When an SMBus read command is sent to the device (LSB = high), it answers with the subaddress and the last six bytes written.

|          |       |               | SMBus<br>Command<br>Byte | Byte<br>Count |      |     |     |     |     |      |

|----------|-------|---------------|--------------------------|---------------|------|-----|-----|-----|-----|------|

| SENT     | Start | 69h           | xxh                      | 07h           | Stop |     |     |     |     |      |

| RECEIVED | Start | 07h           | aah                      | ddh           | ddh  | ddh | ddh | ddh | ddh | Stop |

|          |       | Byte<br>Count |                          |               |      |     |     |     |     |      |

Where:

xxh = Command byte. It is a *don't care* because the response contains only the subaddress and the last six bytes of data written to the TAS3002 device.

aah = The last subaddress accessed in the device

ddh = Data bytes from the TAS3002 device

NOTE: Use read sequence defined in 6.3.2

# 7 Microcontroller Operation

The TAS3002 device contains an internal microcontroller programmed by Texas Instruments to perform housekeeping and interface functions. Additionally, it handles I<sup>2</sup>C communication and general purpose input functions.

# 7.1 General Description

The microcontroller uses a 256 f<sub>S</sub> system clock and can access up to 8K bytes of memory. It interfaces with the digital audio interface I<sup>2</sup>C master/slave for downloading data and coefficients. It also interfaces with two internal DSPs for transferring coefficients and other information.

The TAS3002 coefficients are loaded through  $I^2C$  in the master or slave mode. Standard audio processing functions (volume, bass, and treble) can be controlled/activated through external switches connected to the six GPI terminals. Upon reset, the internal microcontroller sets all coefficients and audio parameters to the default values. See Section 7.2.2 for default values.

If the TAS3002 address is 68h (ADDR\_SEL=0), it becomes the bus master device and attempts to load parameters and coefficients from the external EEPROM. If no EEPROM is present, the TAS3002 device remains in its default condition. If addresses other than 68h/69h are set, the TAS3002 device only operates as an I<sup>2</sup>C slave device.

If the microcontroller determines the TAS3002 device has an I<sup>2</sup>C address of 68h/69h and the EEPROM is present, the microcontroller downloads coefficients from the EEPROM. Once the download is complete, it enables the serial audio in the mode defined by an I<sup>2</sup>C write to the MCR to transfer data into and out of the device. Before reading the EEPROM, the serial audio port defaults to I<sup>2</sup>S mode.

The TAS3002 device allows the user to update volume, bass, and treble dynamically by an I<sup>2</sup>C slave command or by a simple GPI input. The GPI can select volume up and down, bass/treble up and down, or digital equalizations. Up to five different equalizations (that is, flat, jazz, rock, voice, etc.) can be stored in the external EEPROM. Also, DRCE, MCR1, MCR2, and loudness contour are enabled and disabled by I<sup>2</sup>C.

When the TAS3002 device operates in the I<sup>2</sup>C master mode, it echoes changes to all of its functions to other I<sup>2</sup>C addresses that are defined in its external EEPROM. If no addresses are defined, it does not echo.

# 7.2 Power-Up/Power-Down Reset

#### 7.2.1 Power-Up Sequence

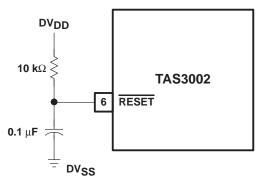

An active low on terminal 6 (RESET) while MCLK is running resets the internal microcontroller and DSPs. RESET synchronizes internally and can be asserted asynchronously or with the simple RC circuit in Figure 7–1. On reset, SCL and SDA go to a high-impedance state. If the I<sup>2</sup>C address is set to 68h, approximately 400  $\mu$ s after RESET returns to a 1, the device sends a one-byte query via I<sup>2</sup>C to look for an EEPROM. If an EEPROM is found, the TAS3002 becomes an I<sup>2</sup>C master; otherwise, it becomes an I<sup>2</sup>C slave. When using address 68h in the slave mode, an external master must wait until after the EEPROM query or else bus contention and improper operation occur.

I<sup>2</sup>C address x6Ah does not query the bus for an EEPROM. The address for the EEPROM is A0h.

#### 7.2.2 Reset

The TAS3002 device has an asynchronous reset terminal (RESET). This reset is synchronized with various clocks used in this device to generate a synchronous internal reset. Upon reset, the TAS3002 device goes through the following process:

• Clears all the RAM memory content

- Clears all the registers in the circuits

- Purges the codec

- Selects analog input A (RINA and LINA) and sets the input A active indicator (INPA) low

- Initializes the equalization parameters to AllPass filters

- Sets the digital audio interface to the I<sup>2</sup>S 18-bit mode

- Sets the bass/treble to 0 dB

- Sets the mixer gain to 0 dB SDIN1 and mutes both SDIN2 and analog-in

- Sets the volume to -40 dB

- Turns off all enhancement features (DRCE, etc.)

- Reads the I<sup>2</sup>C address. If the address is 68h, the device reads its EEPROM. It is possible to load the user-defined bass/treble data and break points (optional). If there is no data, the device loads default bass/treble delta and break points from ROM.

- If the address is 6Ah, the device puts the I<sup>2</sup>C interface in slave mode and waits for input.

#### 7.2.3 Reset Circuit

Because the TAS3002 device has an internal power-on reset (POR), in many cases, additional components are not needed to reset the device. It resets internally at approximately 80% of V<sub>DD</sub>.

In the case where the system power supplies are slow in reaching their final voltage or where there is a difference in the time the system power supplies take to become stable, the TAS3002 reset can be delayed by a simple RC circuit.

Figure 7–1. TAS3002 Reset Circuit

The reset delay for the above circuit can be calculated by the simple equation:

t<sub>rd</sub> = 0.8RC + 400 μs

Where:  $t_{rd}$  = The delay before the TAS3002 device comes out of reset

C = Value of the capacitance from  $\overline{\text{RESET}}$  (pin 6) to  $\text{DV}_{SS}$

R = Value of the resistance from  $\overline{\text{RESET}}$  (pin 6) to  $DV_{DD}$

The circuit described in Figure 7–1 delays the start-up of the TAS3002 device approximately 1.2 ms.

When it is necessary to control the reset of the TAS3002 device with an external device, such as a microcontroller,  $\overline{\text{RESET}}$  (pin 6) can be treated as a logic signal. It then brings the device out of reset when the voltage on  $\overline{\text{RESET}}$  reaches V<sub>DD</sub>/2.

#### 7.2.4 Fast Load Mode

While in fast load mode—FL bit (bit 7 of main control register 1) = 0—it is possible to update the parametric equalization without any audio processing delay. The audio processor pauses while the RAM is updated in this mode.

Bass and treble cannot download in this mode. Mixer1 and Mixer2 registers can download in this mode or normal mode (FL bit = 0).

Once the download is complete, the fast load bit must be cleared by writing a 0 into bit 7 of main control register 1 (MCR1). This puts the TAS3002 device into normal mode.

#### 7.2.5 Codec Reset

During initialization, the output of the codec is disabled. Throughout reset and initialization, the output of the DAC is muted to prevent extraneous noise being sent to the system output.

Data from the ADC and other internal processing is purged so that when reset/initialization is complete, only valid inputs are sent to the system output.

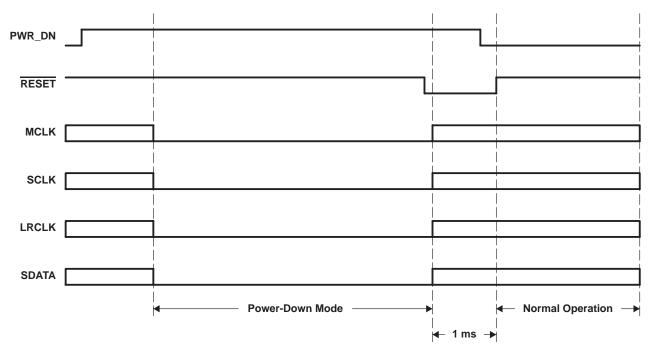

#### 7.3 Power-Down Mode

The TAS3002 device has an asynchronous power-down mode. In the power-down mode, the internal control registers and equalization programming of the device are stored in the device.

To enter power-down mode:

- 1. Assert the power-down control signal (1)

- 2. Set the serial audio input clocks to 0

The TAS3002 device goes into power-down mode.

To exit the power-down mode:

- 1. Assert RESET (logic 0)

- 2. Restart the serial audio clocks

- 3. Wait for a delay of 1.0 ms (to allow the PLL to lock)

- 4. Negate the power-down control signal (logic 0)

- 5. Negate RESET (logic 1)

The device then returns to the state it was in before power down (resumes normal operation).

7.3.1 Power-Down Timing Sequence

Figure 7–2. Power-Down Timing Sequence

In power-down mode, the TAS3002 device typically consumes less than 1 mA.

#### 7.4 Test Mode

Terminal 9 (TEST) is tied low in normal operation. This function is reserved for factory test and must not be asserted.

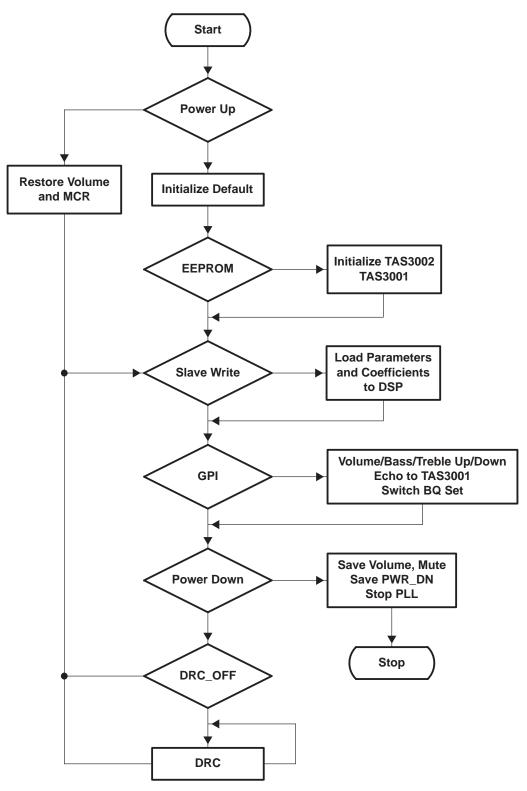

### 7.5 Internal Interface

Figure 7–3 shows the flow chart of the interface between the microcontroller and its peripheral blocks.

### 7.6 GPI Terminal Programming

During initialization, the microcontroller fetches a control byte from its EEPROM or receives a command from I<sup>2</sup>C.

#### 7.6.1 GPI Interface

The six GPI terminals are programmed to operate as indicated in Table 7–1.

|                | GPI5 | GPI4 | GPI3 | GPI2 | GPI1 | GPI0 |

|----------------|------|------|------|------|------|------|

|                |      | GF14 | GFIS | GFIZ | GFII | GFIU |

| VOL_UP, +1 dB  | X    |      |      |      |      |      |

| VOL_DN, -1 dB  |      | х    |      |      |      |      |

| BASS_UP, +1 dB |      |      | х    |      |      |      |

| BASS_DN, -1 dB |      |      |      | х    |      |      |

| TREB_UP, +1 dB |      |      |      |      | x    |      |

| TREB_DN, -1 dB |      |      |      |      |      | х    |

| Shift 1        | х    |      |      |      |      | х    |

| Mute           | х    |      |      |      |      |      |

| EQ1            |      | х    |      |      |      |      |

| EQ2            |      |      | х    |      |      |      |

| EQ3            |      |      |      | х    |      |      |

| EQ4            |      |      |      |      | х    |      |

| EQ5            |      |      |      |      |      | х    |

| Shift 2        |      |      | х    | х    |      | 1    |

Table 7–1. GPI Terminal Programming

NOTE: x = Logic low

Initially (after reset), the TAS3002 GPI is set to control volume, bass, and treble. Simultaneously setting GPI bits 1 and 5 low for 1 second changes the function of the GPI terminals to control mute and equalization.

To return to volume, bass, and treble control, simultaneously set GPI terminals 2 and 3 low for 1 second.

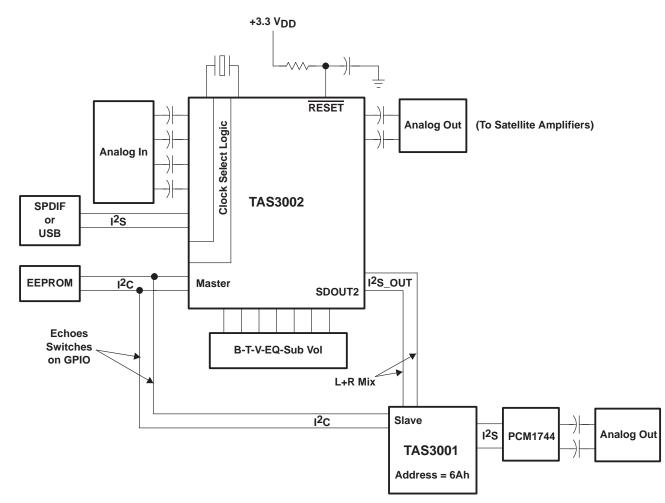

When a GPI terminal is activated, the TAS3002 device echoes its function over I<sup>2</sup>C to a TAS3001 device mapped to address 6Ah. Therefore, a system with two audio equalization chips can be implemented without the need for a microcontroller.

#### 7.6.2 GPI Architecture

The GPI provides simple but flexible input port to activate the input parameters. Each terminal input is an active logic low.

Figure 7–3. Internal Interface Flow Chart

### 7.7 External EEPROM Memory Maps

Table 7–2 through Table 7–5 show the 512-byte and 2048-byte EEPROM memory maps.

| Таріс     |             |                             |                                                   |  |

|-----------|-------------|-----------------------------|---------------------------------------------------|--|

| ADDRESS   | BYTE NUMBER | FUNC                        | CTION                                             |  |

| 000h      | 1           | Signature (2Ah)             |                                                   |  |

| 001h      | 1           | ID byte = 0000 0000         |                                                   |  |

| 002h      | 1           | MCR                         |                                                   |  |

| 003h-00Bh | 9           | Mixer left gain             |                                                   |  |

| 00Ch-014h | 9           | Mixer right gain            |                                                   |  |

| 015h–01Ah | 2           | DRC (ratio, threshold, ener | rgy $\alpha$ , attack $\alpha$ , decay $\alpha$ ) |  |

| 01Bh      | 1           | Bass                        |                                                   |  |

| 01Ch      | 1           | Treble                      |                                                   |  |

| 01Dh-022h | 6           | Volume                      |                                                   |  |

| 031h-03Fh | 15          | Biquad 0                    |                                                   |  |

| 040h-04Eh | 15          | Biquad 1                    |                                                   |  |

| 04Fh-05Dh | 15          | Biquad 2                    |                                                   |  |

| 05Eh-06Ch | 15          | Biquad 3                    | Left channel                                      |  |

| 06Dh-07Bh | 15          | Biquad 4                    |                                                   |  |

| 07Ch-08Ah | 15          | Biquad 5                    |                                                   |  |

| 08Bh-099h | 15          | Biquad 6                    |                                                   |  |

| 09Ah      | 1           | 0 dB/bass                   |                                                   |  |

| 09Bh      | 1           | 0 dB/treble                 |                                                   |  |

| 09Ch-0A1h | 6           | Bass break                  |                                                   |  |

| 0A2h-0A7h | 6           | Treble break                |                                                   |  |

| 0A8h-110h | 105         | Bass delta                  |                                                   |  |

| 111h–179h | 105         | Treble delta                |                                                   |  |

| 17Ah–17Fh | 6           | Bass set point              |                                                   |  |

| 180h–185h | 6           | Treble set point            |                                                   |  |

| 186h–194h | 15          | Biquad 0                    |                                                   |  |

| 195h-1A3h | 15          | Biquad 1                    | ]                                                 |  |

| 1A4h-1B2h | 15          | Biquad 2                    |                                                   |  |

| 1B3h-1C1h | 15          | Biquad 3                    | Right channel                                     |  |

| 1C2h-1D0h | 15          | Biquad 4                    |                                                   |  |

| 1D1h-1DFh | 15          | Biquad 5                    |                                                   |  |

| 1E0h-1EEh | 15          | Biquad 6                    |                                                   |  |

|           |             |                             |                                                   |  |

Table 7–2. 512-Byte EEPROM Memory Map 2.0 Channels

NOTE: Bytes are in the same order as they appear in the I<sup>2</sup>C register map. The EEPROM address is A0h.

| ADDRESS   | BYTE NUMBER | FUNCTION                                                                    |                |

|-----------|-------------|-----------------------------------------------------------------------------|----------------|

| 000h      | 1           | Signature (2Ah)                                                             |                |

| 001h      | 1           | ID byte = 0000 0011                                                         |                |

|           |             | TAS3002                                                                     |                |

| 002h      | 1           | MCR                                                                         |                |

| 003h-00Bh | 9           | Mixer left gain                                                             |                |

| 00Ch-014h | 9           | Mixer right gain                                                            |                |

| 015h–01Ah | 6           | DRC (ratio, threshold, energy $\alpha$ , attack $\alpha$ , decay $\alpha$ ) |                |

| 01Bh      | 1           | Bass                                                                        |                |

| 01Ch      | 1           | Treble                                                                      |                |

| 01Dh-022h | 6           | Volume                                                                      |                |

| 031h–03Fh | 15          | Biquad 0                                                                    |                |

| 040h-04Eh | 15          | Biquad 1                                                                    |                |

| 04Fh–05Dh | 15          | Biquad 2                                                                    | TAS3002        |

| 05Eh-06Ch | 15          | Biquad 3                                                                    | right and left |

| 06Dh-07Bh | 15          | Biquad 4                                                                    | channel        |

| 07Ch-08Ah | 15          | Biquad 5                                                                    |                |

| 08Bh-099h | 15          | Biquad 6                                                                    |                |

| 09Ah      | 1           | 0 dB/bass                                                                   |                |

| 09Bh      | 1           | 0 dB/treble                                                                 |                |

| 09Ch-0A1h | 6           | Bass break                                                                  |                |

| 0A2h-0A7h | 6           | Treble break                                                                |                |

| 0A8h–110h | 105         | Bass delta                                                                  |                |

| 111h–179h | 105         | Treble delta                                                                |                |

| 17Ah–17Fh | 6           | Bass set point                                                              |                |

| 180h–185h | 6           | Treble set point                                                            |                |

| 186h–194h | 15          | Biquad 0                                                                    |                |

| 195h–1A3h | 15          | Biquad 1                                                                    |                |

| 1A4h–1B2h | 15          | Biquad 2                                                                    | TAS3001        |

| 1B3h–1C1h | 15          | Biquad 3                                                                    | right and left |

| 1C2h-1D0h | 15          | Biquad 4                                                                    | channel        |

| 1D1h–1DFh | 15          | Biquad 5                                                                    |                |

| 1E0h–1EEh | 15          | Biquad 6                                                                    |                |

|           |             | TAS3001                                                                     | •              |

| 1EFh      | 1           | MCR                                                                         |                |

| 1F0h-1F2h | 3           | SDIN1 gain                                                                  |                |

| 1F3h-1F5h | 3           | SDIN2 gain                                                                  |                |

| 1F6h–1F7h | 2           | DRC (ratio, threshold, energy $\alpha$ , attack $\alpha$ , decay $\alpha$ ) |                |

| 1F8h      | 1           | Bass                                                                        |                |

| 1F9h      | 1           | Treble                                                                      |                |

| 1FAh–1FFh | 6           | Volume                                                                      |                |

#### Table 7–3. 512-Byte EEPROM Memory Map 2.1 Channels (with TAS3001)

NOTE: In this mode, the TAS3002 and the TAS3001 devices both use the same equalization coefficients for their right and left channels. Bytes are in the same order as they appear in the I<sup>2</sup>C register map. The EEPROM address is A0h.

| TAS3002 ADDRESS<br>LEFT BIQUAD | NUMBER<br>OF BYTES | FUNCTION      | CATEGORY                  | TAS3002 ADDRESS<br>RIGHT BIQUAD | TAS3001   |

|--------------------------------|--------------------|---------------|---------------------------|---------------------------------|-----------|

| 000h                           | 1                  |               | Signature                 | e (2Ah)                         |           |

| 001h                           | 1                  | 1 0           | 0 0                       | 0 0                             | 1 0       |

| 002h                           | 1                  | •             | MCR                       |                                 | 1EFh      |

| 003h-00Bh                      | 9/3                |               | Mixer left gain           |                                 | 1F0h-1F2h |

| 00Ch-014h                      | 9/3                |               | Mixer right gain          |                                 | 1F3h-1F5h |

| 015h-019h                      | 6/2                | DRC (ratio, t | hreshold, energyα, attacl | kα, decayα)                     | 1F6h-1F7h |

| 01Ah                           | 1                  |               | Bass                      |                                 | 1F8h      |

| 01Bh                           | 1                  |               | Treble                    |                                 | 1F9h      |

| 01Ch-021h                      | 6                  |               | Volume                    |                                 | 1FAh–1FFh |

| 031h-03Fh                      | 15                 | Biguad 0      | Volume                    | 3A4h–3B2h                       | 186h–194h |

| 040h-04Eh                      | 15                 | Biquad 0      |                           | 3B3h-3C1h                       | 195h–1A3h |

| 04Fh-05Dh                      | 15                 | Biquad 2      |                           | 3C2h-3D0h                       | 1A4h-1B2h |

| 05Eh-06Ch                      | 15                 | Biquad 2      | Set 0                     | 3D1h-3DFh                       | 1B3h–1C1h |

| 06Dh-07Bh                      | 15                 | Biquad 3      | 000                       | 3E0h–3EEh                       | 1C2h-1D0h |

| 07Ch-08Ah                      | 15                 | Biquad 5      |                           | 3EFh-3FDh                       | 1D1h-1DFh |

| 08Bh-099h                      | 15                 | Biquad 6      |                           | 3FEh–40Ch                       | 1E0h–1EEh |

| 09Ah-185h                      | 236                | Biquado       | Bass treb                 |                                 |           |

| 200h-20Eh                      | 15                 | Biquad 0      |                           | 40Dh-41Bh                       | 5B1h–5BFh |

| 20Fh-21Dh                      | 15                 | Biquad 0      |                           | 41Ch-42Ah                       | 5C0h-5CEh |

| 21Eh-22Ch                      | 15                 | Biquad 2      |                           | 42Bh-439h                       | 5CFh-5DDh |

| 22Dh-23Bh                      | 15                 | Biquad 2      | Set 1                     | 43Ah-448h                       | 5DEh-5ECh |

| 23Ch-24Ah                      | 15                 | Biquad 4      |                           | 449h-457h                       | 5EDh-5FBh |

| 24Bh-259h                      | 15                 | Biquad 5      |                           | 458h-466h                       | 5FCh-60Ah |

| 25Ah-268h                      | 15                 | Biquad 6      |                           | 467h-475h                       | 60Bh-619h |

| 269h-277h                      | 15                 | Biquad 0      |                           | 476h–484h                       | 61Ah-628h |

| 278h-286h                      | 15                 | Biquad 0      |                           | 485h-493h                       | 629h-637h |