**TENTATIVE**

TOSHIBA BIPOLAR LINEAR INTEGRATED CIRCUIT SILICON MONOLITHIC

# TA8899AF

#### FM DEMODULATION IC FOR BROADCASTING SATELLITE RECEIVER

TA8899AF combines the necessary function on a single monolithic integrated circuit to modulate FM signal of the 2nd IF of DBS.

#### **FEATURES**

- 5V single power source

- 2nd IF AGC amplifier (AGC range 50dB or more)

- Logarithmic-linear type signal level amplifier

- PLL type FM detector (variable impedance built in)

- Adjustment free AFT circuit (IF frequency direct count type digital AFT) and also designed for keyed AFT system

- Output terminal of 1'st AGC control circuit

Weight: 0.63g (Typ.)

961001EBA

The products described in this document are subject to foreign exchange and foreign trade control laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

<sup>●</sup> TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

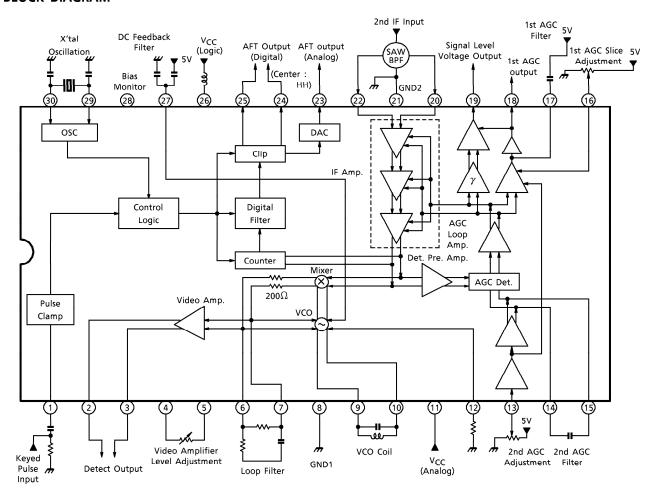

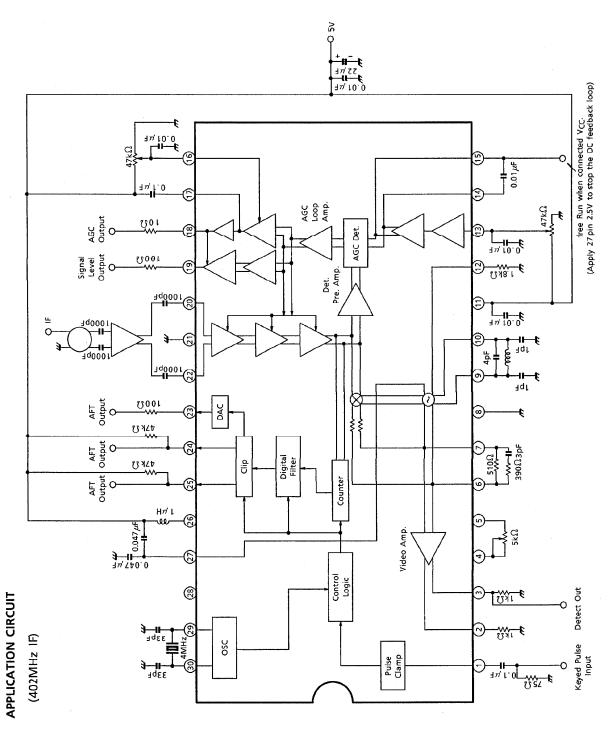

#### **BLOCK DIAGRAM**

#### **TERMINAL FUNCTION**

|            | ERMINAL FUNCTION                    |                                                                                                                                                                                                                                                                                                              |                                                             |  |  |  |  |  |

|------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| PIN<br>No. | PIN NAME                            | FUNCTION                                                                                                                                                                                                                                                                                                     | INTERFACE CIRCUIT                                           |  |  |  |  |  |

| 1          | Keyed Pulse Input                   | It clamps at the pulse peak and generates the reference level. The input impedance is $3k\Omega$ .                                                                                                                                                                                                           | 300k<br>1 1kΩ<br>1 1kΩ<br>2 .5v                             |  |  |  |  |  |

| 2 3        | Detect Output                       | It outputs the detection output through a low-pass filter of 30MHz cut off frequency using an emitter follower.                                                                                                                                                                                              | 2 3 4 1000Ω<br>Δ 3 mA A 5 kΩ<br>Δ 3 mA A 5 kΩ               |  |  |  |  |  |

| 4 5        | Video Amplifier<br>Level Adjustment | It controls the level adjustment by varying the emitter resistor of a differential amplifier. If the resistor between pins 4 and 5 is reduced the output will be greater, however, since the output dynamic range is narrow the output level should be used in the range of lower than 0.7V <sub>p-p</sub> . | 1.3kΩ 0.1pF 1.3kΩ  5,6kΩ  5,6kΩ  5,6kΩ  5,0kΩ               |  |  |  |  |  |

| 6<br>7     | Loop Filter                         | The output impedance is 200 $\Omega$ .                                                                                                                                                                                                                                                                       | 4.3V<br>VCO<br>VCO<br>VCO<br>VCO<br>VCO<br>VCO<br>VCO<br>VC |  |  |  |  |  |

| PIN<br>No. | PIN NAME                           | FUNCTION                                                                                                                                                                                                                | INTERFACE CIRCUIT                          |

|------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 8          | GND1                               | It is the GND of VCO circuit blocks that are VCO (pins 9, 10, 12), loop filter (pins 6, 7), video amplifier (pins 4, 5) AFT system (pins 1, 23, 24, 25, 26, 27, 28) and S/H (pins 29, 30).                              | _                                          |

| 9 10       | VCO Coil                           | It is the VCO using variations in internal impedance of diode for control voltage from mixer.  Use a UJ characteristic for the capacitor of the external tank circuit to correct the internal temperature drift.        | 32 00 1 10 10 10 10 10 10 10 10 10 10 10 1 |

| 12         | VCO Temperature<br>Compensate Bias | The VCO bias is composed of a synthesis of bias in proportion to VBE and VT of transistor, and this terminal generates a bias proportioned to the VBE. If the external resistor reduced, the VCO sensitivity will rise. | VCC 2kΩ VCO Bias                           |

| 13         | 2nd AGC<br>Adjustment              | It changes the input level for a AGC detector. It adjusts by adding the direct current offset to pins 14 and 15. The variation width of about 8dB can be added. Internal bias is 2.5V.                                  | Vcc 2                                      |

| PIN<br>No. | PIN NAME                    | FUNCTION                                                                                                                                                                                                                                                                       | INTERFACE CIRCUIT                          |

|------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 14<br>15   | 2nd AGC Filter              | It generates the AGC voltage by filtering the 403MHz IF signal by means of an internal resistor and an external capacitor. If applying the V <sub>CC</sub> to pin 15, the AGC will be minimum gain and the VCO oscillates at free-running frequency.                           | VCC                                        |

| 16         | 1st AGC Slice<br>Adjustment | It sets the input level threshold for generating the control signal to lower gain from the IC to the 2nd converter of front stage when excessive signal input. Even if the 2nd AGC adjustment varies, the 1st AGC adjustment point hardly changes.  The internal bias is 2.5V. | V <sub>CC</sub>                            |

| 17         | 1st AGC Filter              | It outputs by comparating with the AGC and 1st AGC slice level adjustment voltages. This comparator is constructed by the active load type high gain amplifier and determines its response by a capacitor connected to this terminal.                                          | 12 S S S S S S S S S S S S S S S S S S S   |

| 18         | 1st AGC Control             | It outputs the control voltage using an emitter follower (active low level). The internal current sink has only $25\mu\text{A}$ .                                                                                                                                              | (B) (A) (A) (A) (A) (A) (A) (A) (A) (A) (A |

| PIN<br>No. | PIN NAME                       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                       | INTERFACE CIRCUIT                         |

|------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 19         | Signal Level<br>Voltage Output | It outputs the AGC voltage by doing logarithm <-> linear conversion. In the TA8899AF the level detection can be carried out even after the 1st AGC is effective and input is reduced using the 1st AGC output.                                                                                                                                                                                 | 19 VCC                                    |

| 20 22      | 2nd IF Input                   | The IF amplifier constructed by the 3-step series connection of variable gm type gain control, of which the maximum gain is $47dB$ and minimum gain $-8dB$ . In order to prevent a sneak of radio frequency, all the circuits are balance-connected. Therefore, the differential combination is also desirable for the IC input. The internal bias is 2.0V and input impedance is $1k\Omega$ . | 2) VCC VCC VCC VCC VCC VCC VCC VCC VCC VC |

| 23         | AFT Output<br>(Analog)         | This counts the IF frequency, averages the count data, carries out D/A conversion of the signal and outputs an AFT signal. X'tal is used for the reference signal of this AFT operation, so operation is stabilized against temperature fluctuation. Furthermore, an AFT signal is created from an IF signal, and so VCO oscillation is an independent operation.                              | VCC VCC VCC                               |

| PIN<br>No. | PIN NAME                | FUNCTION                                                                                                                                                                                                                                                                                                                           | INTERFACE CIRCUIT                |

|------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

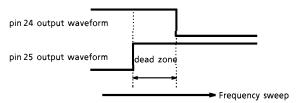

| 24<br>25   | AFT Output<br>(Digital) | These are high detection ("H" when the IF signal is high) and low detection ("H" when the IF signal is low). These shows both outputs is high when the input frequency is nearby 402.78MHz.                                                                                                                                        | Vcc Vcc                          |

| 26         | VCC<br>(Logic Block)    | To avoid interference of digital circuits and analog circuits connect to the power line through a 1 $\mu$ H inductor.                                                                                                                                                                                                              | _                                |

| 27         | DC Feedback Filter      | In order to correct the lag between the VCO's fo and the input's IF signal, the wave detection output's DC offset is used and a circuit installed which feeds this back to the VCO oscillation frequency. The low pass filter for detecting this DC offset is composed of an internal resistor and an external capacitor. (fc=1Hz) | ν <sub>CC</sub> 2.2ΜΩ  1kΩ  1 kΩ |

| 28         | Bias Monitor            | This terminal monitors the bias of an internal logic circuit. Normally keep it open.                                                                                                                                                                                                                                               | 28 K K K                         |

| 29<br>30   | X'tal Oscillation       | This is the 4MHz X'tal oscillation terminal, the reference for internal digital operations. When supplying 4MHz OSC from other, please input to a 29 pin.                                                                                                                                                                          | 29 500Ω<br>500Ω<br>500Ω<br>30    |

## **MAXIMUM RATINGS** (Ta = $25^{\circ}$ C)

| CHARACTERISTIC        | SYMBOL           | RATING          | UNIT |

|-----------------------|------------------|-----------------|------|

| Power Supply Voltage  | VCC MAX          | 6.0             | V    |

| Power Dissipation     | PD MAX           | 1000            | mW   |

| Operation Temperature | T <sub>opr</sub> | <b>- 20∼75</b>  | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>-</b> 55∼150 | °C   |

| Lead Temperature      | _                | 260°C, 10       | )s   |

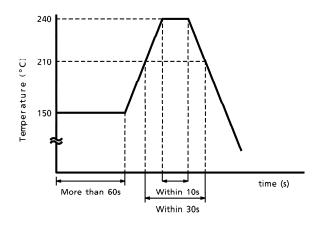

Recommended assembly method : Recommended temperature profile of reflow soldering of far and medium infrared rays

#### RECOMMENDED POWER SUPPLY VOLTAGE

| PIN<br>No. | PIN NAME                 | MIN. | TYP. | MAX. | UNIT |

|------------|--------------------------|------|------|------|------|

| 11         | V <sub>CC</sub> (Analog) | 4.75 | 5.0  | 5.25 | V    |

| 26         | V <sub>CC</sub> (Logic)  | 4.75 | 5.0  | 5.25 | V    |

**ELECTRICAL CHARACTERISTICS**

DC CHARACTERISTICS (Unless otherwise specified,  $V_{CC} = 5.0V$ , Ta = 25°C)

| CHARACTERISTIC                     |        | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION           | MIN.  | TYP. | MAX.  | UNIT |

|------------------------------------|--------|------------------|----------------------|--------------------------|-------|------|-------|------|

| Supply Cur                         | rent   | lcc              | 1                    | _                        | 75    | 100  | 125   | mA   |

|                                    | Pin 1  | V <sub>1</sub>   |                      | _                        | 2.0   | 2.5  | 3.0   |      |

| <b>[</b>                           | Pin 2  | V <sub>2</sub>   |                      | _                        | 1.5   | 2.0  | 2.5   |      |

|                                    | Pin 3  | V <sub>3</sub>   |                      | 1                        | 1.5   | 2.0  | 2.5   |      |

|                                    | Pin 4  | V <sub>4</sub>   |                      |                          | 0.8   | 1.3  | 1.8   |      |

|                                    | Pin 5  | V <sub>5</sub>   |                      | _                        | 0.8   | 1.3  | 1.8   |      |

|                                    | Pin 6  | ٧6               |                      | _                        | 2.2   | 2.7  | 3.2   |      |

|                                    | Pin 7  | V <sub>7</sub>   |                      | _                        | 2.2   | 2.7  | 3.2   |      |

|                                    | Pin 9  | V <sub>9</sub>   |                      | _                        | 2.2   | 2.7  | 3.2   |      |

|                                    | Pin 10 | V <sub>10</sub>  |                      | _                        | 2.2   | 2.7  | 3.2   |      |

| Terminal                           | Pin 12 | V <sub>12</sub>  | 1                    | 1.8k $\Omega$ -GND       | 0.08  | 0.2  | 0.32  |      |

| Voltage                            | Pin 13 | V <sub>13</sub>  |                      | _                        | 2.3   | 2.5  | 2.7 V | V    |

| Voltage                            | Pin 14 | V <sub>14</sub>  |                      | _                        | _     | 3.7  | _     |      |

|                                    | Pin 15 | V <sub>15</sub>  |                      | _                        | _     | 3.9  | _     |      |

|                                    | Pin 16 | V <sub>16</sub>  |                      | _                        | 2.1   | 2.5  | 2.9   |      |

|                                    | Pin 18 | V <sub>18h</sub> |                      | Pin 17 : $1k\Omega$ -GND | _     | 1.0  | 1.3   |      |

|                                    |        | V <sub>18I</sub> |                      | Pin 17: V <sub>CC</sub>  | 3.9   | 4.3  | 4.7   |      |

|                                    | Pin 20 | V <sub>20</sub>  |                      | _                        | 1.5   | 2.0  | 2.5   |      |

| Ī                                  | Pin 22 | V <sub>22</sub>  | _                    | _                        | 1.5   | 2.0  | 2.5   |      |

|                                    | Pin 28 | V <sub>28</sub>  |                      | _                        | 1.8   | 2.2  | 2.6   |      |

| [                                  | Pin 29 | V <sub>29</sub>  |                      | _                        | 2.3   | 2.7  | 3.0   |      |

|                                    | Pin 30 | V <sub>30</sub>  |                      | _                        | 2.3   | 2.7  | 3.0   |      |

| Pin 2, 3 Acceptable Output Current |        |                  | 1                    |                          | - 1.0 |      | 6.0   | mA   |

| 1st AGC Output<br>Current          |        | l <sub>18</sub>  | 1                    | _                        | -0.02 |      | 6.0   | mA   |

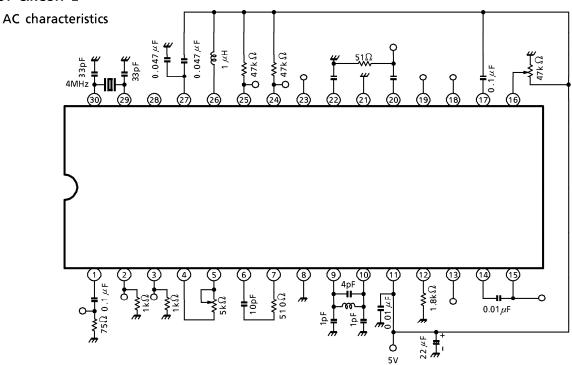

### **AC CHARACTERISTICS**

| AC CHARACTERISTICS                                              |                    |                      |                                                                                            |      |       |       |                  |

|-----------------------------------------------------------------|--------------------|----------------------|--------------------------------------------------------------------------------------------|------|-------|-------|------------------|

| CHARACTERISTIC                                                  | SYMBOL             | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                             | MIN. | TYP.  | MAX.  | UNIT             |

| IF Input Frequency<br>Range                                     | fin                | 2                    | _                                                                                          | 350  | 400   | 550   | MHz              |

| IF Input Level Range                                            | v <sub>in</sub>    | 2                    | _                                                                                          | - 50 | _     | - 10  | dBmW             |

| 1st AGC Shoulder Level<br>Range                                 | AGC <sub>MAX</sub> | 2                    | Pin 16 = 2.5V                                                                              | - 33 | - 26  | - 19  | dBmW             |

| 1st AGC Control<br>Sensitivity                                  | ∆AGC               | 2                    | _                                                                                          | 1.3  | 2.7   |       | V/dB             |

| Signal Level Sensitivity                                        | ΔV/Δν              | 2                    | _                                                                                          | 50   | 100   | 150   | mV/dB            |

| VCO Conversion<br>Sensitivity                                   | β                  | 2                    | _                                                                                          | 60   | 80    | 110   | MHz/V            |

| VCO Temperature Drift                                           | ⊿f <sub>Ta</sub>   | 2                    | Ta = − 10~65°C                                                                             | _    | ± 1.0 | ± 2.5 | MHz              |

| PLL Lock Range                                                  | fL                 | 2                    | _                                                                                          | ± 20 | ± 30  | _     | MHz              |

| PLL Capture Range                                               | fc                 | 2                    | _                                                                                          | ± 20 | ± 30  | _     | MHz              |

| Demodulation Output<br>Level                                    | V <sub>out</sub>   | 2                    | $\Delta f$ = 10MHz <sub>p-p</sub><br>Converting to output rate<br>Pin 4, 5 : 2.4k $\Omega$ | 0.35 | 0.50  | 0.65  | V <sub>p-p</sub> |

| Video Amplifier Variable<br>Width                               | Vo S/5             | 2                    | Pin 4, $5:$ short, $5k\Omega$                                                              | 10   | _     | _     | dB               |

| Demodulation Output<br>Amplitude Frequency<br>Characteristics 1 | Vo A1              | 2                    | f=0.2~4MHz<br>Reference: 100kHz                                                            | _    | _     | ± 2   | dB               |

| Demodulation Output<br>Amplitude Frequency<br>Characteristics 2 | Vo A2              | 2                    | f=4~9MHz<br>Reference: 100kHz                                                              | _    | _     | ± 2   | dB               |

| Group Delay<br>Characteristics 1                                | τ pd1              | 2                    | f = 0.2~4MHz<br>Reference: 100kHz                                                          | _    | _     | ± 10  | ns               |

| Group Delay<br>Characteristics 2                                | τ pd2              | 2                    | f = 4~9MHz<br>Reference: 100kHz                                                            | _    | _     | ± 40  | ns               |

| Keyed AFT Input Range                                           | ٧1                 | 2                    | _                                                                                          | 0.35 | 0.5   | 0.65  | $V_{p-p}$        |

| Keyed AFT Input<br>Frequency                                    | Т1                 | 2                    | _                                                                                          | 8.0  | 16.7  | 50    | ms               |

| AFT Sensitivity                                                 | <b>Δf/ΔV</b>       | 2                    | _                                                                                          | 1.5  | 2.0   | 2.8   | MHz / V          |

| AFT Width of Dead Zone                                          | V <sub>DEAD</sub>  | 2                    | _                                                                                          | 281  | 313   | 344   | kHz              |

| Digital AFT Voltage Low<br>Level                                | V <sub>20L</sub>   | 2                    | _                                                                                          | _    | 0.2   | 0.5   | ٧                |

| DG                                                              | DG                 | 2                    | APL: 10~90%                                                                                |      | ± 2.0 | ± 3.0 | %                |

| DP                                                              | DP                 | 2                    | APL: 10~90%                                                                                |      | ± 2.0 | ± 3.0 | 0                |

| I M 2                                                           | IM2                | 2                    | 2.15MHz beat level (*)                                                                     | 45   | 50    | _     | dB               |

| I M 3                                                           | IM3                | 2                    | 1.43MHz beat level (*)                                                                     | 45   | 50    | _     | dB               |

| Video S/N                                                       | SN <sub>sat</sub>  | 2                    | _                                                                                          | 51   | _     |       | dB               |

| External Input Level<br>(4MHz Clock)                            | X <sub>in</sub>    | 2                    | _                                                                                          | 0.3  | 0.5   | 0.7   | V <sub>p-p</sub> |

| VCO Initial Drift                                               | SWON               | 2                    | 3~20s                                                                                      | 0    | _     | 850   | kHz              |

|                                                                 |                    |                      |                                                                                            |      |       |       |                  |

<sup>(\*)</sup> VCO coil must be adjusted to make IM2/3 best value

#### **MEASUREMENT CONDITION**

(Note 1) 1st AGC Shoulder Level Range : AGCMAX

F=402.78MHz input level  $v_{in}$  = 0 to -40dBmW (50 $\Omega$ ) to pin 20. Measure  $v_{in}$  that pin 18 voltage is lower than 4V by opening pin 16 and raising  $v_{in}$ .

(Note 2) 1st AGC Control Sensitivity: △AGC

Input f = 402.78MHz  $v_{in}$  = 0~ – 40dBmW (50 $\Omega$ ) to pin 20. Calculate  $v_{in}$  that pin 18 voltage is 4V/1V (as  $v_{in1}$ ,  $v_{in2}$ ), using the equation below.

$$\triangle AGC = -3/(v_{in1} - v_{in2}) \quad V/dB$$

(Note 3) Signal Level Sensitivity :  $\Delta V / \Delta v$

Measure each output voltage of pin 19 at  $v_{in} = -40$ , -60 dBmW (50 $\Omega$ )  $\Delta V/\Delta V = (V_{-60} - V_{-40})/20$  mV/dB

(Note 4) VCO Conversion Sensitivity :  $\beta$

Input f = 402.78MHz and sweep  $\pm$  5MHz,  $v_{in}$  = - 30dBmW (50 $\Omega$ ) to pin 20. Calculate  $\beta$  = 10 / (Vdet  $_{+}$  5 - Vdet  $_{-}$  5) and multiply the gain portion (2.66) of video amplifier when outputting a direct current voltage to pin 3 at 407.78MHz, 397.78MHz as Vdet  $_{+}$  5 and Vdet  $_{-}$  5 each.

(Note 5) VCO Temperature Drift : ∆fTa

Short pin 6 and 7, and connect pin 14 to GND. Measure the VCO frequency at ambient temperature  $Ta = 25^{\circ}C$ ,  $-10^{\circ}C + 65^{\circ}C$  and calculate how much frequency changes from at 25°C. (read out the VCO leakage output by spectrum analyzer.)

(Note 6) PLL Lock Range: fL, Capture Range: fca

Measure the range that synchronizes with VCO by putting pin 20 input frequency away from the free-running frequency.

(Note 7) Demodulation Output Level: Vout

Input pin 20 f = 402.78MHz,  $f_m$  = 100kHz,  $\Delta_f$  = 10MHz<sub>p-p</sub>,  $v_{in}$  = - 30dBmW (50 $\Omega$ ) Open pin 4 and 5 and measure the output level of pin 3.

(Note 8) Video Amplifier Variable Width: Vouts Vouts

Input pin 20 f = 402.78MHz,  $f_m$  = 100kHz,  $\Delta f$  = 10MHz<sub>p-p</sub>,  $v_{in}$  = - 30dBmW (50 $\Omega$ ) Measure the variation of video output by shorting between pin 4 and 5 and connecting a 5k $\Omega$  resistance.

(Note 9) Demodulation Output level Width, Group Delay Characteristics :  $V_{OutA}$ ,  $\tau_{Pd}$

Input pin 20 f = 402.78MHz,  $f_m$  = 100kHz, 60Hz to 4MHz to 9MHz,  $\Delta f$  = 5MHz<sub>p-p</sub>,  $v_{in}$  = - 30dBmW (50 $\Omega$ )

Compare to the value at 100kHz by opening pin 4 and 5, and measuring the output level and group delay of pin 3.

(Note 10) Keyed Pulse Allowable Period : T<sub>1</sub>

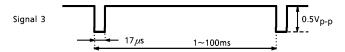

Input pin 20 f = 402.78MHz,  $f_m$  = 100kHz,  $\Delta f$  = 10MHz<sub>p-p</sub>,  $v_{in}$  = - 30dBmW (50 $\Omega$ ) Input the signal below to pin 1 and open pin 27 and 28.

Observe the pin 23 output and change f so as to be 2.5V voltage.

Measure the frequency range in which a 2kHz sine wave does not output to pin 23, by changing the signal 3 period.

If the sample-hold circuit malfunctions, the 2kHz sine wave will be outputted from pin 23.

(Note 11) AFT Sensitivity :  $\Delta f/\Delta V_{23}$

Input pin 20 f = 402.78MHz  $\pm$  1MHz,  $v_{in}$  = - 30dBmW (50 $\Omega$ )

Adjust f so that pin 23 output will be 2.5V. By moving f up. and down, calculate each frequency as  $f_H$ ,  $f_L$  when pin 23 voltage varies 0.5V using the following equation.

$\Delta f / \Delta V_{23} = f_H - f_L (MHz / V)$

(Note 12) AFT Digital Output Width of dead zone : fDEAD

Input pin 20 f = 402.78MHz  $\pm$  5MHz,  $v_{in} = -30dBmW$  (50 $\Omega$ )

Measure the input frequency range in which both pin 24 and 25 become high level, by sweeping f.

(Note 13) DG, DP

Input pin 20 f = 402.78MHz  $\pm$  5MHz,  $v_{in}$  = - 30dBmW (50 $\Omega$ ),  $\Delta$ f = 17MHz<sub>p-p</sub>, Gray level video signal (APL : 10~90%)...Pre-emphasis-on

(Note 14) IM2, IM3

Input pin 20 f = 402.78MHz  $\pm$  5MHz,  $v_{in}$  = - 30dBmW (50 $\Omega$ ),  $\Delta$ f = 17MHz<sub>p-p</sub>, Color subcarrier (3.579MHz), Sound subcarrier (5.7272MHz) ...

Observe the frequency component outputting to the screen output pin (pin 3) through the video gate of a video noise meter by spectrum analyzer, and measure the level difference between 3.579MHz component and 2.15MHz, 1.43MHz components.

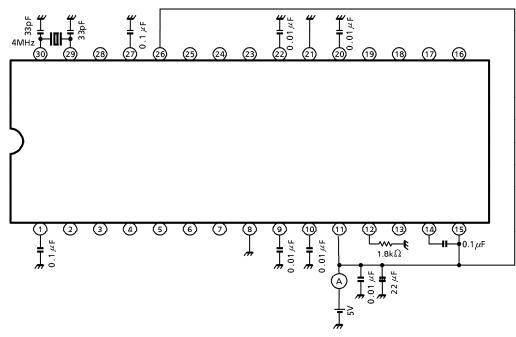

**TEST CIRCUIT 1**

#### DC characteristics

#### **TEST CIRCUIT 2**

TA8899AF - 14

#

Weight: 0.63g (Typ.)