# Features

- Low-power, Low-voltage Operation

- Contactless Power Supply

- Contactless Read/Write Data Transmission

- Radio Frequency (RF): 100 kHz to 150 kHz

- 264-bit EEPROM Memory in 8 Blocks of 33 Bits

- 224 Bits in Seven Blocks of 32 Bits are Free for User Data

- Block Write Protection

- Extensive Protection Against Contactless Malprogramming of the EEPROM

- On-chip Resonance Capacitor (70 or 200 pF Mask Option)

- Anticollision Using Answer-On-Request (AOR)

- Typical < 50 ms to Write and Verify a Block</li>

- Other Options Set by EEPROM:

- Bitrate [bit/s]: RF/8, RF/16, RF/32, RF/40, RF/50, RF/64, RF/100, RF/128

- Modulation: BIN, FSK, PSK, Manchester, Biphase

- Other: Terminator Mode, Password Mode, AOR Mode

# Description

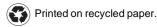

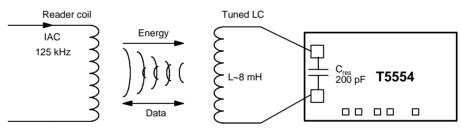

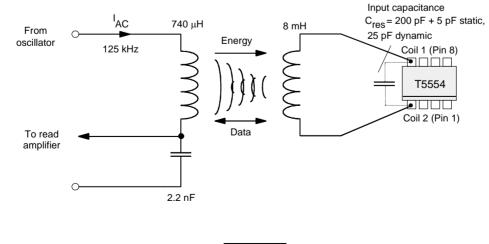

The T5554 is a contactless R/W-ID entification IC (IDIC<sup>®</sup>) for general-purpose applications in the 125 kHz range. A single coil, connected to the chip, serves as the IC's power supply and bidirectional communication interface. The coil and chip together form a transponder.

The on-chip 264-bit EEPROM (8 blocks 33 bits each) can be read and written blockwise from a base station. The blocks can be protected against overwriting. One block is reserved for setting the operation modes of the IC. Another block can contain a password to prevent unauthorized writing.

Reading occurs by damping the coil by an internal load. There are different bitrates and encoding schemes possible. Writing occurs by interrupting the RF field in a special way.

# System Block Diagram

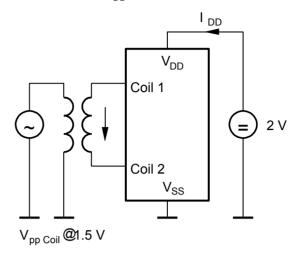

Figure 1. RFID System Using T5554 Tag

Standard R/W IDIC (264 Bit) with Integrated Capacitance

# T5554

# Preliminary

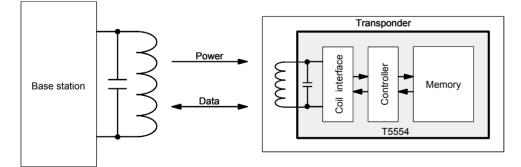

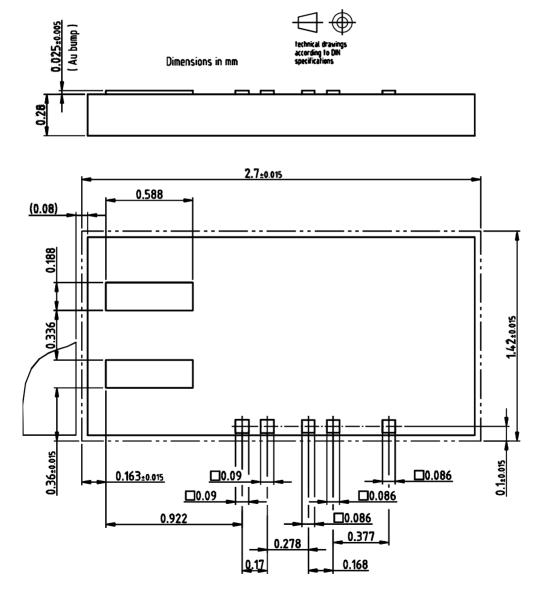

# **Pad Layout**

Figure 2. Pad Layout of T5554

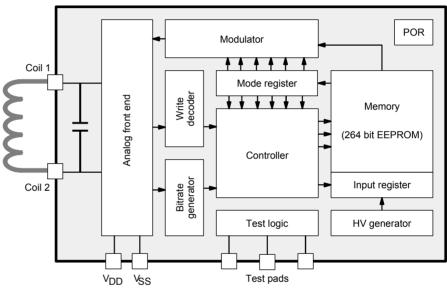

# **T5554 Building Blocks**

# Analog Front End (AFE) The AFE includes all circuits which are directly connected to the coil. It generates the IC's power supply and handles the bidirectional data communication with the reader unit. It consists of the following blocks:

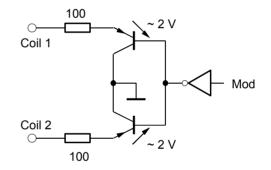

- Rectifier to generate a DC supply voltage from the AC coil voltage

- Clock extractor

- Switchable load between Coil1/Coil2 for data transmission from the IC to the reader unit (read)

- Field gap detector for data transmission from the reader unit into the IC (write)

# **Resonance Capacitor** The resonance capacitor is integrated on chip. By mask option the value can be 70 pF or 200 pF typically.

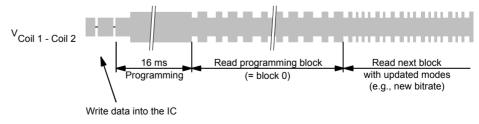

| Controller           | <ul> <li>The main controller has the following functions:</li> <li>Load mode register with configuration data from EEPROM block 0 after power-on and also during reading</li> <li>Control memory access (read, write)</li> <li>Handle write data transmission and the write error modes</li> <li>The first two bits of the write data stream are the OP-code. There are two valid OP-codes (standard and stop) which are decoded by the controller.</li> <li>In password mode, the 32 bits received after the OP-code are compared with the stored password in block 7.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bitrate Generator    | The bitrate generator can deliver the following bitrates:<br>RF/8 – RF/16 – RF/32 – RF/40 – RF/50 – RF/64 – RF/100 – RF/128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Write Decoder        | Decode the detected gaps during writing. Check if write data stream is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Test Logic           | Test circuitry allows rapid programming and verification of the IC during test.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HV Generator         | Voltage pump which generates ~18 V for programming of the EEPROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Power-On Reset (POR) | The power-on reset is a delay reset which is triggered when supply voltage is applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mode Register        | The mode register stores the mode data from EEPROM block 0. It is continually refreshed at the start of every block. This increases the reliability of the device (if the originally loaded mode information is false, it will be corrected by subsequent refresh cycles).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

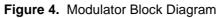

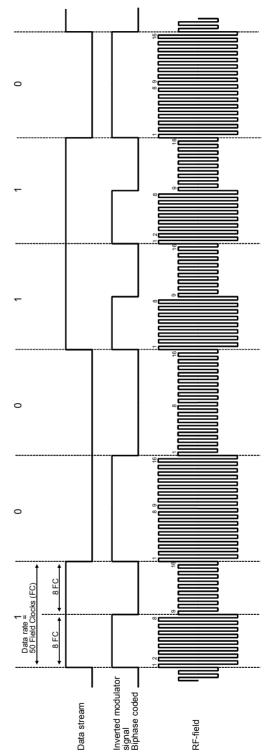

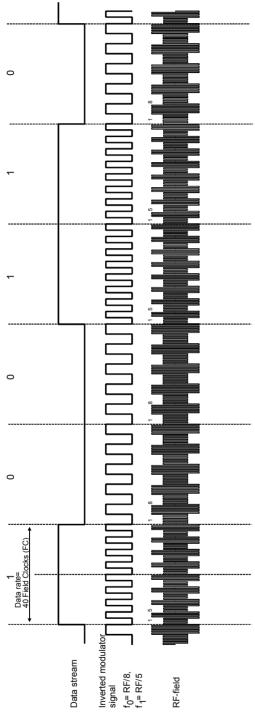

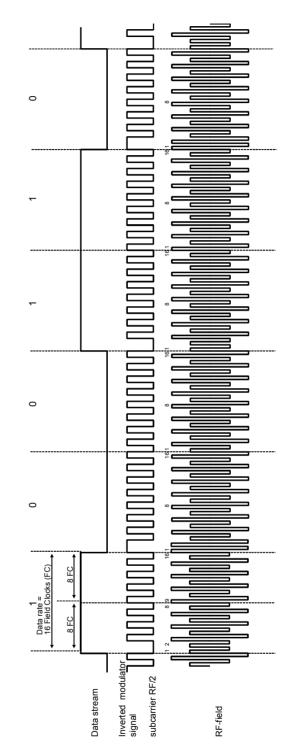

| Modulator            | <ul> <li>The modulator consists of several data encoders in two stages, which may be freely combined to obtain the desired modulation. The basic types of modulation are:</li> <li>PSK: phase shift: 1) every change; 2) every "1"; 3) every rising edge (carrier: fc/2, fc/4 or fc/8)</li> <li>FSK: 1) f1 = rf/8 f2 = rf/5; 2) f1 = rf/8, f2 = rf/10</li> <li>Manchester: rising edge = H; falling edge = L</li> <li>Biphase: every bit creates a change, a data "H" creates an additional mid-bit change Note: The following modulation type combinations will not work:</li> <li>Stage1 Manchester or Biphase and stage2 PSK, at any PSK carrier frequency (because the first stage output frequency is higher than the second stage strobe frequency);</li> <li>Stage1 Manchester or Biphase and stage2 PSK with bitrate = rf/8 and PSK carrier frequency = rf/8 (for the same reason as above);</li> <li>Any stage1 option with any PSK for bitrates rf/50 or rf/100 if the PSK carrier frequency is not an integer multiple of the bitrate (e.g., br = rf/50, PSKcf = rf/4, because 50/4 = 12.5). This is because the PSK carrier frequency must maintain constant phase with respect to the bit clock.</li> </ul> |

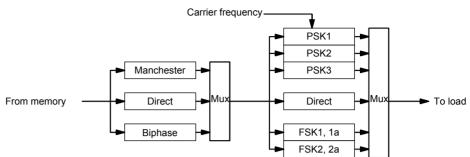

## Memory

The memory of the T5554 is a 264-bit EEPROM, which is arranged in 8 blocks of 33 bits each. All 33 bits of a block, including the lock bit, are programmed simultaneously. The programming voltage is generated on-chip.

Block 0 contains the mode data, which are not normally transmitted (see figure 6).

Blocks 1 to 6 are freely programmable. Block 7 may be used as a password. If password protection is not required, it may be used for user data.

Bit 0 of every block is the lock bit for that block. Once locked, the block (including the lockbit itself) cannot be field-reprogrammed.

Data from the memory is transmitted serially, starting with block 1, bit 1, up to block "MAXBLK", bit 32. "MAXBLK" is a mode parameter set by the user to a value between 0 and 7 (if maxblk = 0, only block 0 will be transmitted).

## Figure 5. Memory Map

# Figure 6. Memory Map of Block 0

|                                                                                                                                                                                                                                                                                                |                  |                                        |                      |                                              |                                 |                                      |                                              |                             |                      |                            |                         |                   |                    |          |                            |                     |                       |       | I                        |      |            |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------|----------------------|----------------------------------------------|---------------------------------|--------------------------------------|----------------------------------------------|-----------------------------|----------------------|----------------------------|-------------------------|-------------------|--------------------|----------|----------------------------|---------------------|-----------------------|-------|--------------------------|------|------------|-------------|

| ) 1                                                                                                                                                                                                                                                                                            | 11 12            | 13                                     | 14                   | 15                                           | 16                              | 17                                   | 18                                           | 19                          | 20                   | 21                         | 22                      | 2 2               | 3                  | 24       | 25                         | 26                  | 2                     | 72    | 8 2                      | 29   | 30         | 31 3        |

| reserved                                                                                                                                                                                                                                                                                       | [2]              | BR<br>[1]                              | [0]                  |                                              |                                 | S1<br>[0]                            | [2]                                          | /IS2<br>[1]                 |                      |                            |                         | I                 |                    |          |                            | AXE<br>[1]          |                       |       |                          |      |            | <br>re      |

| lock bit (never transmitted)                                                                                                                                                                                                                                                                   |                  |                                        | 1                    | *<br>"0"                                     |                                 |                                      |                                              |                             |                      |                            |                         | AC                |                    | *<br>"0" |                            |                     |                       |       | u<br>seP                 | seS  | useE<br>ST | useS⊺<br>8T |

| Key:<br>ACR Anwer-On-Request<br>T use Block Terminator<br>T use Sequence Terminator<br>WD use Password<br>TOP obey stop header (active low!)<br>R Bit Rate<br>MS1 Modulator Stage 1<br>MS2 Modulator Stage 2<br>PSKCF PSK Clock Frequency<br>MAXBLK see Maxblock feature<br>seerved do not use |                  |                                        |                      |                                              |                                 |                                      |                                              |                             |                      |                            |                         |                   |                    |          | 0<br>0<br>0<br>1<br>1<br>1 | 1<br>1<br>0<br>1    | 1<br>0<br>1<br>0<br>1 | 0     | ) 3<br>) 4<br>) 5<br>) 6 | oloc | ks:        |             |

| Bit 15 and 24 must always be at "0",<br>otherwise malfunction will appear.                                                                                                                                                                                                                     |                  |                                        |                      |                                              |                                 |                                      |                                              |                             |                      | 0<br>1<br>1<br>irect       | 1<br>0<br>1             |                   | 7/4<br>7/8<br>serv |          | ae w                       | /hen                | inr                   | outo  | cha                      | nae  | s)         |             |

|                                                                                                                                                                                                                                                                                                |                  |                                        |                      |                                              |                                 |                                      | 0                                            | 1 C<br>1 1<br>              | ) ps<br>ps<br>/p fre | sk2<br>sk3<br>eq.          | (ph<br>(ph<br>(ph<br>DA | ase<br>ase<br>ATA | ch<br>ch<br>=1     | ang      | je o<br>je o               | n bit<br>n ris<br>- | tclk                  | if ir | nput                     | ĥig  | h)         |             |

|                                                                                                                                                                                                                                                                                                |                  |                                        |                      |                                              |                                 |                                      | 1<br>1                                       | 0 1<br>1 C                  | l fs<br>) fs         | sk1<br>sk2<br>sk1a<br>sk2a | rf/8<br>rf/             | 3 rl<br>75        | f/10<br>rf/8       | 3        |                            |                     |                       |       |                          |      |            |             |

|                                                                                                                                                                                                                                                                                                |                  |                                        |                      |                                              | 0<br>1                          | 1 N<br>0 E                           | lirect<br>Aanc<br>Bipha<br>eserv             | hes<br>se                   | ter                  |                            |                         |                   |                    |          |                            |                     |                       |       |                          |      |            |             |

|                                                                                                                                                                                                                                                                                                | 0<br>0<br>1<br>1 | 0 1<br>1 0<br>1 1<br>0 0<br>1 1<br>1 0 | ) RF<br>  RF<br>  RF | -/16<br>-/32<br>-/40<br>-/50<br>-/64<br>-/10 | bit<br>bit<br>bit<br>bit<br>bit | rate<br>rate<br>rate<br>rate<br>rate | _16c<br>_32c<br>_40c<br>_50c<br>_64c<br>e_10 | pb<br>pb<br>pb<br>pb<br>0cp |                      |                            |                         |                   |                    |          |                            |                     |                       |       |                          |      |            |             |

# **Operating the T5554**

| General          | The basic functions of the T5554 are: supply IC from the coil, read data from the EEPROM to the reader, write data into the IC and program these data into the EEPROM. Several errors can be detected to protect the memory from being written with the wrong data (see figure 21).                                                                                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply           | The T5554 is supplied via a tuned inductance (L ~ 8 mH) which is connected to the Coil 1 and Coil 2 pads. The incoming RF (actually a magnetic field) induces a current into the coil. The on-chip rectifier generates the dc supply voltage ( $V_{DD}$ , $V_{SS}$ pads). Overvoltage protection prevents the IC from damage due to high-field strengths. Depending on the coil, the open-circuit voltage across the LC circuit can reach more than 100 V. The first occurrence of RF triggers a power-on reset pulse, ensuring a defined start-up state. |

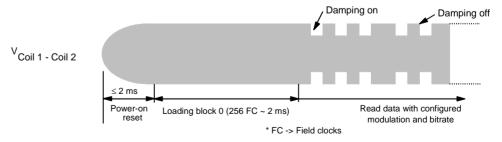

| Read             | Reading is the default mode after power-on reset. It is done by switching a load between the coil pads on and off. This changes the current through the IC coil, which can be detected from the reader unit.                                                                                                                                                                                                                                                                                                                                              |

| Start-up         | The many different modes of the T5554 are activated after the first readout of block 0. The modulation is off while block 0 is read. After this set-up time of 256 field clock periods, modulation with the selected mode starts.                                                                                                                                                                                                                                                                                                                         |

|                  | Any field gap during this initialization will restart the complete sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Read Data Stream | The first block transmitted is block 1. When the last block is reached, reading restarts with block 1. Block 0, which contains mode data, is normally never transmitted. How-<br>ever, the mode register is continuously refreshed with the contents of EEPROM block 0.                                                                                                                                                                                                                                                                                   |

## Figure 7. Application Circuit

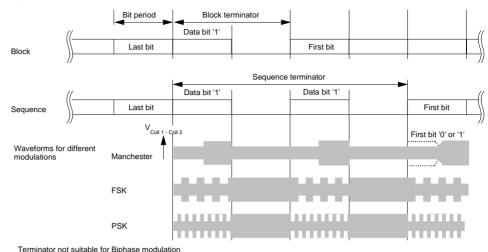

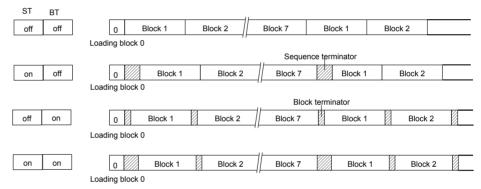

Figure 9. Terminators

#### Figure 11. MAXBLK Examples

| MAXBLK = 5 | 0 Block 1                    | Block 4 | Block 5 | Block 1 | Block 2 | _ |

|------------|------------------------------|---------|---------|---------|---------|---|

|            | Loading block 0              |         |         |         |         |   |

| MAXBLK = 2 | 0 Block 1<br>Loading block 0 | Block 2 | Block 1 | Block 2 | Block 1 | _ |

| MAXBLK = 0 | 0 Block 0                    | Block 0 | Block 0 | Block 0 | Block 0 |   |

Maxblock FeatureIf it is not necessary to read all user data blocks; the MAXBLK field in block 0 can be<br/>used to limit the number of blocks read. For example, if MAXBLK = 5, the T5554 repeat-<br/>edly reads and transmits only blocks 1 to 5 (see figure 11). If MAXBLK is set to "0", block<br/>0 - which is normally not transmitted - can be read.

**Terminators** The terminators are (optionally selectable) special damping patterns, which may be used to synchronize the reader. There are two types available; a block terminator which precedes every block, and a sequence terminator which always follows the last block.

|  | R |

|--|---|

The sequence terminator consists of two consecutive block terminators. The terminators may be individually enabled with the mode bits ST (Sequence Terminator enable) or BT (Block Terminator enable).

Note: It is not possible to include a sequence terminator in a transmission where MAXBLK = 0.

Direct Access

The direct access command allows the reading of an individual block by sending the OP-code ("10"), the lock-bit and the 3-bit address.

Note:

PWD has to be 0.

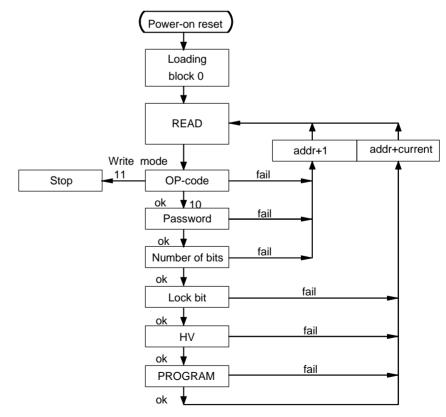

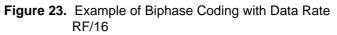

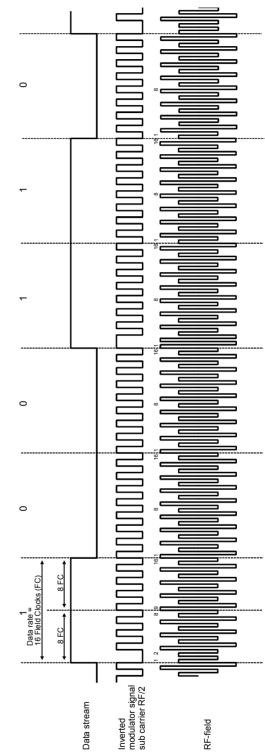

**Modulation and Bitrate** There are two modulator stages in the T5554 (see figure 4) whose mode can be selected using the appropriate bits in block 0 (MS1[1:0] and MS[2:0]). Also the bitrate can be selected using BR[2:0] in block 0. These options are described in detail in figures 21 through 26.

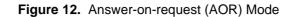

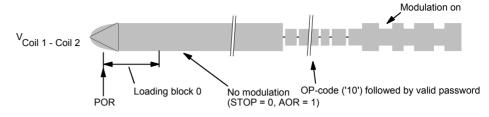

Answer-On-Request<br/>Mode (AOR)When the AOR bit is set, the IDIC does not start modulation after loading configuration<br/>block 0. It waits for a valid AOR data stream (wake-up command) from the reader before<br/>modulation is enabled.

The wake-up command consists of the OP-code ("10") following by a valid password. The IC will remain active until the RF field is turned off or a stop OP-code is received.

| PWD | AOR | STOP | Behavior of Tag after Reset/POR                                                                                           | STOP Function                                                                 |

|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 1   | 1   | 0    | Anticollision mode:<br>Modulation starts after wake-up<br>with a matching PWD                                             | STOP OP-code ("11") defeats<br>modulation until RF field is<br>turned off     |

|     |     |      | <ul> <li>Programming needs valid PWD</li> <li>AOR allows programing with read protection (no read after write)</li> </ul> |                                                                               |

| 1   | 0   | 0    | Password mode:                                                                                                            | -                                                                             |

|     |     |      | Modulation starts after reset                                                                                             |                                                                               |

|     |     |      | Programming needs valid PWD                                                                                               |                                                                               |

| 0   | 1   | 0    | Modulation starts after wake-up command                                                                                   |                                                                               |

|     |     |      | <ul> <li>Programming with modulation defeat without previous wake-up<br/>possible</li> </ul>                              |                                                                               |

|     |     |      | AOR allows programing with read protection (no read after write)                                                          |                                                                               |

| 0   | 0   | 0    | Plain/Normal mode:                                                                                                        |                                                                               |

|     |     |      | Modulation starts after reset                                                                                             |                                                                               |

|     |     |      | Direct access command                                                                                                     |                                                                               |

|     |     |      | Programming without password                                                                                              |                                                                               |

| х   | 0   | 1    | See corresponding modes above                                                                                             | STOP OP-code ignored,<br>modulation continues until RF<br>field is turned off |

Table 1.

T5554 - Modes of Operation

Figure 13. Anticollision Procedure Using AOR Mode

Figure 16. T5554 – OP-code Formats

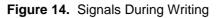

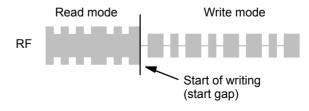

Writing data into the IC occurs via the Atmel write method. It is based on interrupting the RF field with short gaps. The time between two gaps encodes the "0/1" information to be transmitted.

Start GapThe first gap is the start gap which triggers write mode. In write mode, the damping is<br/>permanently enabled which eases gap detection. The start gap may need to be longer<br/>than subsequent gaps in order to be detected reliably.

A start gap will be detected at any time after block 0 has been read (field-on plus approximately 2 ms).

Figure 17. Start of Writing

Write

| Decoder                        | The duration of the gaps is usually 50 to 150 $\mu$ s. The time between two gaps is nomi-<br>nally 24 field clocks for a "0" and 56 field clocks for a "1". When there is no gap for more<br>than 64 field clocks after previous gap, the IDIC exits write mode; it starts with program-<br>ming if the correct number of valid bits were received. |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | If there is a gap fail - i.e., one or more of the intervals did represent not a valid "0" or "1" - the IC does not program, but enters read mode beginning with block 1, bit 1.                                                                                                                                                                     |

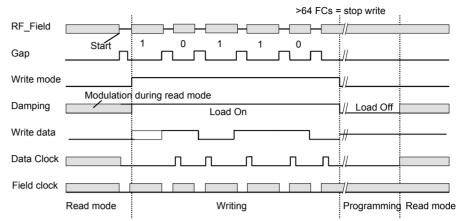

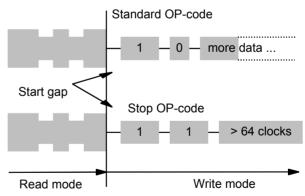

| Writing Data into the<br>T5554 | The T5554 expects a 2-bit OP-code first. There are two valid OP-codes ("10" and "11"). If the OP-code is invalid, the T5554 starts read mode beginning with block 1 after the last gap. The OP-code ("10") is followed by different information (see figure 17):                                                                                    |

|                                | <ul> <li>Standard writing needs the OP-code, the lock bit, the 32 data bits and the 3-bit block<br/>address.</li> </ul>                                                                                                                                                                                                                             |

|                                | <ul> <li>Writing with usePWD set requires a valid password between OP-code and<br/>address/data bits.</li> </ul>                                                                                                                                                                                                                                    |

|                                | <ul> <li>In AOR mode with usePWD, OP-code and a valid password are necessary to<br/>enable modulation.</li> </ul>                                                                                                                                                                                                                                   |

|                                | <ul> <li>The STOP OP-code is used to silence the T5554 (disable damping until power is cycled).</li> </ul>                                                                                                                                                                                                                                          |

|                                | Note: The data bits are read in the same order as written.                                                                                                                                                                                                                                                                                          |

| STOP OP-code                   | The STOP OP-code ("11") is used to disable the modulation until a power-on reset occurs. This feature can be used to have a steady RF field where single transponders are collected one by one. Each IC is read and than disabled, so that it does not interfere with the next IC.                                                                  |

|                                | Note: The STOP OP-code should contain only the two OP-code bits to disable the IC. Any                                                                                                                                                                                                                                                              |

Note: The STOP OP-code should contain only the two OP-code bits to disable the IC. Any additional data sent will not be ignored, and the IC will not stop modulation.

Figure 18. OP-code Transmission

| Password    | When password mode is on (usePWD = 1), the first 32 bits after the OP-code are regarded as the password. They are compared bit-by-bit with the contents of block 7, starting at bit 1. If the comparison fails, the IC will not program the memory, but restart in read mode at block 1 once writing has completed.                                                                                                                                                                                                                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | <ol> <li>If PWD is not set, but the IC receives a write datastream containing any 32 bits in place of a password, the IC will enter programming mode.</li> <li>In password mode, MAXBLK should be set to a value below 7 to prevent the password from being transmitted by</li> <li>Every transmission of 2 OP-code bits, 32 password bits, one lock bit, 32 data bits and 3 address bits (= 70 bits) needs about 35 ms. Testing all 232 possible combinations (about 4.3 billion) takes about 40,000 h, or over four years. This is a sufficient password protection for a general-purpose IDIC.</li> </ol> |

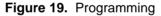

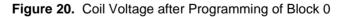

| Programming | When all necessary information has been written to the T5554, programming may pro-<br>ceed. There is a 32-clock delay between the end of writing and the start of pro-<br>gramming. During this time, Vpp - the EEPROM programming voltage - is measured<br>and the lock bit for the block to be programmed is examined. Furthermore, Vpp is con-<br>tinually monitored throughout the programming cycle. If at any time Vpp is too low, the                                                                                                                                                                 |

The programming time is 16 ms.

chip enters read mode immediately.

After programming is done, the T5554 enters read mode, starting with the block just programmed. If either block or sequence terminators are enabled, the block is preceded by a block terminator. If the mode register (block 0) has been reprogrammed, the new mode will be activated after the just-programmed block has been transmitted using the previous mode.

# Error Handling Several error conditions can be detected to ensure that only valid bits are programmed into the EEPROM. There are two error types which lead to different actions. Errors During Writing There are four detectable errors which could occur during writing data into the T5554: Wrong number of field clocks between two gaps The OP-code is neither the standard OP-code ('10') nor the stop OP-code ('11') Password mode is active but the password does not match the contents of block 7 The number of bits received is incorrect; valid bit counts are Standard write 38 bits (PWD not set)

- Password write 70 bits (PWD set)

- AOR wake-up 34 bits

- Stop command 2 bits

If any of these four conditions are detected, the IC starts read mode immediately after leaving write mode. Reading starts with block 1.

If writing was successful, the following errors could prevent programming:

- The lock bit of the addressed block is set

- V<sub>PP</sub> is too low

In these cases, programming stops immediately. The IC reverts to read mode, starting with the currently addressed block.

#### Figure 21. Functional Diagram of the T5554

**Errors During**

Programming

Figure 22. Example of Manchester Coding with Data Rate RF/16

**Figure 24.** Example of FSK Coding with Data Rate RF/40 Subcarrier  $f_0 = RF/8$ ,  $f_1 = RF/5$ ,

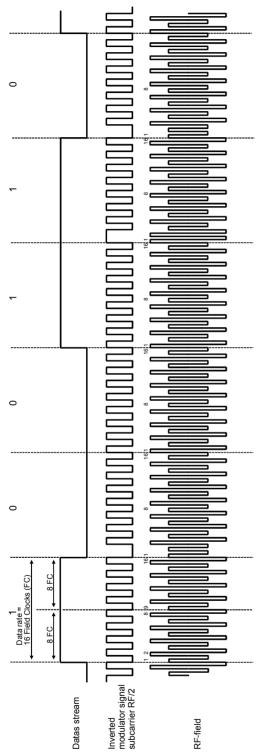

Figure 25. Example of PSK Coding with Data Rate RF/16

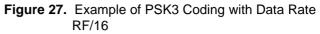

Figure 26. Example of PSK2 Coding with Data Rate RF/16

Figure 29. Simplified Damping Circuit

# **Application Example**

Figure 30. Typical Application Circuit

# **Absolute Maximum Ratings**

| Parameters                                                              | Symbol              | Value       | Unit |

|-------------------------------------------------------------------------|---------------------|-------------|------|

| Maximum DC current into Coil 1/Coil 2                                   | I <sub>coil</sub>   | 10          | mA   |

| Maximum AC current into Coil 1/Coil 2, f = 125 kHz                      | I <sub>coil p</sub> | 20          | mA   |

| Power dissipation (dice) (free-air condition, time of application: 1 s) | P <sub>tot</sub>    | 100         | mW   |

| Electrostatic discharge maximum to<br>MIL-Standard 883 C method 3015    | V <sub>max</sub>    | 2           | kV   |

| Operating ambient temperature range                                     | T <sub>amb</sub>    | -40 to +85  | °C   |

| Storage temperature range (data retention reduced)                      | T <sub>stg</sub>    | -40 to +150 | °C   |

| Maximum assembly temperature for less than 5 min                        | T <sub>sld</sub>    | 150         | °C   |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

# **Electrical Characteristics**

| Parameters                        | Test Conditions                                | Symbol                             | Min.        | Тур. | Max. | Unit   |

|-----------------------------------|------------------------------------------------|------------------------------------|-------------|------|------|--------|

| RF frequency range                |                                                | f <sub>RF</sub>                    | 100         | 125  | 150  | kHz    |

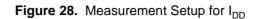

| Supply current<br>(see figure 28) | Read and write over the full temperature range | I <sub>DD</sub>                    |             | 5    | 7.5  | μA     |

| Supply current<br>(see figure 28) | Programming over the full temperature range    | I <sub>DD</sub>                    |             | 100  | 200  | μA     |

| Clamp voltage                     | 10 mA current into Coil1/2                     | V <sub>cl</sub>                    | 9.5         |      | 11.5 | V      |

| Programming voltage               | From on-chip HV-Generator                      | V <sub>pp</sub>                    | 16          |      | 20   | V      |

| Programming time                  |                                                | t <sub>P</sub>                     |             | 18   |      | ms     |

| Startup time                      |                                                | t <sub>startup</sub>               |             |      | 4    | ms     |

| Data retention (1)                |                                                | t <sub>retention</sub>             | 10          |      |      | Years  |

| Programming cycles (1)            |                                                | n <sub>cycle</sub>                 | 100,00<br>0 |      |      | Cycles |

| Supply voltage                    | Read and write                                 | V <sub>DD</sub>                    |             |      | 1.6  | V      |

| Supply voltage                    | Read-mode, T = -30°C                           | V <sub>DD</sub>                    |             |      | 2.0  | V      |

| Coil voltage                      | Read and write                                 | V <sub>coil pp</sub>               |             |      | 6.0  | V      |

| Coil voltage                      | Programming,<br>RF field not damped            | V <sub>coil pp</sub>               |             |      | 10   | V      |

| Resonance capacitor               |                                                | C <sub>res(A)</sub> <sup>(2)</sup> | 63          | 70   | 77   | pF     |

| Resonance capacitor               |                                                | C <sub>res(B)</sub> <sup>(2)</sup> | 180         | 200  | 220  | pF     |

| Damping resistor                  |                                                | R <sub>D</sub>                     |             | 300  |      | W      |

Notes: 1. Since EEPROM performance may be influenced by assembly and packaging, Atmel confirms the parameters for DOW (= die-on-wafer) and ICs assembled in standard package.

2. Tolerance/wafer ±4%; tolerance / lot ±5%; typical value selected by mask option

# **Ordering Information**

| Extended Type Number | Package                           | Remarks                                                            |

|----------------------|-----------------------------------|--------------------------------------------------------------------|

| T5554401-DBN         | Au-bumped 25 µm<br>chip on sticky | 200 pF capacitor; default programming: all 0; EEPROM memory erased |

| T5554402-DBN         |                                   | 70 pF capacitor; default programming: all 0; EEPROM memory erased  |

| T5554403-DBN         | NiAu-bumped 15 µm                 | 200 pF capacitor; default programming: all 0; EEPROM memory erased |

| T5554404-DBN         | chip on sticky                    | 70 pF capacitor; default programming:all 0; EEPROM memory erased   |

# **Chip Dimensions**

#### **Atmel Headquarters**

*Corporate Headquarters* 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### **Microcontrollers**

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

#### *Biometrics/Imaging/Hi-Rel MPU/*

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel<sup>®</sup> is the registered trademark of Atmel.

IDIC® stands for IDentification Integrated Circuit and is a trademark of Atmel Germany GmbH.

Other terms and product names may be the trademarks of others.