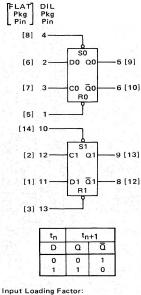

**DUAL TYPE D FLIP-FLOP**

# MC5479 · MC7479

Add Suffix F for TO-86 ceramic package (Case 607). Suffix L for TO-116 ceramic package (Case 632). Suffix P for TO-116 plastic package (Case 605) MC7479 only.)

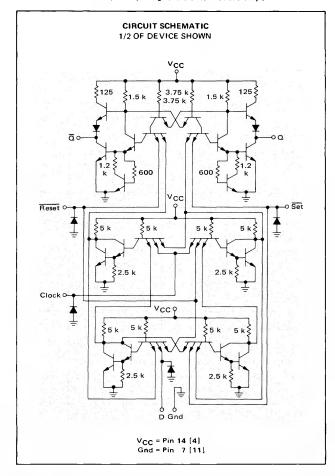

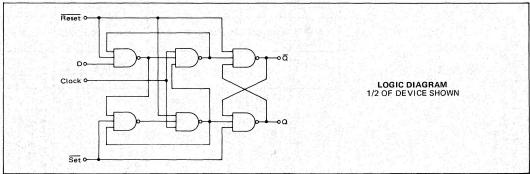

This dual type D flip-flop triggers on the positive edge of the clock input. During the clock transition the state of the D input is transferred to the Q output. The device is useful in shift registers and simple counters.

D = 1 Set, Clock = 2 Reset = 3

Output Loading Factor = 10 Total Power Dissipation = 84 mW typ/pkg Propagation Delay Time = 16 ns typ Operating Frequency = 30 MHz typ

| ELECTRICAL CHARACTERISTICS Test procedures are shown for only one flip-flop. The other flip-flop is tested in the same manner. | CTERIS'<br>n for only<br>lop is test                 | TICS<br>one<br>ed in | P. P | (8) (8) (9) (9) (9) (9) (9) (9) (9) (9) (9) (9 | 00 00 00       |         | [6] 9                 |              |                |             |            |          |                  |                                                   |         |          |        |         |                                       |                                |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|------------------------------------------|------------------------------------------------|----------------|---------|-----------------------|--------------|----------------|-------------|------------|----------|------------------|---------------------------------------------------|---------|----------|--------|---------|---------------------------------------|--------------------------------|

| > 0<br>  <br>                                                                                                                  | V = V <sub>CC</sub> = Pin 14 [4]<br>Gnd = Pin 7 [11] | 14 [4]<br>7 [11]     | 2 2 5                                    | [7] 3—<br>[5] 1—<br>[14] 10—                   |                |         | 6 [10]                |              |                |             |            |          |                  |                                                   |         |          |        |         |                                       |                                |

|                                                                                                                                |                                                      |                      |                                          |                                                | ⊸er.           |         |                       |              |                |             | TEST CL    | IRRENT   | VOLTA            | TEST CURRENT/VOLTAGE VALUES (All Temperatures)    | ES (All | Tempera  | tures) |         | -                                     |                                |

|                                                                                                                                |                                                      |                      | _                                        | [2] 12—                                        | 5<br>T         | ō<br>ō  | -9 [13]               | 1            | Аш             |             |            |          |                  | _                                                 | Volts   |          |        |         |                                       |                                |

|                                                                                                                                |                                                      |                      |                                          | -11 111                                        | - <del>-</del> | <u></u> | -8 [12]               |              | ا <sub>0</sub> | _ <u>e</u>  | >=         | ٧<br>٣   | VIHH             | VRI                                               | V#1     | Vtho     | Vcc    | VccL    | VCCH                                  |                                |

|                                                                                                                                |                                                      |                      |                                          |                                                | £ >-           | 7       | ž:                    | MC5479       | 16             | -0.4        | 0.4        | $\vdash$ |                  | +-+                                               | -       | +        |        | + +     |                                       |                                |

|                                                                                                                                |                                                      | .E                   |                                          | MC5479<br>Test Limits                          | 2              |         | MC7479<br>Test Limits | MC 477       | 10             | -0.4<br>TES | T CURR     | ENT/VO   | LTAGE            | TEST CURRENT/VOLTAGE APPLIED TO PINS LISTED BELOW | TO PIN  | S LISTED | BELOW  | 2       | for all tests in addition to the pins | grounded<br>s in addi-<br>pins |

| Characteristic                                                                                                                 | Symbol                                               | Under                | Min Ain                                  | -55 to +125 C                                  | Unit           | Win     | 0 to +70°C            | - tim        | lor            | -E          | <b>^</b> " | N H      | V <sub>IHH</sub> | V                                                 | ۷#،     | ٧, ۴, ٥  | Vcc    | VccL    | V <sub>ссн</sub> Gnd                  | -                              |

| Input Forward Current Set Reset Clock                                                                                          |                                                      | Owan                 |                                          | -3.2                                           | mAde           |         | -3.2                  | mAdc         | 11.11.7        | ar is to t  | Owao       | 1        | 1.1.1.1          | R,S<br>D,S                                        |         |          |        |         | C0,C1,D0<br>C0,C1,D0<br>C0,C1         | C1<br>C1<br>C1<br>S2,          |

| Leakage Current D<br>Set<br>Reset<br>Clock                                                                                     | Rı                                                   | Owan                 |                                          | 40<br>80<br>120<br>80                          | μ Adc          | 1111    | 40<br>80<br>120<br>80 | μAdc         | 1 1 1 7        | 3.1.1.1     |            | OSEO     |                  | C,S<br>C*,D,R<br>C*,S                             | 1111    | i i i i  | iriii  |         | V C1,R0<br>C1<br>C1, D0<br>C1,D0,R0   | t0<br>D0<br>J,R0               |

| Set<br>Reset<br>Clock                                                                                                          | <sup>1</sup> R2                                      | OSHO                 | fire                                     | 1:0                                            | mAdc           |         | 1.0                   | mAdc •       |                | 1116        | 1111       |          | ORRO             | C,S<br>C*,D,R<br>C*,S                             | 1.1.1.1 | 1111     | 1111   | 1 1 1 1 | C1,D0,R0                              | t0<br>00<br>0,R0               |

| Output<br>Output Voltage                                                                                                       | NOL.                                                 | 90                   | 1.0                                      | 0.4                                            | Vdc            | 111     | 0.4                   | Vdc          | GIG            | 111         | 100        | 1.0      | 1.1              |                                                   | s H     | N N      | 11     | >>      | - C0,C1,D0<br>- C0,C1,D0              | 0d,<br>0d,                     |

|                                                                                                                                | но                                                   | O, KO,               | 2.4                                      | -1-1                                           | Vde            | 2.4     | i i                   | Vdc<br>Vdc   |                | G,1G,       |            | 1.1      | 1.6              | 11                                                | a s     | SE       | iii    | >>      | - C0,C1,D0<br>- C0,C1,D0              | 88                             |

| Short-Circuit Current                                                                                                          | $^{\mathrm{I}_{\mathrm{SC}}}$                        | 0,10,                | -20                                      | -57                                            | mAdc<br>mAdc   | -18     | -57                   | mAdc<br>mAdc | grij.          |             | 111        | i i      |                  | 1.1                                               | 7.1     | 1.1      | 11     | 4.1     | V C0,50,Q0<br>V C1,R0,Q0              | 00,                            |

| Power Requirements<br>(Total Device)<br>Power Supply Drain                                                                     | Qd.                                                  | >>                   |                                          | 30                                             | mAdc           | 1,0     | 30                    | mAde         |                |             | · ·        | i        |                  | ·                                                 | 1       | ì        | i      |         | V C0,C1,D0                            | C0,C1,D0,D1,S0,S1              |

\*Momentarily ground pin prfor to taking measurement, then set to state indicated.  $^\dagger\text{Only}$  one output should be shorted at a time.

## **OPERATING CHARACTERISTICS**

Data may be applied to the D input any time following 5.0 ns after the leading edge of a clock pulse and 20 ns before the leading edge of the following clock pulse. The state of the D input when the clock changes from the positive logic "0" state to the positive logic "1" state is transferred to the Q output of the flip-flop. The data input cannot be changed between the setup time (20 ns) and the hold time (5.0 ns) without adversely affecting the operation of the flip-flop.

The direct Set and Reset inputs override the clock, and may be applied any time during the operating cycle.

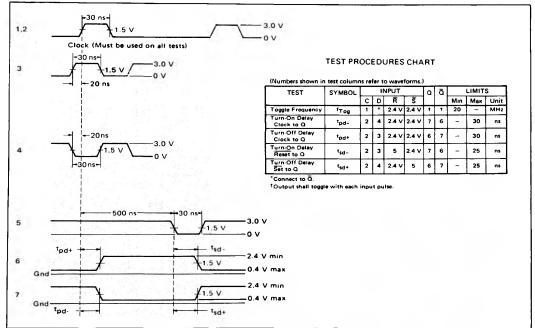

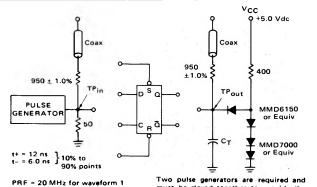

### SWITCHING TIME TEST CIRCUIT

PRF = 20 MHz for waveform 1 = 1.0 MHz for waveforms 2 thru 5

Z thru 5 Z<sub>out</sub>≈50 Ω Two pulse generators are required and must be slaved together to provide the waveforms shown. Only one pulse generator (duty cycle = 50%) is required to test toggle frequency.

The coax delays from input to scope and output to scope must be matched. The scope must be terminated in 50-ohm impedance. The 950-ohm resistor and the scope termination impedance constitute a 20:1 attenuator probe. Coax shall be CT-070-50 or equivalent.

$C_T = 15\ pF =$  total parasitic capacitance, which includes probe, wiring, and load capacitances.

## **VOLTAGE WAVEFORMS AND DEFINITIONS**