## MC1328

## MONOLITHIC DUAL DOUBLY BALANCED CHROMA DEMODULATOR

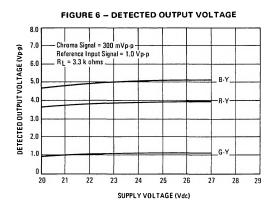

- Good Chroma Sensitivity (0.3 Vp-p Input Produces 5.0 Vp-p Output)

- Good dc Temperature Stability (3 mV/°C typ)

- Low Output dc Offset Voltages (0.6 V max)

- Pin Compatible with ULN-2114, ULN-2114A

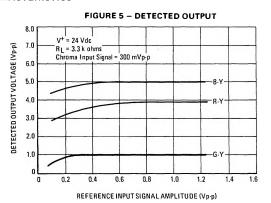

- Negligible Change in Output Voltage Swing With Varying 3.58 MHz Reference Signal

- High Ripple Rejection Due To Built-In MOS Filter Capacitors

- High Output Voltage Swing (10 Vp-p Typ) B-Y

#### DUAL DOUBLY BALANCED CHROMA DEMODULATOR

Monolithic Silicon Integrated Circuit

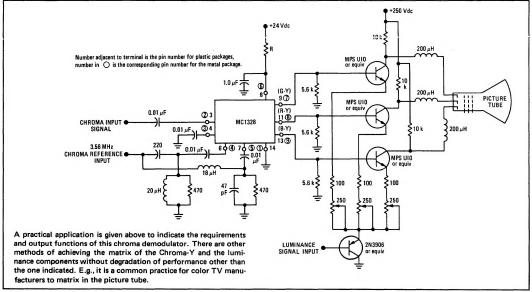

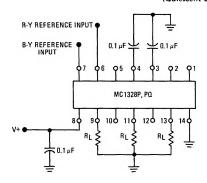

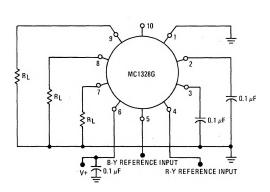

#### FIGURE 1 - MC1328 TYPICAL APPLICATION

### MC1328 (continued)

#### MAXIMUM RATINGS (T<sub>A</sub> = +25°C unless otherwise specified)

| Rating                                                                                                                                        | Value                    | Unit Vdc  mW mW/°C mW mW/°C |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------|--|

| Power Supply Voltage                                                                                                                          | 30                       |                             |  |

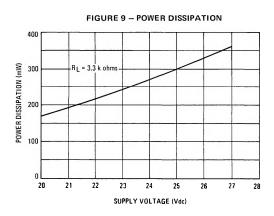

| Power Dissipation (Package Limitation) Plastic Packages Derate above T <sub>A</sub> = +25°C Metal Package Derate above T <sub>A</sub> = +25°C | 625<br>5.0<br>680<br>4.5 |                             |  |

| Chroma Signal Input Voltage                                                                                                                   | 5.0                      | Vpk                         |  |

| Reference Signal Input Voltage                                                                                                                | 5.0                      | Vpk                         |  |

| Minimum Load Resistance                                                                                                                       | 3.0                      | k ohms                      |  |

| Operating Temperature Range (Ambient)                                                                                                         | 0 to +75                 | °C                          |  |

| Storage Temperature Range                                                                                                                     | -65 to +150              | °c                          |  |

Meximum Retings as defined in MIL-S-19500, Appendix A.

ELECTRICAL CHARACTERISTICS (V<sup>+</sup> = 24 Vdc, R<sub>L</sub> = 3.3 k ohms, Reference Input STATIC CHARACTERISTICS Voltage = 1.0 Vp-p, T<sub>A</sub> = +25°C unless otherwise Voltage = 1.0 Vp-p, TA = +25°C unless otherwise noted)

| Characteristic                                                                                                                                                           | Pin No.<br>Suffix G Pkg | Pin No.<br>Suffix P, PQ Pkgs | Min  | Тур  | Max  | Unit  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------|------|------|------|-------|

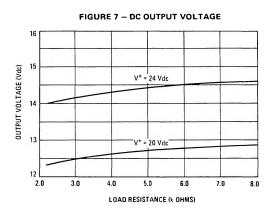

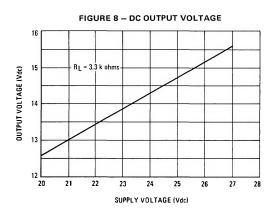

| Quiescent Output Voltage<br>See Figure 2                                                                                                                                 | 7,8,9                   | 9,11,13                      | 13   | 14.3 | 16   | Vdc   |

| Quiescent Input Current (See Figure 2) $(R_L = \infty$ , Chroma and Reference Input Voltages = 0) $(R_L = 3.3 \text{ k ohms}$ , Chroma and Reference Input Voltages = 0) | 6                       | 8                            | 16.5 | 6.0  | 25.5 | mA    |

| Reference Input DC Voltage                                                                                                                                               | 4,5                     | 6,7                          |      | 6.2  |      | Vdc   |

| Chroma Input DC Voltage                                                                                                                                                  | 2,3                     | 3,4                          | _    | 3.4  |      | Vdc   |

| Differential Output Voltage<br>See Note 1 and Figure 3                                                                                                                   | 7,8,9                   | 9,11,13                      | _    | 0.3  | 0.6  | Vdc   |

| Output Temperature Coefficient<br>(No Output Differential Voltage<br>> 0.6 Vdc, +25°C to +65°C)<br>See Note 1 and Figure 3                                               | 7,8,9                   | 9,11,13                      | -    | 3.0  | -    | mV/°C |

#### DYNAMIC CHARACTERISTICS (V+ = 24 Vdc, R<sub>L</sub> = 3.3 k ohms,

Referenced Input Voltage = 1.0 Vp·p, TA = +25°C unless otherwise noted)

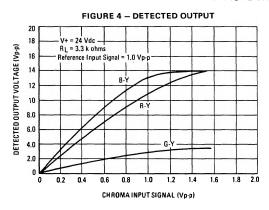

| Detected Output Voltage (B-Y) See Note 2                                                                                | 9          | 13            | 8.0        | 9.0        | -          | V <sub>P</sub> -p |

|-------------------------------------------------------------------------------------------------------------------------|------------|---------------|------------|------------|------------|-------------------|

| Chroma Input Voltage<br>(B-Y Output = 5.0 Vp-p)<br>See Note 3                                                           | 2          | 3             | 7.7        | 0.3        | 0.7        | Vp-p              |

| Detected Output Voltage (Adjust B-Y Output to 5.0 Vp.p) See Note 4 G-Y                                                  | 7          | 9             | 0.75       | 1.0        | 1,25       | Vp-p              |

| R-Y                                                                                                                     | 8          | 11            | 3.5        | 3.8        | 4.2        | d-d               |

| Relative Output Phase (8-Y Output = 5.0 Vp.p)  8-Y to R-Y  4.0 Vp.p 8-Y to G-Y  256°                                    | 9-8<br>9-7 | 13-11<br>13-9 | 101<br>248 | 106<br>256 | 111<br>264 | Degrees           |

| 1.0 VPP                                                                                                                 |            |               |            |            |            |                   |

| Demodulator Unbalance Voltage<br>(no Chroma Input Voltage and<br>normal Reference Signal<br>Input Voltage)              | 7,8,9      | 9,11,13       | 1.0        | 250        | 500        | mVp-p             |

| B-Y Phase Shift<br>(B-Y Reference Input to B-Y Output)                                                                  | 5-9        | 7-13          | -          | 3          | -          | Degrees           |

| Residual Carrier and Harmonics<br>(with Input Signal Voltage,<br>normal Reference Signal Voltage<br>and B-Y = 5,0 Vp-p) | 7,8,9      | 9,11,13       | 1 · =      | T D        | 1.5        | V <sub>P</sub> ·p |

| Reference Input Resistance<br>(Chroma Input = 0)                                                                        | 4,5        | 6,7           | -          | 2.0        | -          | k ohms            |

| Reference Input Capacitance<br>(Chroma Input = 0)                                                                       | 4,5        | 6,7           | 74         | 6.0        | 15,2       | pF                |

| Chrome Input Resistance                                                                                                 | 2,3        | 3,4           |            | 2.0        | <u> </u>   | k ohms            |

| Chroma Input Capacitance                                                                                                | 2,3        | 3,4           | -          | 2.0        | -          | pF                |

#### NOTES:

- NOTES:

1. With Chroma Input Signal Voltage = 0 and normal Reference Input Signal Voltage (1.0 Vp-p.), all output voltages will be within specified limits and will not differ from each other by greater than 0.6 Vdc.

2. With normal Reference Input Signal Voltage, adjust Chroma Input Signal Voltage to 0.6 Vp-p.

3. With normal Reference Input Signal Voltage, adjust Chroma Input Signal Voltage until the B-Y Output Voltage = 5 Vp-p. The Chroma Input Voltage at this point should be equal to or less than 0.7 Vp-p.

4. With normal Reference Input Signal Voltage, adjust the Chroma Input Signal until the B-Y Output Voltage = 5 Vp-p. At this point, the R-Y and G-Y voltages will fall within the specified limits.

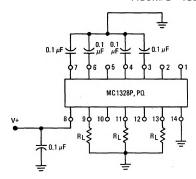

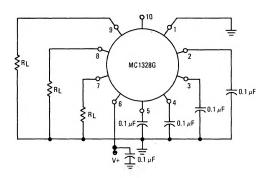

# $\label{eq:tensor} \begin{array}{l} \textbf{TEST CIRCUITS} \\ \text{(V$^+$ = 24 Vdc, R$_L$ = 3.3 k$_\Omega$, T$_A$ = +25°C unless otherwise noted)} \end{array}$

FIGURE 2 - TEST CIRCUIT WITH NO REFERENCE INPUT SIGNAL

FIGURE 3 – TEST CIRCUIT WITH REFERENCE INPUT SIGNAL (Quiescent Current, DC Output Voltage, Difference Voltage)

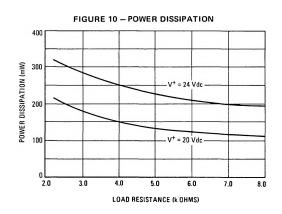

#### TYPICAL CHARACTERISTICS

#### TYPICAL CHARACTERISTICS (continued)

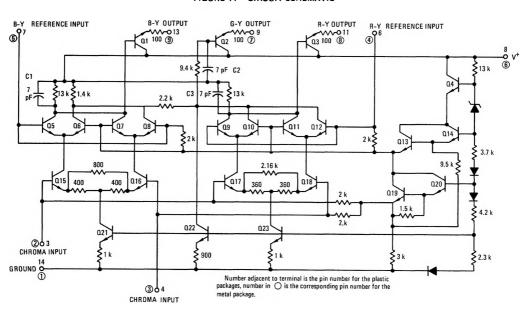

FIGURE 11 - CIRCUIT SCHEMATIC

#### CIRCUIT OPERATION

A double sideband suppressed carrier chroma signal flows between the bases of the two differential pairs, 215 and Q16, Q17 and Q18. A reference signal of approximately 1 Vp-p amplitude having the same frequency as the suppressed chroma carrier with an appropriate phase relationship is supplied between the bases of the upper differential pairs Q5 and Q6, Q7 and Q8, Q9 and Q10, Q11 and Q12. The upper pairs are switched between full conduction and zero conduction at the carrier frequency rate. The collectors of the upper pairs are cross-coupled so that "doubly balanced" or "full-wave" synchronous detected chroma signals are obtained. Both positive and negative phases of the detected signal are available at opposite collector pairs.

Capacitors C1, C2 and C3 provide filtering of carrier harmonics from the detected cotor difference signals. This increases the available swing before clipping for the color difference signal, and reduces the high frequency components which must pass through the emitter followers (Q1, Q2, Q3) into the video output stages. Since high capacitance (>100 pF) is characteristic of the input impedance of a video output stage, the transistor emitter followers must operate at a high quiescent current (>5 mA) in order to pass large high frequency components without distortion. The filtering reduces the quiescent current required in the emitter followers and thus reduces dissipation in the integrated circuit.