# CMOS 16 X 8 CROSSPOINT WITH CONTROL MEMORY

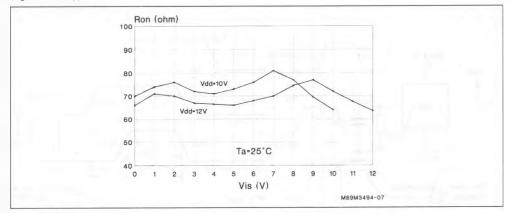

- LOW ON RESISTANCE (typ. 60 Ω at V<sub>DD</sub> = 10 V)

- INTERNAL CONTROL LATCHES

- ANALOG SIGNAL SWING CAPABILITY EQUAL TO POWER SUPPLY VOLTAGE APPLIED

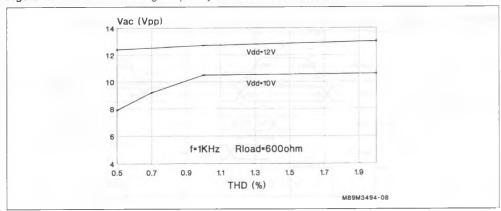

- LESS THAN 1 % TOTAL DISTORT. AT 0 dBm

- LESS THAN 95 dB CROSS-TALK AT 1 KHz 1 V<sub>∞</sub>

- VERY LOW POWER CONSUMPTION

#### DESCRIPTION

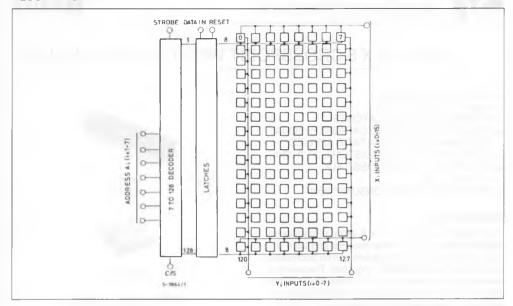

The M3494 contains a 16 x 8 array of crosspoint together with a 7 to 128 line decoder and latch circuits. Anyone of the 128 switches can be addressed by selecting the appropriate 7 input bits. The selected switch can be turned on or off by applying a logical one or zero to the data in and the strobe input at logical one. A reset signal can be used to turn off all the switches together when is set at logical one.

The input pin  $V_G$  shifts the logic level of the digital inputs. It allows one M3494 supplied between  $V_{BB}$  and  $V_{DD}$  to have input logic levels equal to  $V_G$  and  $V_{DD}$ .

M3494 can handle analog signals with an amplitude equal to the voltage power supply.

The C/S allows the control inputs of different devices to be connected in parallel in multiple chip system. Each device is selected when its own C/S input pin is high level.

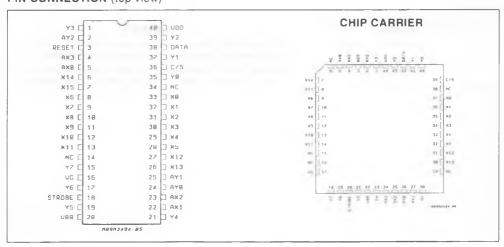

M3494 is available in 40 lead dual in-line plastic, or 44 lead plastic chip carrier packages.

#### PIN CONNECTION (top view)

#### **BLOCK DIAGRAM**

## INPUT/OUTPUT DESCRIPTION

## **POWER**

| I/O | Symbol          | Pin | Description           |  |

|-----|-----------------|-----|-----------------------|--|

|     | V <sub>DD</sub> | 40  | Positive Power Supply |  |

| 1   | V <sub>BB</sub> | 20  | Negative Power Supply |  |

| 1   | V <sub>G</sub>  | 16  | Digital Signal Ground |  |

## **ADDRESS**

| I/O | Symbol  | Pin          | Description                                                                                                                    |

|-----|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| I   | AX0-AX3 | 4, 5, 22, 23 | X Address Lines. These 4 pins are used to select one of the 16 rows of switches. Refer to the truth table for legal address.   |

| ı   | AY0-AY2 | 2, 24, 25    | Y Address Lines. These 3 pins are used to select one of the 8 columns of switches. Refer to the truth table for legal address. |

## CONTROL

| 1/0 | Symbol | Pin | Description                                                                                                                                                                                                                                                                                            |

|-----|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DATA   | 38  | This input determines if the selected switch will be turned on (closed) or off (opened). If the pin is held high, the selected switch will be closed.  If the pin is held low, the switch will be opened.                                                                                              |

| ı   | STROBE | 18  | This pin enables whatever action is selected by the ADDRESS and DATA pins.  When the STROBE pin is held low, no switch openings or closings take place. When the STROBE pin is held high, the switch addressed by the select lines will be opened or closed (depending upon the state of the DATA pin) |

| I   | RESET  | 3   | Master Reset. This pin turns off (opens) all 128 switches. The states of the above control lines are irrelevant. This pin is active high.                                                                                                                                                              |

| 1   | C/S    | 36  | Chip Select. This pin allow the input control lines of different M3494's to be connected in parallel in multiple chip system. This pin is active high. Each device is selected by its own C/S input pin.                                                                                               |

## DATA

| I/O | Symbol | Pin                        | Description                                                                                     |

|-----|--------|----------------------------|-------------------------------------------------------------------------------------------------|

| 1/0 | X0-X15 | 6-13, 26-33                | Analog Input/outputs. These pins are connected to the Y0-Y7 pins according to the truth table.  |

| I/O | Y0-Y7  | 1,15,17,19,21,<br>35,37,39 | Analog Input/outputs. These pins are connected to the X0-X15 pins according to the truth table. |

#### TRUTH TABLE

|              |     |          | Address |     |     |     | Connections               |

|--------------|-----|----------|---------|-----|-----|-----|---------------------------|

| AX0          | AX1 | AX2      | AX3     | AY0 | AY1 | AY2 | Connections               |

| 0            | 0   | 0        | 0       | 0   | 0   | 0   | X0 - Y0                   |

| 1            | 0   | 0        | 0       | 0   | 0   | 0   | X1 - Y0                   |

| 0            | 1   | 0        | 0       | 0   | 0   | 0   | X2 - Y0                   |

| 1            | 1   | 0        | 0       | 0   | 0   | 0   | X3 - Y0                   |

| 0            | 0   | 1        | 0       | 0   | 0   | 0   | X4 - Y0                   |

| 1            | 0   | 1        | 0       | 0   | 0   | 0   | X5 - Y0                   |

| 0            | 1   | 1        | 0       | 0   | 0   | 0   | X12 - Y0                  |

| 1            | 1   | 1        | 0       | 0   | 0   | 0   | X13 - Y0                  |

| 0            | 0   | 0        | 1       | 0   | 0   | 0   | X6 - Y0                   |

| 1            | 0   | 0        | 1       | 0   | 0   | 0   | X7 - Y0                   |

| 0            | 1   | 0        | 1       | 0   | 0   | 0   | X8 - Y0                   |

| 1            | 1   | 0        | 1       | 0   | 0   | 0   | X9 - Y0                   |

| 0            | 0   | 1        | 1       | 0   | 0   | 0   | X10 - Y0                  |

| 1            | 0   | 1        | 1       | 0   | 0   | 0   | X11 - Y0                  |

| n            | 1   |          | 1       | 0   | 0   | 0   | X14 - Y0                  |

| 1            | 1   | 1        | 1       | 0   | 0   | 0   | X15 - Y0                  |

| 0            | 0   | 0        | 0       | 1   | 0   | 0   | X0 - Y1                   |

| Ţ            |     | 1        | 1       | 1   | 1   | 1   | $\downarrow$ $\downarrow$ |

| 1            | 1   | 1        | 1       | 1   | 0   | 0   | X15 - Y1                  |

| 0            | 0   | 0        | 0       | 0   | 1   | 0   | X0 - Y2                   |

| 1            | 1   | 1        | ↓       | 1   | 1   | 1   | 1                         |

| 1            | 1   | 1        | 1       | 0   | 1   | 0   | X15 - Y2                  |

| 0            | 0   | 0        | 0       | 1   | 1   | 0   | X0 - Y3                   |

| 1            | 1   | 1        | 1       | 1   | 1   | 1   | ↓ ↓                       |

| 1            | 1   | 1        | 1       | 1   | 1   | 0   | X15 - Y3                  |

| 0            | 0   | 0        | 0       | 0   | 0   | 1   | X0 - Y4                   |

| 1            | ↓   | ↓        | ↓ ↓     | 1   | 1   | 1 1 | ↓ ↓                       |

| 1            | 1   | 1        | 1       | 0   | 0   | 1   | X15 - Y4                  |

| 0            | 0   | 0        | 0       | 1   | 0   | 1   | X0 - Y5                   |

| $\downarrow$ | 1   | ↓        | ↓ ↓     | 1   | 1   |     | ↓ ↓                       |

| 1            | 1   | 1        | 1       | 1   | 0   | 1   | X15 - Y5                  |

| 0            | 0   | 0        | 0       | 0   | 1   | 1   | X0 - Y6                   |

| 1            | ↓   | <b>1</b> | 1       | 1   | 1   | 1   | ↓ ↓                       |

| 1            | 1   | 1        | 1       | 0   | 1   | 1   | X15 - Y6                  |

| 0            | 0   | 0        | 0       | 1   | 1   | 1   | X0 - Y7                   |

| 1            | 1   | 1        | ↓       | 1   | 1   | 1   | ↓ ↓                       |

| 1            | 1   | 1        | 1       | 1   | 1   | 1   | X15 - Y7                  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                               | Value                                  | Unit |

|------------------|-----------------------------------------|----------------------------------------|------|

| V <sub>DD</sub>  | DC Supply Voltage (V <sub>BB</sub> = 0) | - 0.5 to 14                            | V    |

| V <sub>IN</sub>  | Input Voltage Range                     | $V_{G} - 0.5 \text{ to } V_{DD} + 0.5$ | V    |

| P <sub>tot</sub> | Power Dissipation                       | 1                                      | W    |

| Top              | Operating Temperature Range             | 0 to 70                                | °C   |

| T <sub>sta</sub> | Storage Temperature Range               | - 50 to 125                            | °C   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol                             | Parar                 | neter              | Value                             | Unit |

|------------------------------------|-----------------------|--------------------|-----------------------------------|------|

| V <sub>DD</sub><br>V <sub>BB</sub> | Supply Voltages       | V <sub>G</sub> = 0 | + 5 ± 10 %<br>- 5 ± 10 %          |      |

| Тор                                | Operating Temperature |                    | 0 to 70                           | °C   |

| VIN                                | (logic signal)        |                    | V <sub>G</sub> to V <sub>DD</sub> |      |

## STATIC ELECTRICAL CHARACTERISTICS (Tamb = 0 to 70 °C, VDD = + 5 V, VBB = -5 V, VG = 0 V)

| Symbol | Parameter      | Test Conditions         | Min. | Тур. | Max. | Unit |

|--------|----------------|-------------------------|------|------|------|------|

| Is     | Supply Current | Reset = V <sub>DD</sub> |      |      | 1    | mA   |

## CROSSPOINT

| Symbol | Parameter               | Parameter Test Conditions                                         |  |    | Max. | Unit |

|--------|-------------------------|-------------------------------------------------------------------|--|----|------|------|

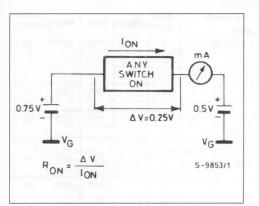

|        | On Resistance           | $V_{IDC} = 0.75 \text{ V}$ $V_{ODC} = 0.5 \text{ V}$ (see fig. 1) |  | 60 | 100  | Ω    |

|        | On Resistance Variation |                                                                   |  | 6  | 10   | Ω    |

|        | Off Leakage*            | All switches off $V_{OS} = V_{IS} = V_{BB}$ to $V_{DD}$           |  |    | ± 3  | μА   |

## CONTROLS

| Symbol   | Parameter      | Test Conditions            | Min. | Тур. | Max. | Unit |

|----------|----------------|----------------------------|------|------|------|------|

| VIL      |                |                            |      |      | 0.8  | V    |

| $V_{IH}$ |                |                            | 2.4  |      |      | V    |

|          | Input Leakage* | $V_{IN} = V_G$ to $V_{DD}$ |      |      | ± 3  | μА   |

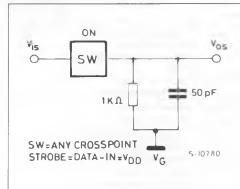

**DYNAMIC ELECTRICAL CHARACTERISTICS**( $T_{amb}=25~^{\circ}C$ ,  $C_{L}=50~pF$  all input square wave rise and fall times = 10 ns,  $V_{DD}=+5~V$ ,  $V_{BB}=-5~V$ ,  $V_{G}=0~V$ )

#### **CROSSPOINTS**

|                    |                                                                                        | Te                    | Test Conditions         |                              |                          |      | Value |      |            |  |

|--------------------|----------------------------------------------------------------------------------------|-----------------------|-------------------------|------------------------------|--------------------------|------|-------|------|------------|--|

| Symbol             | Parameter                                                                              | Note                  | f <sub>i</sub><br>(KHz) | R <sub>L</sub> ( <b>K</b> Ω) | V <sub>is</sub><br>(Vpp) | Min. | Тур.  | Max. | Unit       |  |

| t <sub>PHL</sub> , | Propagation Delay Time (switch ON) Signal Input to Output                              | Fig. 2                |                         | 1                            |                          |      | 30    | 100  | ns         |  |

|                    | Frequency Response (any switch ON) 20 log (V <sub>OS</sub> /V <sub>IS</sub> ) = - 3 dB | C <sub>L</sub> = 3 pF |                         | 0.091                        | 2                        |      |       | 50   | MHz        |  |

|                    | Sine Wave Distortion                                                                   |                       | 1                       | 0.6                          | 8                        |      |       | 1    | %          |  |

| -                  | Feedthrough (any switches OFF)                                                         | Fig. 3                | 10                      | 1                            | 2                        | - 90 |       |      | dB         |  |

|                    | Frequency For Signal Crosstalk<br>Attenuation of 40 dB<br>Attenuation of 110 dB        | Fig. 4                |                         |                              | 1                        | 2    | 1 5   |      | MHz<br>KHz |  |

| С                  | Capacitance<br>Xn to V <sub>BB</sub>                                                   |                       |                         |                              |                          |      |       | 15   |            |  |

|                    | Y <sub>n</sub> to V <sub>BB</sub>                                                      |                       | 1000                    |                              | 0.1                      | 15   |       |      | pF         |  |

|                    | Feedthrough                                                                            |                       |                         |                              |                          |      |       | 0.4  |            |  |

| С                  | Capacitance<br>Logic Input to V <sub>G</sub>                                           |                       | 1000                    |                              | 0.1                      | 5    |       | pF   |            |  |

# DYNAMIC ELECTRICAL CHARACTERISTICS (continued)

## CONTROLS

|                  |                                                                                 | Test Conditions                                                   |                      |             |      | Value |      |      |

|------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|-------------|------|-------|------|------|

| Symbol           | Parameter                                                                       | $V_{DD} = + 5 V$ $V_{BB} = -5 V$                                  | V <sub>G</sub> = 0 V | See<br>Fig. | Min. | Тур.  | Max. | Unit |

| tpsn             | Propagation Delay Time<br>Strobe to Output<br>(switch turn-ON to high<br>level) | $R_{L} = 1 K\Omega N \qquad D_{L}$ $t_{r}, t_{f} = 10 \text{ ns}$ | = 50 pF              | 5           |      | 150   | 200  | ns   |

| tpzH             | Data-in to Output (turn-ON to high level)                                       |                                                                   |                      | 6           |      | 150   | 200  | ns   |

| t <sub>PAN</sub> | Address to Output (turn-ON to high level)                                       |                                                                   |                      | 7           |      | 150   | 200  | ns   |

| tpsf             | Propagation Delay Time<br>Strobe to Output<br>(switch turn-OFF)                 |                                                                   |                      | 5           |      | 150   | 200  | ns   |

| tpZL             | Data-in to Output (turn-ON to low level)                                        |                                                                   |                      | 6           |      | 150   | 200  | ns   |

| tpar             | Address to Output (turn-OFF)                                                    |                                                                   |                      | 7           |      | 150   | 200  | ns   |

| ts               | Set-UP Time<br>Data-in to Strobe or C/S                                         |                                                                   |                      | 5, 10       | 20   |       |      | ns   |

| t <sub>H</sub>   | Hold Time<br>Data-in to Strobe or C/S                                           |                                                                   |                      | 5. 10       | 120  |       |      | ns   |

| to               | Switching Frequency                                                             |                                                                   |                      |             |      | 1     |      | MHz  |

| tw               | Strobe Pulse Width C/S<br>Pulse Width                                           |                                                                   |                      | 10          | 100  |       |      | ns   |

| twa              | Reset Pulse Width                                                               |                                                                   |                      | 9           | 150  |       |      | ns   |

| t <sub>PHZ</sub> | Reset Turn-OFF to Output Delay                                                  |                                                                   |                      | 9           |      | 150   | 200  | ns   |

| tas              | Address Set-UP Time<br>Address to Strobe or C/S                                 |                                                                   |                      | 10          | 20   |       |      | ns   |

| t <sub>AH</sub>  | Address Hold Time<br>Address to Strobe or C/S                                   | 1                                                                 |                      | 10          | 20   |       |      | ns   |

|                  | Control Crosstalk<br>Data-in, Address.<br>or Strobe to Output                   | Square Wave $V_{IN}$<br>Input $t_r$ , $t_f = 10$ ns $R_L$         | = 3 V<br>= 10 kΩ     | 8           |      | 75    |      | mV   |

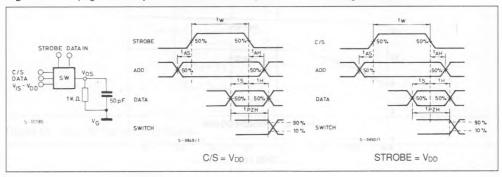

## **TEST CIRCUITS**

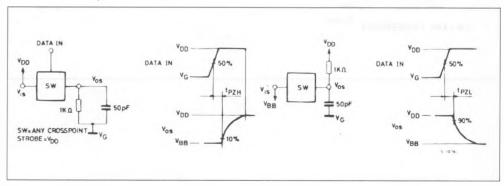

Figure 1: RON Measurement.

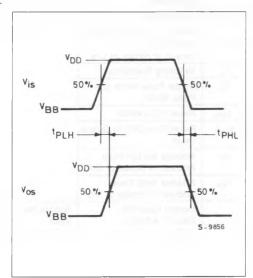

Figure 2: Propagation Delay Time and Waveforms (signal input to signal output switch ON).

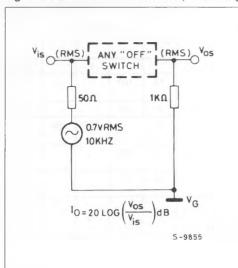

Figure 3: Off Isolation Measurement (Feed through).

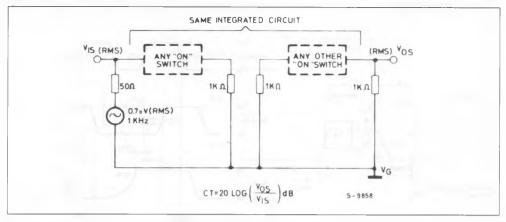

Figure 4: Crosstalk Measurements.

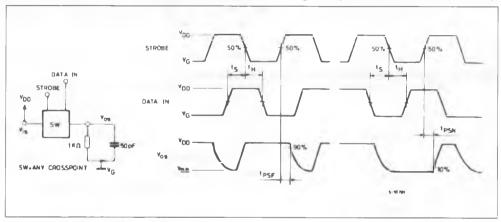

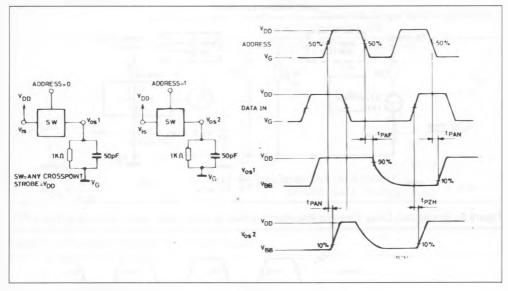

Figure 5: Propagation Delay Time and Waveforms (strobe to signal output switch Turn-ON or Turn-OFF).

Figure 6: Propagation Delay Time and Waveforms (data-in signal output, switch Turn-ON to high or low level).

**Figure 7 :** Propagation Delay Time and Waveforms (address to signal output switch Turn-ON or Turn-OFF).

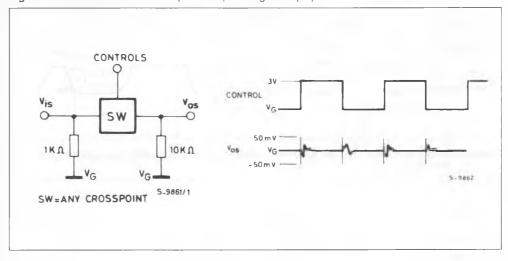

Figure 8: Waveforms for Crosstalk (control input to signal output).

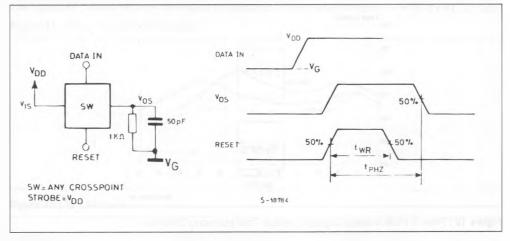

Figure 9: Propagation Delay Time and Waveforms (reset to output delay).

Figure 10: Propagation Delay Time and Waveforms (Strobe and C/S to signal output switch).

Figure 11: Typical Ron versus Vis.

Figure 12: Peak to Peak Voltage Capability versus Total Harmonic Distortion.

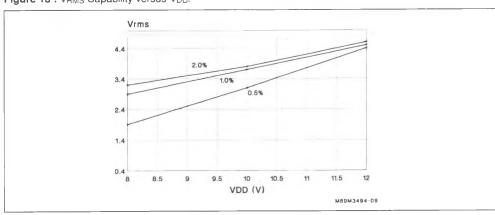

Figure 13: V<sub>RMS</sub> Capability versus V<sub>DD</sub>.

#### TYPICAL APPLICATIONS

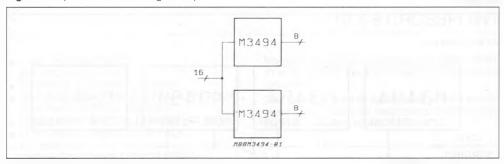

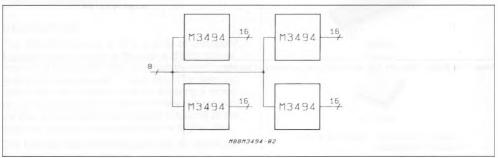

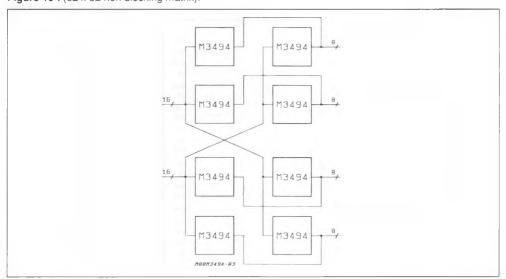

The figures 14, 15 and 16 show the system configuration for expanded matrices (16 x 16, 8 x 64, 32 x 32).

Figure 14: (16 x 16 non blocking matrix).

Figure 15: (8 x 64 matrix).

Figure 16: (32 x 32 non blocking matrix).

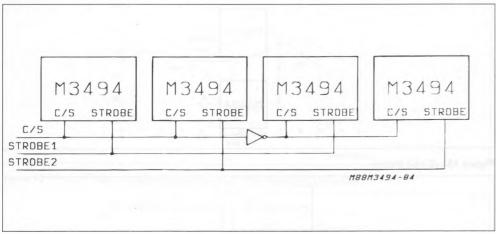

The availability of the C/S input in addition of the STROBE input aids the addressing circuit for expanded matrices.

Fig. 17 shows an example, the selection circuit for a matrix with 4 x M3494 that implement this function with only one extens! inverter.

Figure 17.

Note: The Reset, Data and Address inputs are connected in parallel.