# **MOS** INTEGRATED CIRCUIT

## **16 KEY KEYBOARD ENCODER AND LATCH**

- ANTIBOUNCE AND ANTINOISE CIRCUITRY

- INTERLOCK PREVENTS INCORRECT SELECTION

- OPERATES WITH SINGLE POLE PUSH-BUTTONS

- SELECTION OF PROGRAM 1 AT POWER ON

- MUTING OUTPUT AVAILABLE DURING PROGRAM CHANGES AND POWER SUPPLY SWITCHING

- STEP-BY-STEP PROGRAM CHANGE INPUT

- KEYBOARD LOCKING

- OUTPUTS DIRECTLY COMPATIBLE WITH M 193 (ELECTRONIC PROGRAM MEMORY), M 192 (7-SEGMENT DECODER DRIVER), H 770/1/2/3 (QUAD ANALOG SWITCHES)

The M 190 is a monolithic integrated circuit which automatically scans an up to 16 Key keyboard, generating continuous sequential pulses on X outputs and detecting key closure on Y inputs.

A key closure is retained as valid when the key remains closed for all the time corresponding to one scan pulse (i.e. when the bounce is over).

When it occurs an internal flip-flop is set but the key closure is accepted only if it is detected on a second scan cycle. At this point a 4 bit word corresponding to the key closed is internally latched and a pulse is available on the Muting output.

During the time this pulse lasts, no other key closure will be recognized. The new output code follows the Mute signal with a delay.

All the timing for the circuits is determined by the clock oscillator whose frequency is externally fixed by an RC network.

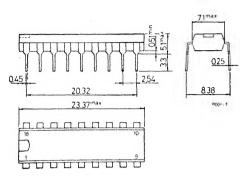

The M 190 also includes a "step-by-step" program change input that, when connected to  $V_{SS}$  (GND), advances by one the selected channel and a Lock which blocks the circuit on the last selected channel. The circuit is produced in N-channel silicon gate technology and is available in a 18 pin dual in-line plastic package.

#### **ABSOLUTE MAXIMUM RATINGS\***

| V <sub>DD</sub> **   | Supply voltage                             | -0.5 to 20 | v  |

|----------------------|--------------------------------------------|------------|----|

| $V_1^{}$             | Input voltage                              | -0.5 to 20 | V  |

| V <sub>O (off)</sub> | Off state output voltage (pins 1-2-3-4-11) | 20         | V  |

| lo                   | Output current                             | 5          | mΑ |

| Ptot                 | Total package power dissipation            | 500        | mW |

| T <sub>stg</sub>     | Storage temperature                        | -65 to 125 | °C |

| Top                  | Operating temperature                      | 0 to 70    | °C |

\* Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

\*\* All voltage are referred to V<sub>SS</sub> pin voltage.

#### ORDERING NUMBER: M 190 B1

MECHANICAL DATA (dimensions in mm)

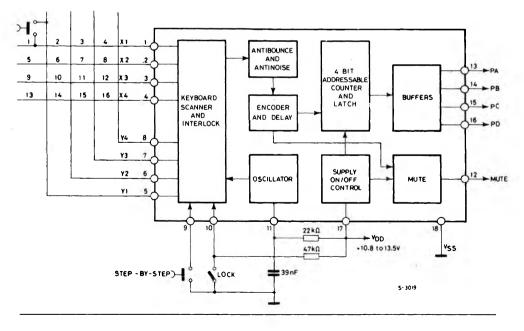

**BLOCK DIAGRAM**

## **RECOMMENDED OPERATING CONDITIONS**

|                      | fumlu voltare                             | 10.0 - 12.5  |    |

|----------------------|-------------------------------------------|--------------|----|

| V <sub>DD</sub>      | Supply voltage                            | 10.8 to 13.5 | v  |

| V <sub>1</sub>       | Input voltage                             | 0 to 13.5    | V  |

| V <sub>O (off)</sub> | Off state output voltage (pins 1-23-4-11) | max 13.5     | V  |

| lo                   | Output current                            | max 2        | mΑ |

| Top                  | Operating temperature                     | 0 to 70      | °C |

| Rt                   | Timing resistor                           | 8 to 47      | KΩ |

| Ct                   | Timing capacitor                          | 1 to 330     | nF |

# STATIC ELECTRICAL CHARACTERISTICS (Over recommended operating conditions)

|                     | <b>.</b> .                |                                                                                             | Values at 25° C |      |      |      |

|---------------------|---------------------------|---------------------------------------------------------------------------------------------|-----------------|------|------|------|

| Parameter           |                           | Test conditions                                                                             | Min.            | Тур. | Max. | Unit |

| V <sub>IH</sub> .   | High level input voltage  | pins 5, 6, 7, 8, 9, 10                                                                      | 3.5             |      |      | V    |

| VIL                 | Low level input voltage   | pins 5, 6, 7, 8, 9, 10                                                                      |                 |      | 0.8  | v    |

| Чн                  | High level input current  | V <sub>DD</sub> = 13.5V, V <sub>IH</sub> = 13.5V<br>pins 5, 6, 7, 8, 9, 10                  |                 |      | 10   | μА   |

| I <sub>IL</sub>     | Low level input current   | V <sub>DD</sub> = 13.5V, V <sub>IL</sub> = 0.8V<br>pins 5, 6, 7, 8, 9, 10                   | 0.1             |      | 0.8  | mA   |

| V <sub>он</sub>     | High level output voltage | V <sub>DD</sub> = 10.8V I <sub>OH</sub> = -1 mA,<br>pin 12                                  | 2.4             |      |      | v    |

|                     |                           | V <sub>DD</sub> = 10.8V I <sub>OH</sub> = -1 mA,<br>pins 13. 14, 15, 16                     | 4               |      |      |      |

| V <sub>ol</sub>     | Low level output voltage  | V <sub>DD</sub> = 10.8V I <sub>OL</sub> = 0.8 mA<br>pins 1, 2, 3, 4, 11                     |                 |      | 0.4  |      |

|                     |                           | V <sub>DD</sub> = 10.8V I <sub>OL</sub> = 2 mA,<br>pins 13, 14, 15, 16                      |                 |      | 0.4  |      |

| I <sub>O(off)</sub> | Output leakage current    | V <sub>DD</sub> <sup>=</sup> V <sub>O(off)</sub> <sup>=</sup> 13.5V,<br>pins 1, 2, 3, 4, 11 |                 |      | 20   | μΑ   |

| IDD                 | Supply current            | V <sub>DD</sub> = 13.5V<br>(all inputs and outputs open)                                    |                 |      | 18   | mA   |

## **TRUTH TABLE**

|     |                                 | Output code (positive logic) |     |    |    |  |

|-----|---------------------------------|------------------------------|-----|----|----|--|

| Key | Connection                      | ΡΑ                           | РВ  | PC | PD |  |

| 1   | X <sub>1</sub> - Y <sub>1</sub> | L                            | L   | L  | L  |  |

| 2   | X <sub>1</sub> - Y <sub>2</sub> | н                            | L   | L  | L  |  |

| 3   | X1 - Y3                         | L                            | н   | L  | L  |  |

| 4   | X <sub>1</sub> - Y <sub>4</sub> | н                            | н   | L  | L  |  |

| 5   | $X_2 - Y_1$                     | L                            | L   | н  | L  |  |

| 6   | X <sub>2</sub> - Y <sub>2</sub> | н                            | ) L | н  | L  |  |

| 7   | X <sub>2</sub> - Y <sub>3</sub> | L                            | н   | н  | L  |  |

| 8   | X <sub>2</sub> - Y <sub>4</sub> | н                            | н   | н  | L  |  |

| 9   | X <sub>3</sub> - Y <sub>1</sub> | L                            | L   | L  | н  |  |

| 10  | X <sub>3</sub> - Y <sub>2</sub> | н                            | L   | L  | н  |  |

| 11  | X <sub>3</sub> - Y <sub>3</sub> | L                            | н   | L  | н  |  |

| 12  | X3 - Y4                         | н                            | н   | L  | н  |  |

| 13  | $\times_4 - \vee_1$             | L                            | L   | н  | н  |  |

| 14  | X <sub>4</sub> - Y <sub>2</sub> | н                            | L   | н  | н  |  |

| 15  | $X_4 - Y_3$                     | L                            | н   | н  | н  |  |

| 16  | X4 - Y4                         | н                            | н   | н  | н  |  |

## DESCRIPTION

## Pins 1, 2, 3, 4-X<sub>1</sub>, X<sub>2</sub>, X<sub>3</sub>, X<sub>4</sub> outputs

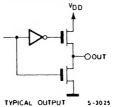

The internal open drain transistors on these outputs are sequentially switched on.

## Pins 5, 6, 7, 8-Y<sub>1</sub>, Y<sub>2</sub>, Y<sub>3</sub>, Y<sub>4</sub> inputs

These inputs correspond to the columns of the keyboard matrix. When a key is pushed, one of the X output signal is present on one of the 4 rows, putting a low level on the Y input.

An interlock circuit rejects more than one key pressed at the same time.

To increase the noise immunity of the system and to avoid bouncing problems, the key closure is considered valid only when it is present for all the time corresponding to the scan pulse. With this system spurious noise signals are also rejected.

Another increase in the noise immunity is given by detecting key closure over two consecutive scanning cycles.

#### **DESCRIPTION** (continued)

After the key bounce time, the acceptance time of a command is between 35T and 63T, where T is the period of the clock pulse.

When any input is open it is pulled-up to logic H by an integrated MOS load of about 50 K $_{\Omega}$  and protected by a diode.

#### Pin 9 - Step-by-step program change

This input advances by one the previously selected channel every time ti is connedted to ground. This input can be considered as a 17th key and follows all the rules of command acceptance time and partially of interlock.

The unput is pulled-up to logic H by an integrated resistor of about 50 K $\alpha$ ; if the input is not used, it should be connected to V<sub>DD</sub>.

#### Pin 10 - Lock

If this input is connected to  $V_{SS}$  (GND) the circuit is locked on the selected channel. If the input is not used, it must be connected to  $V_{DD}$ .

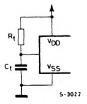

#### Pin 11 - RC network (clock oscillator input)

An internal clock provides all the timing for the circuits.

The frequency of the clock oscillator is controlled by two external components, resistor  $R_t$  and capacitor  $C_t$ .

The period of the clock pulse is approximately given by  $T = R_t C_t$ .

The oscillator works in the following way: assuming the capacitor  $C_t$  is discharged, the resistor  $R_t$  charges the capacitor till an internal threshold is reached. At this point the capacitor is discharged by an internal transistor.

Afterwards the internal transistor is switched off and the cycle can restart.

With  $R_t = 22 \ K_{\Omega}$  and  $C_t = 39 \ nF$  a clock frequency of about 800 Hz is obtained, corresponding to a scan cycle of the keyboard of about 40 ms.

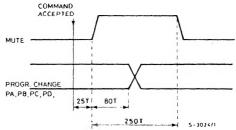

In these conditions the mute signal will be present for about 100 ms before the program changing and will last 300 ms.

### Pin 12 - Mute

The mute signal is available as a high level output (source follower transistor). It is present during power ON/OFF and program changes.

When a command is given the Mute signal and the program information are available in the following way:

The Mute signal is not available when the same program is selected again.

## Pins 13, 14, 15, 16 - PA, PB, PC, PD outputs

These static outputs select the program according to the truth table.

They interface directly with the inputs of M 193 (Electronic Program Memory), M 192 (7 segment Decoder/Driver), H 770/1/2/3 (Quad Analog Switches).

The program 1 is internally selected at power ON.