## **MOS** INTEGRATED CIRCUIT

#### PRELIMINARY DATA

#### 1024 BIT - NON VOLATILE RANDOM ACCESS MEMORY (NV-RAM)

- 256 x 4 ORGANIZATION

- OPTIMUM DATA RETENTION: ONE ORDER OF MAGNITUDE GREATER THAN MNOS DEVICES

- MORE THAN 10<sup>4</sup> MODIFY OPERATIONS PER BIT

- THREE VERSIONS WITH DIFFERENT READ AND MODIFY ACCESS TIMES: M120-2:450 ns → M120 : 700 ns → M120-4 : 950 ns

- INTERNAL WORD MODIFY TIME LESS THAN 100 msec

- "MODIFY END" OUTPUT LINE

- TTL COMPATIBLE: EASY CONNECTION TO ANY MICROPROCESSOR

- COMMON DATA INPUTS AND OUPUTS

- ON CHIP LATCHES FOR ADDRESSES AND DATA

- POWER SUPPLIES  $V_{DD} = 12V \pm 10\%$

- $V_{PP} = 25V \pm 5\%$

- STANDARD 18-PIN DUAL-IN-LINE PACKAGE

The M120 is a new Non Volatile Random Access Memory (NV-RAM). Contents of every word (256 x 4 available on-chip) can be erased and written electrically and data is retained without power supply for 100 years (calculated from test results). SGS-ATES proprietary n-channel, Si-gate, double Polysilicon MOS Technology insures maximum reliability and data retention and allows any number of read operations and more than 10.000 modify cycles per bit. Thanks to an internal circuitry taking care of the modify sequence, access times for both read and modify operations are short enough to allow use with most microprocessors without insertion of wait states. The M120 is available in three different versions. The slowest M120-4 in particular, with 950 ns access time, is intended for applications where the M120 is used in combination with a single chip microcomputer. In these applications all the signals are supplied by the microcomputer I/O ports, and the access time required is always in the range of microseconds. The M120 is available in a standard 18-pin dual-in-line plastic or ceramic package (frit-seal).

#### ABSOLUTE MAXIMUM RATINGS\*

|                  | Input or output voltages (except $V_{DD}$ and $V_{PP}$ ) | -0.5 to 15 | V  |

|------------------|----------------------------------------------------------|------------|----|

| $V_{DD}$         | Supply voltage                                           | -0.5 to 20 | V  |

|                  | Supply voltage                                           | -0.5 to 28 | V  |

| P <sub>tot</sub> | Total power dissipation                                  | 1          | w  |

| T <sub>stg</sub> | Storage temperature range                                | -65 to 150 | °C |

| Top              | Operating temperature range                              | 0 to 70    | °C |

| -                |                                                          | 1          |    |

\* Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stresses rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| ORDERING NUMBERS: | M120B1   | for dual in-line ceramic package (frit seal)<br>for dual in-line plastic package |

|-------------------|----------|----------------------------------------------------------------------------------|

|                   |          | for dual in-line ceramic package (frit seal)                                     |

|                   | M120-2B1 | for dual in-line plastic package                                                 |

|                   | M120-4F1 | for dual in-line ceramic package (frit seal)                                     |

|                   | M120-4B1 | for dual in-line plastic package                                                 |

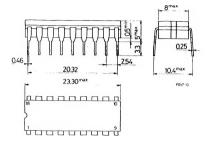

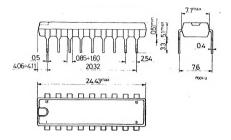

#### MECHANICAL DATA (dimensions in mm)

Dual in-line ceramic package, frit-seal

Dual in-line plastic package

#### **PIN CONNECTIONS**

### LOGIC DIAGRAM

#### **PIN NAMES**

| D0-D3           | DATA INPUTS/OUTPUTS (OPEN DRAIN) |

|-----------------|----------------------------------|

| A0-A7           | ADDRESS INPUTS                   |

| AS              | ADDRESS STROBE INPUT             |

| R/W             | READ/WRITE INPUT                 |

| ME              | MODIFY END OUTPUT (OPEN DRAIN)   |

| V <sub>PP</sub> | POWER (+25V)                     |

| V <sub>DD</sub> | POWER (+12V)                     |

| GND             | GROUND                           |

# DC AND OPERATING CHARACTERISTICS ( $T_{amb}$ = 0°C to 70°C, $V_{DD}$ = +12V ± 10%, $V_{PP}$ = +25V ± 5%)

M 120

| Parameter        |                                        | Test conditions          | 1    |          |      |      |

|------------------|----------------------------------------|--------------------------|------|----------|------|------|

|                  |                                        | lest conditions          | Min. | Typ.*    | Max. | Unit |

| IDD1             | V <sub>DD</sub> supply current         |                          |      |          | 30   | mA   |

| I <sub>PP1</sub> | V <sub>PP</sub> supply current         |                          |      |          | 20   | mA   |

| I <sub>DD2</sub> | Standby V <sub>DD</sub> supply current | AS@ VIH                  |      | <u> </u> | 20   | mĂ   |

| I <sub>PP2</sub> | Standby V <sub>PP</sub> supply current | AS@ VIH                  | -    | - ± -    | 10   | mA   |

| V <sub>IH</sub>  | Input high voltage                     |                          | 2.4  | 5        |      | V    |

| V <sub>IL</sub>  | Input low voltage                      |                          | -0.3 | 0        | 0.6  | V    |

| VOL              | Output low voltage                     | I <sub>OL</sub> = 1.6 mA |      |          | 0.4  | V    |

| ILI              | Input leakage current                  |                          |      |          | 10   | μA   |

| ILO              | Output leakage current                 |                          |      |          | 10   | μA   |

\* Typical values are at +25°C and nominal voltages.

#### AC CHARACTERISTICS

|                  | Deservator                                                                      |      | M 120-2 |      | M 120 |      | M 120-4 |      |

|------------------|---------------------------------------------------------------------------------|------|---------|------|-------|------|---------|------|

| Parameter        |                                                                                 | Min. | Max.    | Min. | Max.  | Min. | Max.    | Unit |

| ts               | Set-up time                                                                     | 50   |         | 50   |       | 100  |         | ns   |

| t <sub>h</sub>   | Hold time                                                                       | 150  |         | 150  |       | 250  |         | ns   |

| tASL             | AS active time                                                                  | 450  | 100K    | 700  | 100K  | 950  | 100K    | ns   |

| tASH             | AS inactive time                                                                | 350  |         | 500  |       | 500  |         | ns   |

| t <sub>R</sub>   | AS ↓ to R/W ↑ (Read)                                                            |      | 100     |      | 150   |      | 200     | ns   |

| tACC             | Access time from AS ↓                                                           |      | 450     |      | 700   |      | 950     | ns   |

| tDOFF            | Data output turn-off delay                                                      |      | 150     |      | 250   |      | 300     | ns   |

| tM               | Modify time (1) from R/W 1                                                      |      | 100     |      | 100   |      | 100     | ms   |

| tWHE             | $\overline{AS} \downarrow$ to $\overline{R/W} \downarrow$ (Early write) (2) (3) | 1    | 100     |      | 150   |      | 200     | ns   |

| twe              | AS↓ to R/W↑ (Early Write)                                                       | 450  |         | 700  |       | 950  |         | ns   |

| <sup>t</sup> MHE | ME turn-on delay from $R/W \downarrow$ (Early Write)                            |      | 400     |      | 500   |      | 600     | ns   |

| tAS              | $R/W \downarrow$ to $\overline{AS} \uparrow$ rising edge (Read/Write)           | 250  | -       | 400  |       | 500  | ļ       | ns   |

| twн              | AS ↓ to R/W ↓ (Read/Write)                                                      | 100  |         | 200  |       | 250  |         | ns   |

| tw∟              | R/W Low time (Read/Write)                                                       | 350  | 100K    | 500  | 100K  | 650  | 100K    | ns   |

| tDF              | Data Float from AS ↓ (Read/Write)                                               | 150  |         | 250  |       | 300  |         | ns   |

| <sup>t</sup> мн  | ME turn-on delay from R/₩↓ (Read/Write)                                         |      | 250     |      | 350   |      | 450     | ns   |

#### Notes:

1) t<sub>M max</sub> is 2 ms for the first 10 modify operations and increases to a maximum of 100 ms after 10<sup>4</sup> operations. 2) If t<sub>WHE</sub>  $\leq$  t<sub>WHE</sub> max then D<sub>OUT</sub> remains floating and there is no conflict between D<sub>OUT</sub> and D<sub>IN</sub>. 3) t<sub>WHE</sub> can be < 0.

TIMING WAVEFORMS

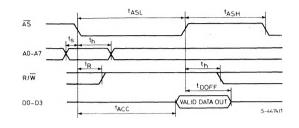

Read Cycle

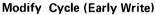

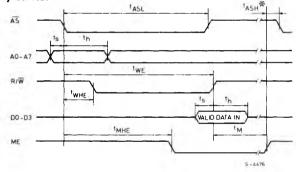

Modify Cycle (Read/Write)

\* The first falling edge of AS following the end of a modify cycle must occur at least t<sub>ASH</sub> after the positive edge of ME.

#### DESCRIPTION OF OPERATION

M120 operation is controlled by the Address Strobe (AS) control input (active low), which also performs the device selecting function.

M 120

The device is deselected (Stand-by Mode) by a high level on AS input.

The falling edge of  $\overline{AS}$  latches Address lines (A0  $\div$  A7) contents into the chip and starts both read and modify cycles.

If  $R/\overline{W}$  remains high while  $\overline{AS}$  is active a **Read Cycle** occurs. The contents of addressed memory location will be available on the Data lines (D0 ÷ D3) after an access time (t<sub>ACC</sub>) from the leading edge of  $\overline{AS}$ . The trailing edge of  $\overline{AS}$  three-states Data lines after t<sub>DOFF</sub> delay.

If R/W is or becomes low while AS is active a Modify Cycle starts.

Depending on timing relationships between  $\overline{AS}$  and  $\overline{R/W}$  leading edges, there are two possible modify sequences.

If R/W falling edge occurs either before or a maximum of  $t_{WHE}$  after  $\overline{AS}$  falling edge, an Early Write Modify Cycle proceeds.

All timing relationships are related to  $\overline{AS}$  falling edge and Data lines are not driven by the M120 thus avoiding any possible bus contention in this mode.

If  $R/\overline{W}$  falling edge occurs a minimum of  $t_{WH}$  after  $\overline{AS}$  falling edge a **Read/Write** Modify Cycle procedes. Most timing relationships are in this case related to  $R/\overline{W}$  falling edge. Because until  $R/\overline{W}$  becomes active, the M120 assumes a read cycle is in process, the device will output addressed location contents on Data lines according to  $t_{DF}$ ,  $t_{ACC}$  and  $t_{WH}$  timing specifications.

This allows a read/write operation to be performed but might also generate some contention on data lines.

However if set-up time requirements are satisfied, the M120 will operate properly since it floats data lines before latching data input.

#### INTERNAL MODIFY OPERATION AND "ME" OUTPUT

At rising edge of R/W in a modify cycle the contents of data lines are latched and the internal modify cycle starts.

The ME output, which indicates Modify Cycle End, goes false (low) after a delay of either  $t_{MHE}$  from  $\overline{AS}$  leading edge (Early Write Modify Cycle) or  $t_{MH}$  from  $\overline{R/W}$  falling edge (Read/Write Modify Cycle). As long as ME is false the device is internally disconnected from buses and control lines, data outputs are floating and no further external operation will be acknowledged by M120.

During internal modify cycle an on-chip circuitry performs a bit by bit comparison between "old" and "new" data word and according to this result writes, erases or leaves unchanged each single bit of the addressed location.

At modify completion (t<sub>M</sub>) ME line becomes true again and M120 is again available for external access.

#### POWER-UP

In order to avoid a spurious modify cycle, care should be taken during the power up sequence to ensure that  $\overline{AS}$  and  $\overline{R/W}$  are at the non-active (high) level before  $V_{DD}$  and  $V_{PP}$  reach half their operating value. The opposite sequence should be followed during the power-down.

Power-on and power-down sequences can start arbitrarily with either  $V_{DD}$  or  $V_{PP}$ .