## 128 X 128 DIGITAL SWITCHING MATRIX

128 INPUT AND 128 OUTPUT CHANNEL DIGI-TAL SWITCHING MATRIX (non blocking)

SGS-THOMSON

- TYPICAL APPLICATION IN PABX

- PCM INPUTS AND OUTPUTS MATUALLY COMPATIBLE

- ACTUAL INPUT-OUTPUT CHANNEL CON-NECTIONS STORED AND MODIFIED VIA AN ON-CHIP 8-BIT PARALLEL MICROPROCES-SOR INTERFACE

- 5 MAIN "FUNCTIONS" or "INSTRUCTIONS" AVAILABLE

- TYPICAL BIT RATE : 2Mbit/s

- TYPICAL SYNCHRONIZATION RATE : 8 KHz (time frame is 125 µs)

- 5 VOLT POWER SUPPLY WITH INTERNALLY GENERATED BIAS VOLTAGE

- MOS & TTL INPUT/OUTPUT LEVELS COMPA-TIBLE

- DIFFUSED WITH ST N-CHANNEL SILICON GATE HIGH DENSITY MOS PROCESS

#### Main instruction controlled by the microprocessor interface

CHANNEL CONNECTION/DISCONNECTION

- CHANNEL DISCONNECTION

- INSERTION OF A BYTE ON A PCM OUTPUT CHANNEL

- TRANSFER TO THE MICROPROCESSOR OF A SINGLE PCM OUTPUT CHANNEL SAMPLE

- TRANSFER TO THE MICROPROCESSOR OF A SINGLE OUTPUT CONTROL WORD

#### ABSOLUTE MAXIMUM RATINGS

| Symbol | Parameter                       | Value       | Unit |

|--------|---------------------------------|-------------|------|

| Vcc    | Supply Voltage                  | - 0.3 to 7  | V    |

| V      | Input Voltage                   | - 0.3 to 7  | V    |

| Vo     | Off State Output Voltage        | 7           | V    |

| Ptot   | Total Package Power Dissipation | 1.5         | W    |

| Tstg   | Storage Temperature Range       | - 65 to 150 | °C   |

| Top    | Operating Temperature Range     | 0 to 70     | °C   |

#### PIN CONNECTION

| RESET     | 1      | 28]    | ۷ <sub>SS</sub> |  |

|-----------|--------|--------|-----------------|--|

| CS 2      | 2      | 27]    | C/D             |  |

| CS 1      | 3      | 26]    | DR              |  |

| WR        | 4      | 25]    | 00              |  |

| RD        | 5      | 24]    | D 1             |  |

| PCMOUT 3  | 6      | 23     | D 2             |  |

| PCM OUT 2 | TT NOU | 22]    | D 3             |  |

| PCM OUT 1 | 8 M044 | 21]    | D4              |  |

| PCM OUT 0 | [ 9    | 20     | D 5             |  |

| BIAS      | 10     | 19]    | D 6             |  |

| CLOCK     | 11     | 18]    | 07              |  |

| SYNC      | 12     | 17     | Vcc             |  |

| PCM IN 3  | 13     | 16 ] P | CM IN 0         |  |

| PCMIN 2   | 14     | 15] P  | CMIN 1          |  |

|           | L      | 5-7885 |                 |  |

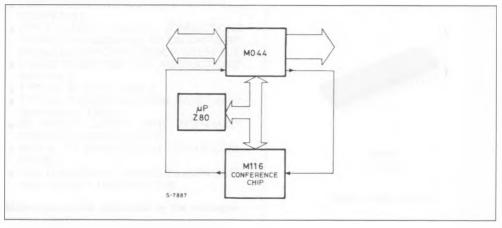

#### **BLOCK DIAGRAM**

#### RECOMMENDED OPERATING CONDITIONS

| Symbol      | Parameter                       | Value        | Unit |

|-------------|---------------------------------|--------------|------|

| Vcc         | Supply Voltage                  | 4.75 to 5.25 | V    |

| V.          | Input Voltage                   | 0 to 5.25    | V    |

| Vo          | Off State Input Voltage         | 0 to 5.25    | V    |

| CLOCK Freq. | Input Clock Frequency           | 4.096        | MHz  |

| SYNC Freq.  | Input Synchronization Frequency | 8            | KHz  |

| Top         | Operating Temperature           | 0 to 70      | °C   |

#### CAPACITANCES (measurements freq. = 1 MHz ; Top = 0 to 70 °C ; unused pins tied to VSS)

| Symbol           | Parameter          | Pins                              | Min. | Typ. | Max. | Unit |

|------------------|--------------------|-----------------------------------|------|------|------|------|

| Cı               | Input Capacitance  | 6 to 15 ; 26 to 30 ; 32 to 36     |      |      | 5    | pf   |

| C <sub>I/O</sub> | I/O Capacitance    | 20 to 24                          |      |      | 15   | pf   |

| Co               | Output Capacitance | 1 to 4 ; 17 to 19 ; 25 ; 37 to 40 |      |      | 10   | pf   |

# DC ELECTRICAL CHARACTERISTICS (T\_{amb} = 0 to 70 °C, V<sub>CC</sub> = 5 V ± 5 %) All DC characteristics are valid 250 $\mu s$ after V<sub>CC</sub> and clock have been applied.

| Symbol          | Parameter                | Pins                                        | Test Conditions                                                                                                                                                                                        | Min.  | Тур. | Max.            | Unit |

|-----------------|--------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------|------|

| VILC            | Clock Input Low Level    | 6                                           |                                                                                                                                                                                                        | - 0.3 |      | 0.8             | V    |

| VIHC            | Clock Input High Level   | 6                                           |                                                                                                                                                                                                        | 3.0   |      | Vcc             | V    |

| VIL             | Input Low Level          | 7 to 15<br>20 to 24<br>26 to 30<br>32 to 36 |                                                                                                                                                                                                        | - 0.3 |      | 0.8             | V    |

| V <sub>IH</sub> | Input High Level         | 7 to 15<br>20 to 24<br>26 to 30<br>32 to 36 |                                                                                                                                                                                                        | 2.0   |      | V <sub>cc</sub> | V    |

| VOL             | Output Low Level         | 17 to 25                                    | I <sub>OL</sub> = 1.8 mA                                                                                                                                                                               |       |      | 0.4             | V    |

| VOH             | Output High Level        | 17 to 25                                    | I <sub>OH</sub> = 250 µ <b>A</b>                                                                                                                                                                       | 2.4   |      |                 | V    |

| V <sub>OL</sub> | PCM Output Low Level     | 1 to 4<br>37 to 40                          | I <sub>OL</sub> = 2.0 mA                                                                                                                                                                               |       |      | 0.4             | V    |

| l <sub>IL</sub> | Input Leakage Current    | 6 to 15<br>26 to 30<br>32 to 36             | $V_{IN} = 0$ to $V_{CC}$                                                                                                                                                                               |       |      | 10              | μA   |

| I <sub>OL</sub> | Data Bus Leakage Current | 17 to 24                                    | $\label{eq:VIN} \begin{array}{l} V_{IN} = 0 \text{ to } V_{CC} \\ V_{CC} \text{ applied }; \text{Pins 35} \\ \text{and 36 tied to } V_{CC}. \text{ After} \\ \text{device Initialization} \end{array}$ |       |      | ± 10            | μA   |

| Icc             | Supply Current           | 16                                          | Clock Freq. = 4.096 MHz                                                                                                                                                                                |       | 170  |                 | mA   |

AC ELECTRICAL CHARACTERISTICS (T<sub>amb</sub> = 0 to 70 °C, V<sub>CC</sub> = 5 V  $\pm$  5 %) All AC characteristics are valid 250 µs after V<sub>CC</sub> and clock have been applied. C<sub>L</sub> is the max capacitive load and RL the test pull up resistor.

| Signal                  | Symbol                                                 | Parameter                                                                                         | Test Conditions                                                                                                       | Min.                               | Typ. | Max.       | Unit                       |

|-------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|------|------------|----------------------------|

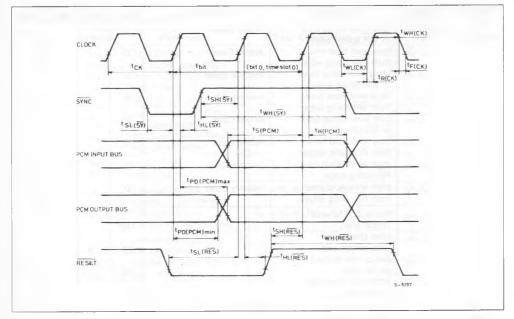

| CK<br>(clock)           | tck<br>twL<br>twH<br>tR<br>tF                          | Clock Period<br>Clock Low Level Width<br>Clock High Level Width<br>Rise Time<br>Fall Time         |                                                                                                                       | 230<br>100<br>100                  |      | 25<br>25   | ns<br>ns<br>ns<br>ns<br>ns |

| SYNC                    | tsi<br>t <sub>HL</sub><br>tsн<br>twн                   | Low Level Setup Time<br>Low Level Hold Time<br>High Level Setup Time<br>High Level Width          |                                                                                                                       | 80<br>40<br>80<br>t <sub>ск</sub>  |      |            | ns<br>ns<br>ns<br>ns       |

| PCM Input<br>Busses     | ts<br>t <sub>H</sub>                                   | Setup Time<br>Hold Time                                                                           |                                                                                                                       | - 5<br>45                          |      |            | ns<br>ns                   |

| PCM<br>Output<br>Busses | tpo min<br>tpo max                                     | Propagation time<br>referred to CK low level<br>Propagation time<br>referred to CK high level     | $C_{L} = 50 \text{ pf},  \text{R}_{L} = 2  \text{K}\Omega$ $C_{L} = 50 \text{ pf},  \text{R}_{L} = 2  \text{K}\Omega$ | 45<br>45                           |      | 180<br>200 | ns<br>ns                   |

| RESET                   | tsı<br>t <sub>HL</sub><br>tsн<br>twн                   | Low Level Setup Time<br>Low Level Hold Time<br>High Level Setup Time<br>High Level Width          |                                                                                                                       | 100<br>50<br>90<br>t <sub>СК</sub> |      |            | ns<br>ns<br>ns<br>ns       |

| WR                      | t <sub>WL</sub><br>t <sub>WH</sub><br>t <sub>REP</sub> | Low Level Width<br>High Level Width<br>Repetition Interval<br>Between Active Pulses               | $t_{REP} = 40 + 2 t_{CK} + t_{WL(CK)} + t_{R(CK)}$                                                                    | 150<br>tcк<br>see<br>formula       |      |            | ns<br>ns<br>ns             |

|                         | t <sub>SH</sub><br>t <sub>HH</sub>                     | High Level Setup Time<br>to Active Read Strobe<br>High Level Hold Time<br>from Active Read Strobe |                                                                                                                       | 0<br>20                            |      |            | ns                         |

|                         | te<br>t <sub>E</sub>                                   | Rise Time<br>Fall Time                                                                            |                                                                                                                       |                                    |      | 60<br>60   | ns<br>ns                   |

| RD                      | t <sub>WL</sub><br>t <sub>WH</sub><br>t <sub>REP</sub> | Low Level Width<br>High Level Width<br>Repetition Interval<br>Between Active Pulses               | $t_{\text{REP}} = 40 + 2 t_{\text{CK}} + t_{\text{WL}(\text{CK})} + t_{\text{R(CK)}}$                                 | 180<br>tск<br>see<br>formula       |      |            | ns<br>ns<br>ns             |

|                         | tsн                                                    | High Level Setup Time<br>to Active Read Strobe                                                    | T H(CK)                                                                                                               | 0                                  |      |            | ns                         |

|                         | tнн                                                    | High Level Hold Time<br>from Active Read Strobe                                                   |                                                                                                                       | 20                                 |      |            | ns                         |

|                         | t <sub>R</sub><br>t <sub>F</sub>                       | Rise Time<br>Fall Time                                                                            |                                                                                                                       |                                    |      | 60<br>60   | ns                         |

### AC ELECTRICAL CHARACTERISTICS (continued)

| Signal                 | Symbol                  | Parameter                                                        | Test Conditions                      | Min.              | Typ. | Max.               | Unit |

|------------------------|-------------------------|------------------------------------------------------------------|--------------------------------------|-------------------|------|--------------------|------|

| CS1.<br>CS2            | tsl(cs·wr)              | Low level setup time<br>to WR falling edge                       | Active Case                          | 0                 |      |                    | ns   |

|                        | t <sub>HL</sub> (CS-WR) | Low level hold time<br>from WR rising edge                       | Active Case                          | 0                 |      |                    | ns   |

|                        | t <sub>SH(CS-WR)</sub>  | High level setup time<br>to WR falling edge                      | Inactive Case                        | 0                 |      |                    | ns   |

|                        | tHH(CS-WR)              | High level hold time<br>from WR rising edge                      | Inactive Case                        | 0                 |      |                    | ns   |

|                        | tsl(cs-RD)              | Low level setup time<br>to RD falling edge                       | Active Case                          | 0                 |      |                    | ns   |

|                        | tHL(CS-RD)              | Low level hold time<br>from RD rising edge                       | Active Case                          | 0                 |      |                    | ns   |

|                        | tsh(cs-RD)              | High level setup time<br>RD falling edge                         | Inactive Case                        | 0                 |      |                    | ns   |

|                        | t <sub>HH(CS-RD)</sub>  | High level hold time<br>from RD rising edge                      | Inactive Case                        | 0                 |      |                    | ns   |

| C/D                    | ts(C/D-WR)              | Setup time to write strobe end                                   |                                      | 180               |      |                    | ns   |

|                        | tH(C/D-WR)              | Hold time from<br>write strobe end                               |                                      | 25                |      |                    | ns   |

|                        | ts(c/D-RD)              | Setup time to read<br>strobe start                               |                                      | 20                |      |                    | ns   |

|                        | t <sub>H(C/D-RD)</sub>  | Hold time from read<br>strobe end                                |                                      | 25                |      |                    | ns   |

| DR<br>(data            | tw<br>tep               | Low state width<br>DP output delay                               | Instructions 5 and 6                 |                   |      | 2-t <sub>СК</sub>  | ns   |

| ready)                 | FU                      | from write strobe end<br>(active command)                        | Instruction 5, $C_L = 50 \text{ pf}$ | 5-t <sub>СК</sub> |      | 14-t <sub>СК</sub> | ns   |

| D0 to D7<br>(interface | ts(BUS-WR)              | Input setup time to<br>write strobe end                          |                                      | 130               |      |                    | ns   |

| bus)                   | tH(BUS WR)              | Input hold time<br>from write strobe end                         |                                      | 25                |      |                    | ns   |

|                        | tpd(BUS)                | Propagation time<br>from (active) falling<br>Edge of read strobe | C <sub>L</sub> = 200 pF              |                   |      | 130                | ns   |

|                        | thz(BUS)                | Propagation time<br>from (active) rising<br>Edge of read strobe  | 1.12                                 |                   |      | 80                 | ns   |

|                        |                         | to high impedance state                                          |                                      |                   |      |                    |      |

#### PCM TIMING, RESET

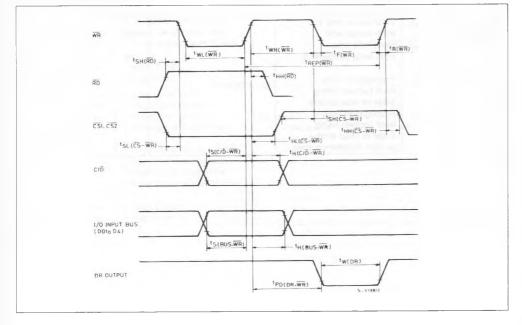

#### WRITE OPERATION TIMING

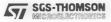

#### READ OPERATION TIMING

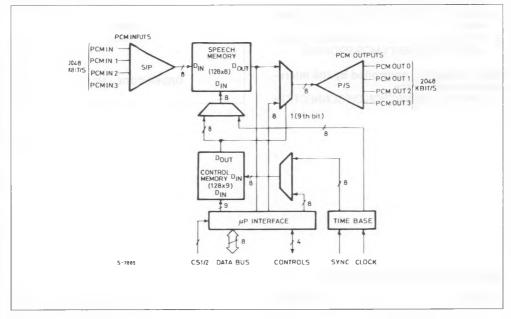

#### **GENERAL DESCRIPTION**

The M044 is intended for PABX Systems and digital like concentrators where a micromputer control approach is extensively used. It consists of a speech memory (SM), a control memory (CM), a serial/parallel and a parallel/serial converter, an internal parallel bus, and interface (8 data lines, 11 control signals) and dedicated control logic. By means of repeated clock division two timebases are generated. These are preset from an external synchronisation signal to two specific count numbers so that sequential scanning of the bases give synchronous addresses to the memories and I/O channel controls. The timebase for the input channels is delayed and the timbase for output channels is advanced with respect to the actual time. Each serial PCM input channel is converted to parallel data and stored in the speech memory at the beginning of any new time slot (according to first timebase) in the location determined by input pin number and time slot number. The control memory CM maintains the correspondences between input and output channels.

More exactly for any output pin/output channel combination the control memory gives either the full address of the speech memory location involved in the PCM transfer or an 8-bit word to be supplied to the parallel/serial output converter, A 9<sup>th</sup> bit at each CM location defines the data source for output links, low for SM, high for CM.

The late timebase is used to scan the output channels and to determine the pins to be serviced within each channel : enough idle cycles are left to the microprocessor for asynchronous instruction processing.

Two 8-bit registers OR1 and OR2 supply feedback data for control or diagnostic purposes; OR1 comes from internal bus i.e. from memories, OR2 gives an opcode copy and additional data to the microcomputer. A four byte-five bit stack register and an instruction register, under microcomputer control store input data available at the interface.

#### **PIN DESCRIPTION**

#### D7 to D0 (pins 17 to 24)

Data bus pins. The bidirectional bus is used to transfer data and instructions to / from the microprocessor. D0 is the least significant digit. The output bus is 8 bits wide ; input is only 5 bits wide. The bus is tristate and cannot be used while RESET is held low.

The meaning of input data, such as bus or channel numbers, and of expected output data is specified in detail by the instruction description.

#### C/D

Input control pin, select pin. In a write operation C/D = 0 qualifies any bus content as data, while C/D = 1 qualifies it as an opcode. In a read operation OR1 is selected by C/D = 0, OR2 by C/D = 1.

#### CS1, CS2

Commutative chip select pins. They enable the device to perform valid read/write operations (active low). Two pins allow row/column selection with different types of microprocessors ; normally one is tied to ground.

#### WR

Pin WR, when CS1 and CS2 are low, enables data transfer from microprocessor to the device. Data or opcode and controls are latched on WR rising edge. Because of internal clock resynchronization one single additional requirement is recommended in order to procedure a simultaneous instruction execution in a multichip configuration : WR rising edge has to be 20 to  $20 + t_{WL(CK)}$  nsed late relative to clock falling edge.

#### RD

When CS1 and  $\overline{\text{CS2}}$  are low and a low level on RD enables a register OR1 or OR2 read operation, through the bidirectional bus.

In addition, the rising edge of RD latches C/D and the match condition pins in order to direct the internal flow of operations. Because of internal clock resynchronization, one single additional requirement is recommended in order to produce a simultaneous instruction flow in a multichip configuration : the RD rising edge has to be 20 to 20 + twL<sub>(CK)</sub> nsec late relative to clock falling edge.

#### DR

This is the data ready signal, it informs the microprocessor that data is available for reading (through OR1/OR2 registers)

#### RESET

RESET control pin is normally used at the very beginning to inizialize the device or the network. Any logical status is reset and CM is set all "ones" after RESET going low.

The internal initialization routine takes one time frame whatever the RESET width on low level (minimum one cycle roughly), but it is repeated an integrer number of time frames as long as RESET is found low during 0 time slot.

Initialization pulls the interface bus immediately to a high impedance state. After the CM has been set to all "ones" the PCM output channels are also set to high impedance state (that is pulled to "ones").

#### CLOCK

Input master clock. Typical frequency is 4.096 MHz. First division gives an internal clock controlling the input and output channels bit rate.

#### SYNC

Input synchronization signal is active low. Typical frequency is 8 kHz.

Internal time bases are forced by synchronism to an assigned count number in order to restore channels and bit sequential addressing to a known state. Count difference between the bases is 32, corresponding to two time slots, that is the minimum PCM propagation time, or latency time.

#### PCM IN 3 TO PCM IN 0

PCM input busses or pins ; they accept a standard 2 Mbit/s rate. Bit 1 (sign bit) is the first of the serial sequence ; in a parallel conversion it is left adjusted as the most significant digit.

#### PCM OUT3 TO PCM OUT0

PCM output busses or pins ; bit rate and organization are the same as input pins.

Output buffers are open drain type in order to simplify wired-or connections and minimize current spike problems in multichip configuration systems. The device drives the output channels theoretically one bit time before input channels are needed by specifications : this feature allows inputs and outputs to be tied together cancelling any analog delay of digital outputs up to :

tDEL max = tbit - tPD(PCM)max + tPD(PCM)min

#### BIAS

Internally generated bias voltage (- 2.5 to - 3.0 V for V<sub>CC</sub> in the operating range). A max 220 pf capacitor connected to pin 5 provides improved filtering.

#### MIXED RD & WR OPERATIONS

In principle RD and WR operations are allowed in any order within specification constraints.

In practive, only one control pin is low at any given time when CS1 and CS2 are enabled.

If by mistake or hardware failure both  $\overline{RD}$  and  $\overline{WR}$  pins are low, the interface bus is internally pushed to tristate condition as long as  $\overline{WR}$  is held low and input registers are protected.

Registers OR1 and OR2 can be read in any order with a single RD strobe using C/D as multiplexing control; never the less this procedure is not recommended because the device is directed for instruction flow only according to data latched by RD rising edge.

Multiple RD operations of the same kind ar allowed without affecting the instruction flow : only "new" OR1 or OR2 read operations step the flow.

Input and output registers are held for sure in the previous state for the first 3 cycles following an opcode or an OR2 read.

#### FUNCTIONAL DESCRIPTION OF SPECIFIC MICROPROCESSOR OPERATIONS

The device, under microprocessor control, performs the following instructions :

1. CHANNEL CONNECTION/DISCONNECTION

2. CHANNEL DISCONNECTION

3. INSERTION OF A BYTE ON A PCM OUTPUT CHANNEL/CHANNEL DISCONNECTION

4. TRANSFER OF A SINGLE PCM OUTPUT CHANNEL SAMPLE

5. TRANSFER OF A SINGLE OUTPUT CHANNEL CONTROL WORD

Any input protocol is started by the microprocessor interface loading the internal stack register with 2 bytes (4 bytes for instructions 1 and 3) qualified as data bytes by C/D = 0 and a specific opcode qualified by  $C/\overline{D} = 1$  (match condition is normally needed).

At the end of an instruction it is normally recommended to read one or both registers.

#### INSTRUCTION TABLES

The most significant digits of OR2 are a copy of the PCM selected output bus ; the least significant digits of OR2 are the opcode. C8 is the control bit. In any case parentheses () define actual register content.

#### INSTRUCTION 1 : CHANNEL CONNECTION/DISCONNECTION

| Co  |    | Sign |    |      |            |     | Data | Bus |     |     |      | Notes                                    |

|-----|----|------|----|------|------------|-----|------|-----|-----|-----|------|------------------------------------------|

| C/D | CS | WR   | RD | D7   | D6         | D 5 | D4   | D 3 | D 2 | D 1 | D 0  |                                          |

| 0   | 0  | 0    | 1  | X    | Х          | Х   | Х    | Х   | Bi2 | Bit | Bi0  | 1 st Data Byte : selected input bus      |

| 0   | 0  | 0    | 1  | Х    | Х          | Х   | Ci4  | Ci3 | Ci2 | Ci1 | Ci0  | 2 nd Data Byte : selected input channel  |

| 0   | 0  | 0    | 1  | Х    | Х          | Х   | Х    | Х   | Bo2 | Bo1 | Bo0  | 3 rd Data Byte : selected input bus      |

| 0   | 0  | 0    | 1  | X    | Х          | Х   | Co4  | Co3 | Co2 | Co1 | Co0  | 4 th Data Byte : selected output channel |

| 1   | 0  | 0    | 1  | X    | Х          | Х   | Х    | 0   | 0   | 0   | 1    | Instruction Opcode                       |

| 0   | 0  | 1    | 0  | C7   | C6         | C5  | C4   | C3  | C2  | C1  | CO   | OR1 : CM Content Copy                    |

|     |    |      |    | (Bi2 | Bi1        | Bi0 | Ci4  | Ci3 | Ci2 | Ci1 | C(0) |                                          |

| 1   | 0  | 1    | 0  | A7   | <b>A</b> 6 | A5  | C8   | 0   | 0   | 0   | 1    | OR2                                      |

|     |    |      |    | (Bo2 | Bo1        | Bo0 | 0    | 0   | 0   | 0   | 1)   |                                          |

#### INSTRUCTION 2 : OUTPUT CHANNEL DISCONNECTION

| Co  | ntrol | Sign | als |            |           |           | Data | Bus |     |     | Notes |                                                     |

|-----|-------|------|-----|------------|-----------|-----------|------|-----|-----|-----|-------|-----------------------------------------------------|

| C/D | CS    | WR   | RD  | D7         | D 6       | D 5       | D 4  | D 3 | D 2 | D1  | D0    | Holes                                               |

| 0   | 0     | 0    | 1   | Х          | Х         | Х         | Х    | Х   | Bo2 | Bo1 | Bo0   | 1 st Data Byte : selected output bus                |

| 0   | 0     | 0    | 1   | X          | Х         | Х         | Co4  | Co3 | Co2 | Co1 | Co0   | 2 <sup>nd</sup> Data Byte : selected output channel |

| 1   | 0     | 0    | 1   | Х          | Х         | Х         | Х    | 0   | 0   | 1   | 0     | Instruction Opcode                                  |

| 0   | 0     | 1    | 0   | 1          | 1         | 1         | 1    | 1   | 1   | 1   | 1     | OR1 : CM Content Copy (output channel is inactive)  |

| 1   | 0     | 1    | 0   | A7<br>(Bo2 | A6<br>Ro1 | A5<br>Bo0 | 1    | 0   | 0   | 1   | 0     | OR2                                                 |

#### INSTRUCTION 3 : LOADING A MICROPROCESSOR BYTE

| Co  | ntrol | Sign | als |            |           |           | Data      | Bus       |           |            |           | Notes                                                               |

|-----|-------|------|-----|------------|-----------|-----------|-----------|-----------|-----------|------------|-----------|---------------------------------------------------------------------|

| C/D | CS    | WR   | RD  | D7         | D6        | D 5       | D 4       | D 3       | D 2       | <b>D</b> 1 | D 0       | Notes                                                               |

| 0   | 0     | 0    | 1   | X          | Х         | Х         | Х         | Х         | Ci7       | Ci6        | Ci5       | 1 st Data Byte : Most significant digits to be inserted             |

| 0   | 0     | 0    | 1   | X          | Х         | Х         | Ci4       | Ci3       | Ci2       | Ci1        | Ci0       | 2 <sup>nd</sup> Data Byte : Least significant digits to be inserted |

| 0   | 0     | 0    | 1   | X          | Х         | Х         | Х         | Х         | Bo2       | Bo1        | Bo0       | 3 rd Data Byte : selected output bus                                |

| 0   | 0     | 0    | 1   | Х          | Х         | Х         | Co4       | Co3       | Co2       | Co1        | Co0       | 4 th Data Byte : selected output channel                            |

| 1   | 0     | 0    | 1   | Х          | Х         | Х         | Х         | 0         | 1         | 0          | 0         | Instruction Opcode                                                  |

| 0   | 0     | 1    | 0   | C7<br>(Ci7 | C6<br>Ci6 | C5<br>Ci5 | C4<br>Ci4 | C3<br>Ci3 | C2<br>Ci2 | C1<br>Ci1  | C0<br>Ci0 | OR1 : CM content copy, that is for match condition                  |

| 1   | 0     | 1    | 0   | A7<br>(Bo2 | A6<br>Bo1 | A5<br>Bo0 | 1         | 0<br>0    | 1         | 0<br>0     | 0<br>0)   | OR2 : that is                                                       |

#### INSTRUCTION 4 : TRANSFER OF A SINGLE PCM SAMPLE

| Co  | ntrol | Sign | als |            |           |           | Data     | Bus |          |          |          | Notes                                                                  |

|-----|-------|------|-----|------------|-----------|-----------|----------|-----|----------|----------|----------|------------------------------------------------------------------------|

| C/D | CS    | WR   | RD  | D7         | D6        | D 5       | D 4      | D 3 | D 2      | D1       | DO       | Notes                                                                  |

| 0   | 0     | 0    | 1   | X          | Х         | Х         | Х        | Х   | Bo2      | Bo1      | Bo0      | 1 st Data Byte : selected output bus                                   |

| 0   | 0     | 0    | 1   | X          | Х         | Х         | Co4      | Co3 | Co2      | Co1      | Co0      | 2 nd Data Byte : selected output channel                               |

| 1   | 0     | 0    | 1   | Х          | Х         | Х         | Х        | 1   | 0        | 1        | 1        | Instruction Opcode                                                     |

| 0   | 0     | 1    | 0   | C7<br>S7   | C6<br>S6  | C5<br>S5  | C4<br>S4 |     | C2<br>S2 | C1<br>S1 | C0<br>S0 | OR1 : CM Content Copy if C8 = 1 ;<br>or<br>SM Content Sample if C8 = 0 |

| 1   | 0     | 1    | 0   | A7<br>(Bo2 | A6<br>Bo1 | A5<br>Bo0 | C8<br>C8 | 1   | 0        | 1        | 1<br>1)  | OR2 : that is                                                          |

Note : S7...S0 is a parallel copy of a PCM data, S7 is the most significant digit and the first of the sequence

12

| Co  | ntrol | Sign | als |      |     |     | Data | Bus |     |     |     | Notes                                              |

|-----|-------|------|-----|------|-----|-----|------|-----|-----|-----|-----|----------------------------------------------------|

| C/D | CS    | WR   | RD  | D7   | D 6 | D 5 | D4   | D 3 | D 2 | D 1 | D 0 | Notes                                              |

| 0   | 0     | 0    | 1   | Х    | Х   | Х   | X    | Х   | Bo2 | Bo1 | Bo0 | 1 st Data Byte : selected input bus                |

| 0   | 0     | 0    | 1   | X    | Х   | Х   | Co4  | Co3 | Co2 | Co1 | Co0 | 2 <sup>nd</sup> Data Byte : selected input channel |

| 1   | 0     | 0    | 1   | Х    | Х   | Х   | Х    | 1   | 0   | 0   | 0   | Instruction Opcode                                 |

| 0   | 0     | 1    | 0   | C7   | C6  | C5  | C4   | C3  | C2  | C1  | CO  | OR1 : CM selected CM word copy                     |

| 1   | 0     | 1    | 0   | A7   | A6  | A5  | C8   | 1   | 0   | 0   | 0   | OR2 : that is                                      |

|     |       |      |     | (Bo2 | Bo1 | Bo0 | 0    | 0   | 0   | 0   | 1)  |                                                    |

### INSTRUCTION 5 : TRANSFER OF AN OUTPUT CHANNEL CONTROL WORD

#### CONFERENCE CALL

A kit which includes Z80 µP and the M116 allows a flexible conference call system to be built up in which the participants can enter on any channel of the M044 (refer to M116 data sheet for detailed information).

#### TYPICAL APPLICATION