# **GAL20V8 Generic Array Logic**

#### **General Description**

The NSC E<sup>2</sup>CMOS<sup>TM</sup> GAL® device combines a high performance CMOS process with electrically erasable floating gate technology. This programmable memory technology applied to array logic provides designers with reconfigurable logic and bipolar performance at significantly reduced power levels.

The 24-pin GAL20V8 features 8 programmable Output Logic Macrocells (OLMCs) allowing each TRI-STATE® output to be configured by the user. Additionally, the GAL20V8 is capable of emulating, in a functional/fuse map/parametric compatible device, the most popular 24-pin PAL® device architectures.

Programming is accomplished using readily available hardware and software tools. NSC guarantees a minimum 100 erase/write cycles.

Unique test circuitry and reprogrammable cells allow complete AC, DC, cell and functionality testing during manufacture. Therefore, NSC guarantees 100% field programmability and functionality of the GAL devices. In addition, electronic signature is available to provide positive device ID. A

security circuit is built-in, providing proprietary designs with copy protection.

#### **Features**

- Electrically erasable cell technology

- Reconfigurable logic

- Reprogrammable cells

- Guaranteed 100% yields

- High performance E<sup>2</sup>CMOS technology

- Low power: 45 mA/90 mA max active

- High speed: 20 ns-35 ns max access

- Eight output logic macrocells

- Maximum flexibility for complex logic designs

- Also emulates 24-pin PAL devices with full function/fuse map/parametric compatibility

- Preload and power-on reset of all registers

- 100% functional testability

- Fully supported by National PLAN<sup>™</sup> development software

- High speed programming algorithm

- Security cell prevents copying logic

#### **PAL Replacement by Device Type**

| "Small-<br>PAL" Mode |      |      |      |       | egister<br>AL'' Mo | "Medium-<br>PAL" Mode |      |

|----------------------|------|------|------|-------|--------------------|-----------------------|------|

| 14L8                 | 16L6 | 18L4 | 20L2 | 20R8  | 20R6               | 20R4                  | 20L8 |

| 14H8                 | 16H6 | 18H4 | 20H2 | 20RP8 | 20RP6              | 20RP4                 | 20H8 |

| 14P8                 | 16P6 | 18P4 | 20P2 |       |                    |                       | 20P8 |

## **PAL Replacement by Speed/Power**

|     | PAL   |        | GAL                                  |  |  |  |  |

|-----|-------|--------|--------------------------------------|--|--|--|--|

| Rev | Speed | Power* | Rev                                  |  |  |  |  |

| B-2 | 25 ns | 105 mA | 25L or 20L (90 mA)<br>or 25Q (45 mA) |  |  |  |  |

| Α   | 25 ns | 210 mA | 25L or 20L (90 mA)                   |  |  |  |  |

| B-4 | 35 ns | 55 mA  | 30Q (45 mA)                          |  |  |  |  |

| A-2 | 35 ns | 105 mA | 30Q (45 mA)                          |  |  |  |  |

| STD | 35 ns | 210 mA | 25L (90 mA)                          |  |  |  |  |

<sup>\*</sup>Shown for Medium PAL products.

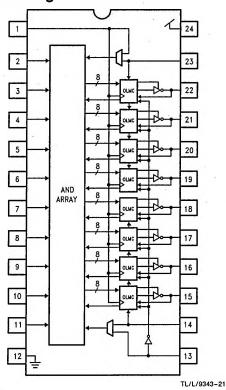

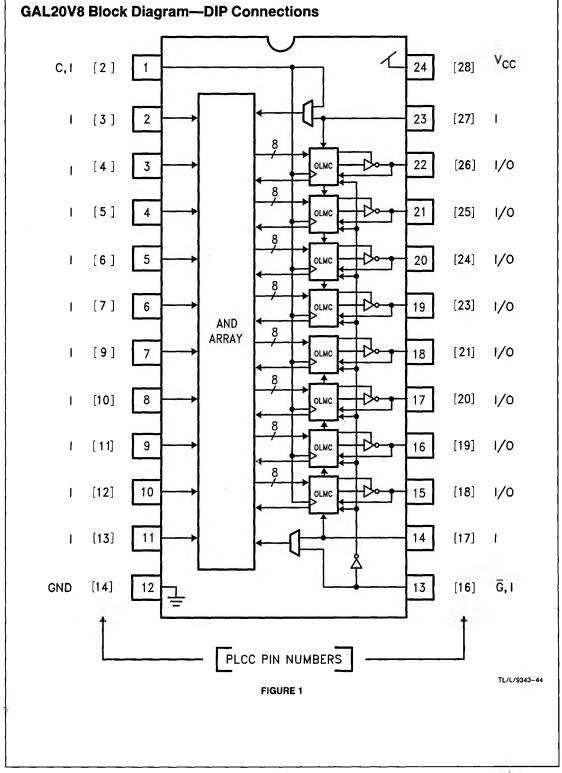

#### **Block Diagram—GAL20V8**

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) (Note 2)

-0.5V to +7.0V

Input Voltage (Note 2)

-2.5V to  $V_{CC} + 1.0$ V

Off-State Output Voltage

(Note 2)

-2.5V to  $V_{CC} + 1.0V$

Output Current

Storage Temperature

+ 100 mA -65°C to + 150°C

+ 100 mA F

$C_{ZAP} = 100 \text{ pF}$  $R_{ZAP} = 1500\Omega$

Lead Temperature

**ESD Tolerance**

Ambient Temperature

Junction Temperature

with Power Applied

(Soldering, 10 seconds)

Test Method: Human Body Model Test Specification: NSC SOP-5-028 -65°C to +125°C

-65°C to +1500°C

260°C

500V

## **Recommended Operating Conditions**

#### **SUPPLY VOLTAGE AND TEMPERATURE**

| Symbol          | Parameter                      | Commercial |     |      | Industrial |     |     | Military |     |     | Units |

|-----------------|--------------------------------|------------|-----|------|------------|-----|-----|----------|-----|-----|-------|

|                 | r arameter                     | Min        | Nom | Max  | Min        | Nom | Max | Min      | Nom | Max |       |

| V <sub>CC</sub> | Supply Voltage                 | 4.75       | 5   | 5.25 | 4.5        | 5   | 5.5 | 4.5      | 5   | 5.5 | ٧     |

| TA              | Operating Free-Air Temperature | 0          | 25  | 75   | -40        | 25  | 85  | -55      | 25  | -   | °C    |

| T <sub>C</sub>  | Operating Case Temperature     |            |     |      |            |     |     |          |     | 125 | °C    |

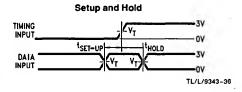

#### **AC TIMING REQUIREMENTS**

|                 |                                               | GAL20V8-20L<br>COM/IND |     | GAL20V8-25Q<br>GAL20V8-25L<br>COM/IND<br>MIL* |     | GAL20V8-35Q<br>GAL20V8-35L<br>COM/IND*<br>MIL |     | Units |     |

|-----------------|-----------------------------------------------|------------------------|-----|-----------------------------------------------|-----|-----------------------------------------------|-----|-------|-----|

| Symbol          | Para                                          |                        |     |                                               |     |                                               |     |       |     |

|                 |                                               | Min                    | Max | Min                                           | Max | Min                                           | Max | 1     |     |

| tsu             | Setup Time (Input or<br>Feedback before Clock | 15                     |     | 20                                            |     | 25                                            |     | ns    |     |

| t <sub>H</sub>  | Hold Time (Input after Clock)                 |                        | 0   |                                               | 0   |                                               | 0   |       | ns  |

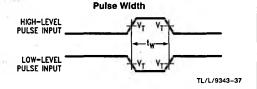

| t <sub>W</sub>  | Clock Pulse Width (Higl                       | h/Low)                 | 12  |                                               | 15  |                                               | 15  |       | ns  |

| CYCLE           | Clock Cycle Perlod<br>(with Feedback) (Note:  | 3)                     | 30  |                                               | 35  |                                               | 45  |       | ns  |

| fclk            | Clock Frequency                               | With Feedback          |     | 33.3                                          |     | 28.5                                          |     | 22.2  |     |

|                 | (Note 4)                                      | Without Feedback       |     | 41.6                                          |     | 33.3                                          |     | 33.3  | MHz |

| f <sub>l</sub>  | Input Frequency (Note 5)                      |                        |     | 50.0                                          |     | 40.0                                          |     | 33.3  |     |

| t <sub>PR</sub> | Clock Valid after Power                       |                        | 100 |                                               | 100 |                                               | 100 | ns    |     |

<sup>\*-25</sup>Q available only in COM/IND operating ranges;

Note 1: Absolute Maximum Ratings are those values beyond which the device may be permanently damaged. Proper operation is not guaranteed outside the specified recommended operating conditions.

Note 2: Some device pins may be raised above these limits during programming and preload operations according to the applicable specification.

Note 3: t<sub>CYCLE</sub> = t<sub>SU</sub> + t<sub>CLK</sub>

Note 4:  $f_{CLK}$  (with feedback) =  $(t_{CYCLE})^{-1}$

f<sub>CLK</sub> (without feedback) = (2 t<sub>w</sub>)-1

Note 5:  $t_1 = (t_{PD})^{-1}$

<sup>-30</sup>L available only in MIL operating range (for COM/IND, use -25L).

## **Electrical Characteristics** Over Recommended Operating Conditions

| Symbol           |                                          | Parameter              | Co                                                            | nditions                   | Temperature<br>Range | Min   | Тур | Max                | Units |

|------------------|------------------------------------------|------------------------|---------------------------------------------------------------|----------------------------|----------------------|-------|-----|--------------------|-------|

| V <sub>IH</sub>  | High Lev                                 | el Input Voltage       |                                                               |                            |                      | 2.0   |     | V <sub>CC</sub> +1 | ٧     |

| VIL              | Low Level Input Voltage                  |                        |                                                               |                            |                      | - 1.0 |     | 0.8                | ٧     |

| V <sub>OH</sub>  | High Lev                                 | el Output Voltage      | $V_{CC} = Min$ $I_{OH} = -3.2 \text{ m/s}$                    |                            | COM/IND              | 2.4   |     |                    | ٧     |

|                  |                                          |                        | ACC - MIII                                                    | $I_{OH} = -2.0 \text{ mA}$ | MIL                  | 2.4   |     |                    | ٧     |

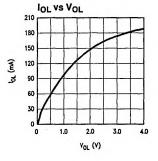

| V <sub>OL</sub>  | V <sub>OL</sub> Low Level Output Voltage |                        | V <sub>CC</sub> = Min                                         | I <sub>OL</sub> = 24 mA    | COM/IND              |       |     | 0.5                | ٧     |

|                  |                                          |                        | VCC - WIIII                                                   | I <sub>OL</sub> = 12 mA    | MIL                  |       |     | 0.5                | ٧     |

| lozh             | High Lev<br>Output C                     | el Off-State<br>urrent | $V_{CC} = Max, V_O = V_{CC}(Max)$                             |                            |                      |       |     | 10                 | μΑ    |

| lozL             | Low Level Off-State<br>Output Current    |                        | V <sub>CC</sub> = Max, V <sub>O</sub> = GND                   |                            |                      |       |     | -10                | μΑ    |

| <u></u>          | Maximun                                  | Input Current          | V <sub>CC</sub> = Max, V <sub>I</sub> = V <sub>CC</sub> (Max) |                            |                      | -     |     | 10                 | μА    |

| l <sub>iH</sub>  | High Lev                                 | el Input Current       | V <sub>CC</sub> = Max, V <sub>I</sub> = V <sub>CC</sub> (Max) |                            |                      |       |     | 10                 | μΑ    |

| IIL              | Low Leve                                 | el Input Current       | V <sub>CC</sub> = Max, V <sub>I</sub> = GND                   |                            |                      |       |     | -10                | μΑ    |

| los*             | Output S                                 | hort Circuit Current   | $V_{CC} = 5.0V, V_O = GND$                                    |                            |                      | -30   |     | -130               | mA    |

| lcc              | Supply                                   | Quarter Power          | f = 15 MHz,                                                   | V <sub>CC</sub> = Max      | СОМ                  |       |     | 45                 | mA    |

|                  | Current                                  | (GAL20V8-25Q, -35Q)    |                                                               |                            | MIL/IND              |       |     | 55                 | mA    |

|                  |                                          | Half Power             | f = 15 MHz,                                                   | V <sub>CC</sub> = Max      | сом                  |       |     | 90                 | mA    |

|                  |                                          | (GAL20V8-20L, -25L)    |                                                               |                            |                      |       |     | 110                | mA    |

| Cı               | Input Car                                | pacitance              | $V_{CC} = 5.0V, V_{I} = 2.0V$                                 |                            |                      |       |     | 8                  | pF    |

| C <sub>I/O</sub> | I/O Capa                                 | citance                | $V_{CC} = 5.0V$                                               | $V_{I/O} = 2.0V$           |                      |       |     | 10                 | pF    |

<sup>\*</sup>One output at a time for a maximum duration of one second @ 25°C.

# Switching Characteristics Over Recommended Operating Conditions

|                    |                                                            |                                                                                                       | GAL20V8-20L<br>COM/IND |     |                 | V8-25Q<br>)V8-25L | GAL20V8-35Q<br>GAL20V8-35L |     |       |

|--------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------|-----|-----------------|-------------------|----------------------------|-----|-------|

| Symbol             | Parameter                                                  | Conditions                                                                                            |                        |     | COM/IND<br>MIL* |                   | COM/IND*                   |     | Units |

|                    |                                                            |                                                                                                       | Min                    | Max | Min             | Max               | Min                        | Max |       |

| t <sub>PD</sub>    | Input or Feedback to Combinatorial Output                  | S1 Closed, C <sub>L</sub> = 50 pF                                                                     |                        | 20  |                 | 25                |                            | 30  | ns    |

| t <sub>CLK</sub>   | Clock to Registered<br>Output or Feedback                  | S1 Closed, C <sub>L</sub> = 50 pF                                                                     |                        | 15  |                 | 15                |                            | 20  | ns    |

| <sup>t</sup> PZXG  | G ↓ to Registered<br>Output Enabled                        | Active High: S1 Open, $C_L = 50 \text{ pF}$ Active Low: S1 Closed $C_L = 50 \text{ pF}$               |                        | 18  |                 | 20                |                            | 25  | ns    |

| ФхZG               | G ↑ to Registered<br>Output Disabled                       | From $V_{OH}$ : S1 Open,<br>$C_L = 5 pF$<br>From $V_{OL}$ : S1 Closed<br>$C_L = 5 pF$                 |                        | 18  |                 | 20                |                            | 25  | ns    |

| t <sub>PZXI</sub>  | Input to Combinatorial Output<br>Enabled via Product Term  | Active High: S1 Open,  C <sub>L</sub> = 50 pF  Active Low: S1 Closed  C <sub>L</sub> = 50 pF          |                        | 20  |                 | 25                |                            | 30  | en    |

| t <sub>PXZI</sub>  | Input to Combinatorial Output<br>Disabled via Product Term | From $V_{OH}$ : S1 Open,<br>$C_L = 5 \text{ pF}$<br>From $V_{OL}$ , S1 Closed<br>$C_L = 5 \text{ pF}$ |                        | 20  |                 | 25                |                            | 30  | ns    |

| t <sub>RESET</sub> | Power-Up to Registered<br>Output High                      | S1 Closed<br>C <sub>L</sub> = 50 pF                                                                   |                        | 45  |                 | 45                |                            | 45  | μs    |

<sup>-25</sup>Q available only in COM/IND operating ranges;

-30L available only in MIL operating range (for COM/IND, use -25L).

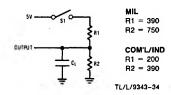

#### **AC Test Load**

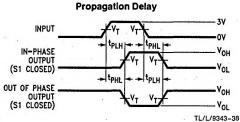

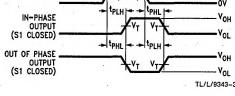

## **Test Waveforms**

#### Notes:

C<sub>L</sub> includes probe and jig capacitance.

$V_T = 1.5V$ .

Test inputs have rise and fall times of 5 ns between 0.3V and 2.7V. In the examples above, the phase relationships between inputs and outputs have been chosen arbitrarily.

## **Switching Waveforms**

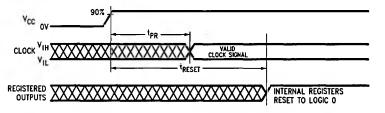

## **Power-Up Reset Waveforms**

TL/L/9343-42

# **Input/Output Schematics**

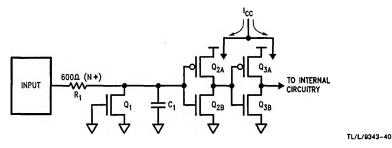

#### Input Translator/Buffer

## Input/Output Schematics (Continued)

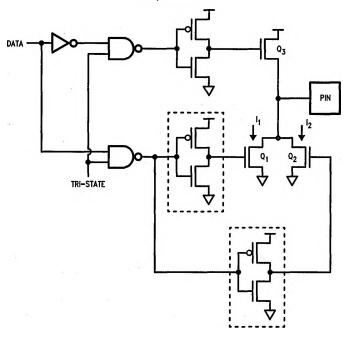

#### **Phased Output Turn-On Circuit**

TL/L/9343-41

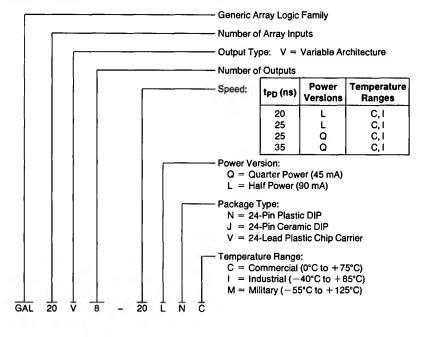

#### **Ordering Information**

The device number is used to form part of a simplified purchasing code where a package type and temperature range are defined as follows:

#### **Functional Description**

The GAL logic array consists of a programmable AND array with fixed OR-gate connections, similar to the bipolar PAL architecture. The logic array is organized as 20 complementary input lines crossing 64 "product term" lines with a programmable E2PROM cell at each intersection (2560 cells). Each programmable cell may establish a connection between an input line (true or complement phase of an array input signal) and a product term. A product term is satisfied (logically true) while all of the input lines "connected" to it are in the high logic state.

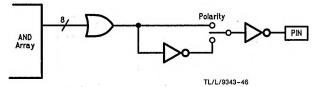

The 64 product terms are organized into eight output groups with eight terms each. Seven or eight of the product terms in each output group feed into an OR-gate to produce each output logic function; one of the product terms may instead be used to control the associated TRI-STATE device output. The fundamental transfer function of each GAL output is the familiar Boolean sum-of-products. Design development software is available which accepts Boolean equations and converts them automatically into GAL programming patterns.

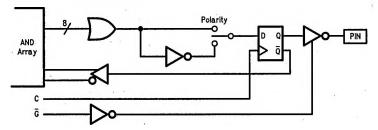

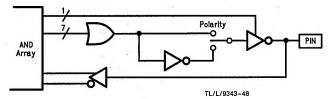

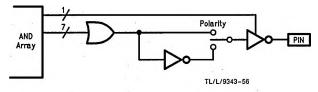

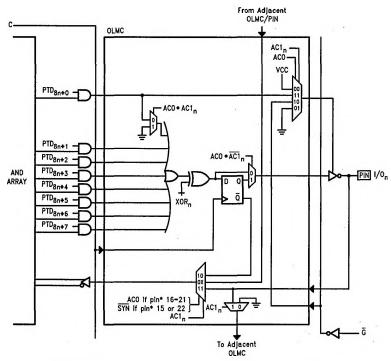

As shown in the GAL20V8 Block Diagram (Figure 1), a total of eight output logic functions are available. Each of the AND/OR logic functions feeds into an "output logic macrocell" (OLMC). The eight OLMCs control the flow of input and output signals between the logic array and the device's I/O pins.

Under control of an OLMC, each output may be designated either registered or combinatorial (non-registered). In the registered output configuration, the logic function output passes through a D-type flip-flop triggered by the rising edge of the clock input. Additionally, the logic function's output polarity may be designated active-low or active-high (adjusted before the register, if present). OLMC options such as these are selected using a set of programmable architecture control cells. These architecture cells are normally configured automatically by the development software or programming hardware.

All of the possible I/O configurations of the GAL20V8 are classified into three basic modes: "Small-PAL" mode, "Registered-PAL" mode and "Medium-PAL" mode. These modes correspond to the architectures of the PAL families which the GAL20V8 can emulate. The modes determine the mixture of OLMC configurations which can be selected for the device. The OLMC Selection table (Table I) lists which functions can be selected on device pins\* 1, 13 and 15 through 22 for each of the three modes. The logic diagrams in Figure 3 illustrate these OLMC functions.

"OUTPUT" represents the always-active combinatorial output configuration available in the "Small-PAL" mode. "REGISTER" is the registered output with register feedback available in the "Registered-PAL" mode. "I/O" is the combinatorial bidirectional I/O available in "Registered-PAL" and "Medium-PAL" modes. "TRI-STATE" is the TRI-STATE combinatorial output function appearing on pins\* 15 and 22 in the "Medium-PAL" mode. "INPUT" in Table I denotes an OLMC used as a dedicated input only.

In the "Small-PAL" and "Medium-PAL" modes (Table I), pins\* 1 and 13 are always dedicated inputs. In the "Registered-PAL" mode, however, pin\* 1 becomes the clock input controlling all OLMC registers, and pin\* 13 becomes the output enable (G) input controlling the TRI-STATE outputs of all registered OLMCs. Within the "Small-PAL" and "Registered-PAL" modes in Table I, the functions of pins\* 15 through 22 can be selected individually from either of the two functions listed. For example, in "Registered-PAL" mode, pins\* 15 through 22 can each be designated as either a registered output or a combinatorial I/O. The "Medium-PAL" mode represents a single fixed configuration used to emulate combinatorial medium PAL devices (20L8, 20H8, 20P8).

Table II lists the bipolar PAL products which the GAL20V8 can emulate, and the specific input/output configurations used. This is just a subset, however, of all the configurations provided in Table I.

All registers in a GAL device are reset to the low state upon power-up. The active-low outputs, in turn, assume high logic levels (if enabled) regardless of the selected output polarity. This may simplify sequential circuit design and test. To ensure successful power-up reset,  $V_{CC}$  must rise monotonically until the specified operating voltage is attained. During power-up, the clock input should assume a valid, stable logic state as early as possible (within the specified time,  $t_{PR}$ ) to avoid interfering with the reset operation. The clock input should also remain stable until after the power-up reset operation is completed to allow the registers to capture the proper next state on the first high-going clock transition.

It should be noted that the switching of any input not logically connected to a product term or logic function has no effect on the associated output logic state. To minimize power consumption, however, unused inputs should be connected to a stable logic level such as ground or  $V_{CC}$  (CMOS GAL inputs may be tied directly to the supply voltage without causing excessive loading conditions).

Applies to 24-pin DIP packages for GAL20V8; refer to the 28-lead PCC Connection Diagram for conversion.

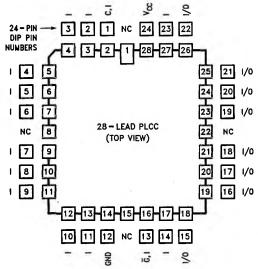

#### 28-Lead PLCC Connection Diagram

FIGURE 2

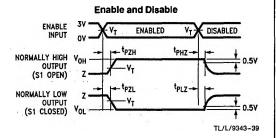

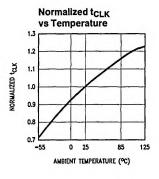

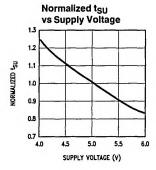

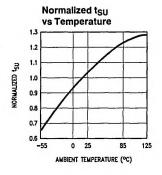

# Clock/Input Frequency Specifications

The clock frequency (fCLK) parameter listed in the Recommended Operating Conditions table specifies the maximum speed at which the GAL registers are guaranteed to operate. Clock frequency is defined differently for the two cases in which register feedback is used versus when it is not. In a data-path type application, when the logic functions fed into the registers are not dependent on register feedback from the previous cycle (i.e. based only on external inputs), the minimum required cycle period (f<sub>CLK</sub>-1 without feedback) is defined as the greater of the minimum clock period (tw high + tw low) and the minimum "data window" period (tsu + t<sub>H</sub>). This assumes optimal alignment between data inputs and the clock input. In sequential logic applications such as state machines, the minimum required cycle period (tcycle =  $f_{CLK}^{-1}$  with feedback) is defined as  $t_{CLK} + t_{SU}$ . This provides sufficient time for outputs from the registers to feed back through the logic array and set up on the inputs to the registers before the end of each cycle.

The input frequency (f<sub>i</sub>) parameter specifies the maximum rate at which each GAL input can be toggled and still produce valid logic transitions on each combinatorial output. The f<sub>i</sub> specification is derived as the inverse of the combinatorial propagation delay (t<sub>Pl</sub>).

## **Design Development Support**

A variety of software tools and programming equipment is available to support the development of designs using GAL products. Typical software packages accept Boolean logic equations to define desired functions. Most are available to run on personal computers and generate a JEDEC-compatible "cell-map" (analogous to a PAL "fuse-map"). The industry-standard JEDEC format ensures that the resulting

cell-map file can be down-loaded into a variety of programming equipment. Many software packages and programming units support a large variety of programmable logic products as well. The PLANTM software package from National Semiconductor supports all programmable logic products available from National and is fully JEDEC-compatible. PLAN software also provides automatic device selection based on the designer's Boolean logic equations.

TL/L/9343-45

National strongly recommends using only approved programming hardware and software for developing GAL designs. Programming using unapproved equipment generally voids all guarantees. Approved programmers incorporate specialized programming algorithms that program the array and automatically configure the architecture cells. To ensure data retention and reliability, the programming algorithm also tracks the number of programming cycles to which each GAL device has been subjected since shipment, and stores this information automatically in the device.

The special GAL programming algorithm can also program a GAL device using a standard fuse-map developed for any of the emulated PAL products. PAL fuse-maps can be created by any JEDEC-compatible PAL development software or by loading the fuse pattern from an existing programmed PAL device into the programming unit (provided the PAL device has not been secured). However, to utilize the full flexibility of the GAL architecture, true GAL development software (such as PLAN software) is recommended.

Detailed logic diagrams showing all JEDEC cell-map addresses in the GAL logic array and OLMC are provided for direct map editing and diagnostic purposes (see "Programming Details"). For a list of current software and programming support tools available for these devices, please contact your local National sales representative or distributor. If detailed specifications of the GAL programming algorithm are needed, please contact the National Semiconductor Programmable Device Support department.

## **OLMC Selection Table**

|                  | TABLE                 |                      |

|------------------|-----------------------|----------------------|

| "Small-PAL" Mode | "Registered-PAL" Mode | "Medium-PAL"<br>Mode |

| INPUT            | CLOCK                 | INPUT                |

| INPUT or OUTPUT* | REGISTER or I/O       | TRI-STATE**          |

| INPUT or OUTPUT* | REGISTER or I/O       | 1/0                  |

| INPUT or OUTPUT* | REGISTER or I/O       | 1/0                  |

| OUTPUT*          | REGISTER or I/O       | 1/0                  |

| OUTPUT*          | REGISTER or I/O       | 1/0                  |

| INPUT or OUTPUT* | REGISTER or I/O       | 1/0                  |

| INPUT or OUTPUT* | REGISTER or I/O       | 1/0                  |

| INPUT or OUTPUT* | REGISTER or I/O       | TRI-STATE**          |

| INPUT            | OUTPUT ENABLE (G)     | INPUT                |

<sup>·</sup> Active combinatorial output

Note: Pin numbers above apply to 24-pin DIP packages; refer to the 28-lead PCC Connection Diagram for conversion.

# **PAL Replacement Configurations**

|                 |         |                       |         | TABLE II |          |         |                       |          |          |                      |  |  |  |

|-----------------|---------|-----------------------|---------|----------|----------|---------|-----------------------|----------|----------|----------------------|--|--|--|

|                 |         |                       |         | "Small-P | AL" Mode |         | "Registered-PAL" Mode |          |          | "Medium-PAL"<br>Mode |  |  |  |

|                 |         |                       | INPUT   | INPUT    | INPUT    | INPUT   | CLOCK                 | CLOCK    | CLOCK    | INPUT                |  |  |  |

| ΓE              | 0       | 24) v <sub>∞</sub>    |         |          |          | -111    |                       |          |          |                      |  |  |  |

| 1 2             |         | 221                   | OUTPUT* | INPUT    | INPUT    | INPUT   | REGISTER              | 1/0      | 1/0      | TRI-STATE**          |  |  |  |

| A<br>  I<br>  I |         | 20                    | OUTPUT* | OUTPUT*  | INPUT    | INPUT.  | REGISTER              | REGISTER | 1/0      | 1/0                  |  |  |  |

| 1 3             |         | 20 →                  | OUTPUT* | OUTPUT*  | OUTPUT*  | INPUT   | REGISTER              | REGISTER | REGISTER | 1/0                  |  |  |  |

| 1 6             | GAL20V8 | <b>19</b> →           | OUTPUT* | OUTPUT*  | OUTPUT*  | OUTPUT* | REGISTER              | REGISTER | REGISTER | 1/0                  |  |  |  |

| 1 1 1 1 1       |         | <u> </u>              | OUTPUT  | OUTPUT*  | OUTPUT*  | OUTPUT* | REGISTER              | REGISTER | REGISTER | 1/0                  |  |  |  |

| 1 🖪             |         | ╝──                   | OUTPUT* | OUTPUT*  | OUTPUT*  | INPUT   | REGISTER              | REGISTER | REGISTER | 1/0                  |  |  |  |

| 1 II            |         | ⊡——                   | OUTPUT* | OUTPUT*  | INPUT    | INPUT   | REGISTER              | REGISTER | 1/0      | 1/0                  |  |  |  |

| 1 10            |         | <u>ॼ</u> —→           | OUTPUT* | INPUT    | INPUT    | INPUT   | REGISTER              | 1/0      | 1/0      | TRI-STATE**          |  |  |  |

| CHD [[2]        |         | ☑ ·<br>☑ <del>·</del> | INPUT   | INPUT    | INPUT    | INPUT   | G                     | G        | G        | INPUT                |  |  |  |

|                 |         | TL/L/9343-57          | 14L8    | 16L6     | 18L4     | 20L2    | 20R8                  | 20R6     | 20R4     | 20L8                 |  |  |  |

|                 |         | Emulated              | 14H8    | 16H6     | 18H4     | 20H2    | 20RP8                 | 20RP6    | 20RP4    | 20H8                 |  |  |  |

|                 |         | PAL Products          | 14P8    | 16P6     | 18P4     | 20P2    |                       | - 1      |          | 20P8                 |  |  |  |

Active combinatorial output.

Note: Pin numbers above apply to 24-pin DIP packages; refer to the 28-pin PCC Connection Diagram for conversion.

<sup>\*\*</sup>TRI-STATE combinatorial output

<sup>\*\*</sup>TRI-STATE combinatorial output.

# **OLMC Configurations**

#### **OUTPUT (Active Combinatorial Output)**

#### **REGISTER (Registered Output)**

TL/L/9343-47

#### I/O (Combinatorial Input/Output)

#### TRI-STATE (TRI-STATE Combinatorial Output)

FIGURE 3

#### **Security Cell**

A security cell is provided on all GAL20V8 devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, the circuitry enabling array access is disabled, preventing further programming or verification of the array. The security cell can be erased only in conjunction with the array during a bulk erase cycle, so the original configuration can never be examined once this cell is programmed.

#### **Electronic Signature**

Each GAL device contains an electronic signature word consisting of 64 bits of reprogrammable memory. The electronic signature word can be programmed to contain any identification information desired by the user. Some uses include pattern identification labels, revision numbers, dates, inventory control information, etc. The data stored in the electronic signature word has no effect on the functionality of the device. The information is read out of the device using the normal program verification procedure provided by the programming equipment. The information may be accessed at any time independent of the state of the security cell. National's PLAN development software allows electronic signature data to be entered by the user and downloaded to the programming equipment.

#### **Bulk Erase**

The programming equipment automatically performs a bulk erase operation prior to each programming operation. No special erase operation need be performed by the user. Bulk erase clears the logic array, architecture cells, security cell, and electronic signature information. The GAL device is thereby reverted back to its virgin state.

#### **Latch-Up Protection**

GAL devices are designed with an on-chip charge pump to negatively bias the substrate. The negative bias is of sufficient magnitude to prevent input undershoots from causing the circuitry to latch. Additionally, outputs are designed with n-channel pullups instead of the traditional p-channel pullups to eliminate any possibility of SCR induced latching.

## **Manufacturer Testing**

Because of E<sup>2</sup>CMOS technology, GAL devices can be reprogrammed in milliseconds. This allows each device to be completely tested by the manufacturer using numerous logic array and architecture patterns prior to shipping. Every programmable cell and every logic path through every device is fully tested for programmability, functionality and performance to all AC and DC parameters. The customer can therefore expect 100% programming and functional yield and 100% compliance of all GAL products to datasheet specifications.

The testing procedure performed on all GAL devices by the manufacturer tests all aspects of device operation. Extensive testing of all programmable cells in the device include margin testing, internal verify, and program retention during high-temperature bake. All DC and AC parameters are tested at hot and cold temperatures using a variety of worst-case logic and signal patterns. Functional tests include reprogramming each OLMC to all valid architectural configurations.

#### **Register Preload**

The register preload feature allows OLMC registers to be directly loaded with any desired data pattern. It also allows the present state of OLMC registers to be examined regardless of TRI-STATE control conditions. This simplifies testing of devices after programming. A device may be put into any desired register state at any point during the functional test sequence. The test sequence may then be resumed to verify proper next-state transitions. This allows complete verification of sequential logic circuits, including states that are normally impossible or difficult to reach. It may also shorten the overall test time significantly.

Register preload is not an operational mode and is not intended for board-level testing because elevated voltage levels must be applied to the device. The programming equipment normally provides the register preload capability as part of its functional test facility. Note that the testing of GAL devices after programming by the user may be considered unnecessary because all E<sup>2</sup>CMOS GAL products are completely tested by the manufacturer, guaranteeing 100% post-programming functional yield.

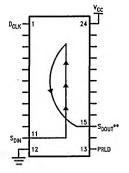

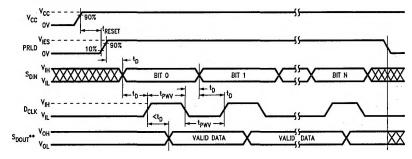

The register preload algorithm is described for those users who wish to test programmed GAL devices using test equipment other than approved GAL programming equipment. As shown in the Register Preload Waveform in *Figure 5*, the preload sequence must not begin until the normal power-up reset operation has completed (after time t<sub>RESET</sub>). The device is placed into preload mode by raising the "PRLD" input (pin\* 13) to voltage V<sub>IES</sub>, as specified in the Register Preload Specifications (Table III).

To preload the OLMC registers, a series of data bits are shifted into the device on the "S<sub>DIN</sub>" input (pin\* 11), one bit for each OLMC in which registered output has been selected. (Non-registered OLMCs are bypassed.) The shift sequence is clocked by the rising edge of the "D<sub>CLK</sub>" input (pin\* 1). The data stream is shifted in through the registered OLMC with the lowest corresponding pin number, and then "upward" through all remaining registered OLMCs in pinnumber ascending order. Therefore, the first data bit in the series is ultimately loaded into the registered OLMC with the highest corresponding pin number, as shown in Figure 4. \*Applies to 24-pin DIP packages for GAL20V8; refer to the 28-lead PCC

#### Register Preload (Continued)

As the data series is shifted into the S<sub>DIN</sub> input, the contents of all registers (in registered OLMCs) are shifted "upward" and out onto the "S<sub>DOUT</sub>" output (pin\* 15). Complete present-state information can be examined in this manner. Test fixtures can be devised to test several GAL devices in which the S<sub>DOUT</sub> pin of each chip is connected to the S<sub>DIN</sub> pin of the next, and all preload and present-state data can be shifted around a single serial loop.

Note that when shifting register data into  $S_{DIN}$  or out of  $S_{DOUT}$ ,  $V_{IL}/V_{OL} =$  register reset (0), and  $V_{IH}/V_{OH} =$  register set (1). These 0 and 1 register states are always inverted (active-low) on the normal output pins regardless of the selected output polarity (polarity affects logic function values before register inputs).

Applies to 24-pin DIP packages for GAL20V8; refer to the 28-lead PCC Connection Diagram for conversion.

TL/L/9343-17

\*\* The  $S_{DOUT}$  output buffer is an open drain output during preload. This pin should be terminated to  $V_{CC}$  with a 10  $k\Omega$  resistor.

FIGURE 4. Output Register Preload Pinout

## **Register Preload Specifications**

#### **TABLE III**

| Symbol             | Parameter                                      | Conditions                        | Min  | Тур | Max             | Units |

|--------------------|------------------------------------------------|-----------------------------------|------|-----|-----------------|-------|

| V <sub>IH</sub>    | Input Voltage (High)                           |                                   | 2.40 |     | Vcc             | V     |

| V <sub>IL</sub>    | Input Voltage (Low)                            |                                   | 0.00 |     | 0.50            | ٧     |

| V <sub>IES</sub>   | Register Preload Input Voltage                 |                                   | 14.5 | 15  | 15.5            | ٧     |

| V <sub>OH</sub>    | Output Voltage (High) (Note 1)                 |                                   |      |     | V <sub>CC</sub> | V     |

| V <sub>OL</sub>    | Output Voltage (Low) (Note 1)                  | I <sub>OL</sub> ≤ 12 mA           | 0.00 |     | 0.50            | V     |

| կլդ, կլ            | Input Current (Programming)                    |                                   |      | ±1  | ±10             | μΑ    |

| Юн                 | High Level Output Current (Note 1)             | V <sub>OH</sub> ≤ V <sub>CC</sub> |      |     | 10              | μΑ    |

| tpwv               | Verify Pulse Width                             |                                   | 1    | 5   | 10              | μs    |

| t <sub>D</sub>     | Pulse Sequence Delay                           |                                   | 1    | 5   | 10              | μs    |

| t <sub>RESET</sub> | Register Reset Time from Valid V <sub>CC</sub> |                                   |      |     | 45              | μs    |

Note 1: The Spout output buffer is an open drain output. This pin should be terminated to V<sub>CC</sub> with a 10k resistor.

## **Register Preload Waveforms**

TL/L/9343-16

FIGURE 5

<sup>\*\*</sup>The Spout output buffer is an open drain output during preload. This pin should be terminated to V<sub>CC</sub> with a 10 kΩ resistor.

# **OLMC Logic Diagram**

\*Applies to 24-pin DIP packages for GAL20V8; refer to the 28-lead PCC Connection Diagram for conversion.

FIGURE 6

TL/L/9343-53

## **OLMC Architecture Programming**

**TABLE IV**

|           | "Sı                                              | nall-PAL" Mod                                    | le     | "Regis      | stered-PAL" M                  | ode                                   | "Medium-PA           | L" Mode                               |  |

|-----------|--------------------------------------------------|--------------------------------------------------|--------|-------------|--------------------------------|---------------------------------------|----------------------|---------------------------------------|--|

|           | Fund                                             | Function  Function  JEDEC Input Line #s (Note 1) |        |             | tion                           | JEDEC<br>Input<br>Line #s<br>(Note 1) | Function             | JEDEC<br>Input<br>Line #s<br>(Note 1) |  |

| Pin 1     | INPUT                                            | INPUT                                            | 2, 3   | CLOCK       | CLOCK                          |                                       | INPUT                | 2, 3                                  |  |

| Pin 23    | INPUT                                            | INPUT                                            | 6,7    | INPUT       | INPUT                          | 2,3                                   | INPUT                | 6, 7                                  |  |

| ***Pin 22 | OUTPUT*                                          | INPUT                                            | 10, 11 | REGISTER    | 1/0                            | 6,7                                   | TRI-STATE**          |                                       |  |

| ***Pin 21 | OUTPUT*                                          | INPUT                                            | 14, 15 | REGISTER    | 1/0                            | 10, 11                                | 1/0                  | 10, 11                                |  |

| ***Pin 20 | OUTPUT*                                          | INPUT                                            | 18, 19 | REGISTER    | 1/0                            | 14, 15                                | 1/0                  | 14, 15                                |  |

| ***Pin 19 | OUTPUT*                                          | NC                                               |        | REGISTER    | 1/0                            | 18, 19                                | 1/0                  | 18, 19                                |  |

| ***Pin 18 | OUTPUT*                                          | NC                                               |        | REGISTER    | 1/0                            | 22, 23                                | 1/0                  | 22, 23                                |  |

| ***Pin 17 | OUTPUT*                                          | INPUT                                            | 22, 23 | REGISTER    | 1/0                            | 26, 27                                | 1/0                  | 26, 27                                |  |

| ***Pin 16 | OUTPUT*                                          | INPUT                                            | 26, 27 | REGISTER    | 1/0                            | 30, 31                                | 1/0                  | 30, 31                                |  |

| ***Pin 15 | OUTPUT*                                          | INPUT                                            | 30, 31 | REGISTER    | 1/0                            | 34, 35                                | TRI-STATE**          |                                       |  |

| Pin 14    | INPUT                                            | INPUT                                            | 34, 35 | INPUT       | INPUT                          | 38, 39                                | INPUT                | 34, 35                                |  |

| Pin 13    | INPUT                                            | INPUT                                            | 38, 39 | G           | G                              |                                       | INPUT                | 38, 39                                |  |

|           | AC1 <sub>n</sub> = 0                             | AC1 <sub>n</sub> = 1                             |        | $AC1_n = 0$ | AC1 <sub>n</sub> = 1           |                                       | AC1 <sub>n</sub> = 1 |                                       |  |

|           | SY                                               | N = 1, AC0 =                                     | 0      | SYI         | SYN = 0, AC0 = 1               |                                       |                      | SYN = 1, AC0 = 1                      |  |

|           | All outputs are combinatorial and always active. |                                                  |        | At le       | east one output<br>registered. | All I/O pins are combinatorial.       |                      |                                       |  |

Note: Pin numbers above apply to 24-pin DIP packages; refer to the 28-lead PCC Connection Diagram for conversion.

Note 1: All even and odd numbered JEDEC input line numbers correspond to true and complement array inputs, respectively.

<sup>\*</sup>Active combinatorial output.

\*\*TRI-STATE combinatorial output.

\*\*\*AC1<sub>n</sub> applies to these I/O pins only.

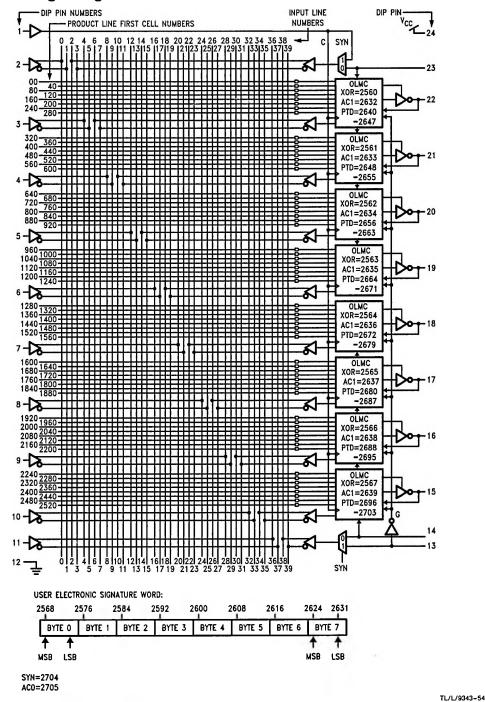

## **GAL20V8 Logic Diagram**

JEDEC Logic Array Cell Number = Product Line First Cell Number + Input Line Number

FIGURE 7

#### **Programming Details**

Understanding the information in this section is not essential when using approved programming equipment and software for developing GAL designs. This is a more thorough disclosure of the GAL architecture provided for direct JEDEC cell-map editing and diagnostic purposes. This section alone, however, does not contain sufficient information to implement the GAL programming algorithm. If detailed specifications of the GAL programming algorithm are needed, please contact the National Semiconductor Programmable Device Support department.

As mentioned in the Functional Description, the OLMC is responsible for selecting input and/or output paths, registered vs. combinatorial outputs, active-high or low polarity, and common vs. locally-controlled TRI-STATE control. Additionally, the OLMCs select between alternate logic array input paths to maintain JEDEC cell-map compatibility with either "small-PAL" or "medium-PAL" logic arrays.

The various configurations of the OLMCs are controlled by a set of programmable "architecture" cells, separate from the logic-defining array cells. Each GAL device contains two "global" architecture cells, "SYN" and "ACO", which affect all OLMCs. Each of the devices's eight OLMCs also contains two "local" cells, "AC1" and "XOR". The OLMC Logic Diagram in *Figure* 6 shows how the architecture cells select the different paths through the OLMC.

The SYN bit controls whether a device will have any registered outputs (SYN = 0) or will be purely combinatorial (SYN = 1). The SYN bit determines whether device pins\* 1 and 13 are used as the clock and global TRI-STATE control inputs (SYN = 0) or whether they are ordinary inputs (SYN = 1). The AC0 bit selects between the "Small-PAL" mode and the "Medium/Registered-PAL" modes. The function of the AC1 bits depend on the state of the AC0 bit. In "Small-PAL" mode (AC0 = 0), the AC1 bit in each OLMC determines whether the associated device pin is an output (AC1 = 0) or an input (AC1 = 1). In "Registered-PAL" mode (ACO = 1), the AC1 bit determines whether each OLMC is registered (AC1 = 0) or combinatorial (AC1 = 1). In "Medium-PAL" mode (AC0 = 1), the AC1 bits in all OLMCs must be set to 1 (combinatorial). All of the valid architecture bit configurations are shown in the OLMC Architecture table (Table IV), which has the same familiar format used in the OLMC Selection table (Table I).

Independent of SYN, AC0 and the AC1 bits, the XOR bit in each OLMC selects between active-low (XOR = 0) or active-high (XOR = 1) output polarity.

Applies to 24-pin DIP packages for GAL20V8; refer to the 28-lead PCC Connection Diagram for conversion.

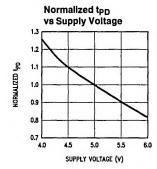

## **Typical Performance Characteristics**

TL/L/9343-19