## 0.5 Micron CMOS Standard Cell Data Book AMI500XXXX 5.0 Volt Revision 1.1

Copyright © 2002 AMI Semiconductor, Inc. (AMIS). All rights reserved. Trademarks registered.®

Information furnished by AMIS in this publication is believed to be accurate. Devices sold by AMIS are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. AMIS makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMIS makes no warranty of merchantability or fitness for any purposes. AMIS reserves the right to discontinue production and change specifications and prices at any time and without notice.

AMI Semiconductor's products are intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements or high reliability applications such as military, medical life-support or life-sustaining equipment, are specifically **not** recommended without additional processing by AMIS for such application.

| General Introduction          | ix  |

|-------------------------------|-----|

| Section 1 - Selection Guide   | 1-1 |

| Section 2 - Overview          | 2-1 |

| Section 3 - Core Logic        | 3-1 |

| Section 4 - Pad Logic         | 4-1 |

| Section 5 - Megacells         | 5-1 |

| Section 6 - Memories          | 6-1 |

| Section 7 - Sales Information | 7-1 |

iv

## **Selection Guide**

Section 1

## Overview Section 2

Core Logic Section 3

Pad Logic Section 4

Megacells

Selection Guide

Library Characteristics

Core Locic

Sales Informatio

## Memories Section 6

Section 5

## **Sales Information**

Section 7

v

#### On-line updates to this information

The information contained herein is the most current and accurate available at this time. In order to assist in the design of ASICs, AMIS has published several application notes on a wide range of design topics that can be accessed on-line at <a href="http://www.amis.com/tech\_info">http://www.amis.com/tech\_info</a>. Please visit the AMIS web site to ensure that you have the most current information prior to beginning the design of your ASIC.

## General Introduction

#### AMI5HS 0.5 micron CMOS Standard Cell

#### AMI Semiconductor - Providing customers the best total ASIC solution for more than 30 years

AMI Semiconductor (AMIS) pioneered the development of the world's first custom MOS ICs in 1966. With more experience than any other ASIC vendor, you can be assured that when you bring your ASIC development project to AMIS, you are working with a dependable team that has the depth of experience to provide you with an optimum solution, on time and on budget.

The vision shared by all employees at AMIS is expressed in our mission statement:

Through the smart application of mixed-signal and digital ASIC technology, AMIS makes it easier for its customers to get to market faster and more economically with better end products.

AMIS strives to realize this vision by offering a range of products and services aimed at improving cycle time, reducing overall design cost, achieving world-class quality and reliability, and designing to customer needs.

AMIS provides a full range of digital and mixed-signal ASICs, including high voltage and sensor interface ASICs, low data rate RF products, system level integration, FPGA-to-ASIC conversion, and modular foundry services.

AMIS operates globally with world wide headquarters in Pocatello, Idaho and European headquarters in Oudenaarde, Belgium. AMIS also owns a wafer sort and final test facility in Manilla, Philippines.

#### Markets

- Automotive

- Medical

- Industrial

- Military

- Communications

- Computer

#### **Sales and Distribution**

- Full-service sales and technical support offices are located in key markets throughout North America, Europe, and the Asia Pacific region.

- Technical service centers located in North America and Europe offer customers a full range of digital and mixed-signal ASIC design resources and services.

- For the most current sales information, go to www.amis.com/sales.

#### AMI500xxxx 0.5 micron CMOS Standard Cell

#### Description

#### **Features**

- Minimum drawn length: 0.6μ

- Excellent performance:

- 590 MHz maximum toggle rate on clocked flipflops ( $T_J = 135^{\circ}C$ )

- 218 ps delay (FO=2; L=2mm) for a 2-input NAND gate

- 103 ps delay (FO=2; L=0mm) for a 2-input NAND gate

- -6 ns clock to out performance (CL = 35 pF)

- Unparalleled temperature ranges:

- Operating temperatures range from -55 to 125°C.

#### Clock Tree Synthesis:

Clock drivers are placed to minimize clock skew and latency effects on circuit performance. Parameterized clock buffers model the clock trees before layout. AMIS matches the simulation parameters of the prelayout models with a physical clock tree during layout.

#### • Cost driven architecture:

A choice of 2 or 3 level metal interconnect provides the lowest device cost for the number of gates and pads required.

#### • Extensive library for quick design:

- Complete primary cell and I/O library

- Synchronous ROM compiler from 64x1 to 16Kx32 bits

- Megacells include processors, peripherals, and datapath synthesizers

- 100% compatible with AMI Semiconductor's proven ASIC Library

#### • Extensive RAM support:

- Asynchronous, synchronous, single, dual, and n-port

- Build from any configuration of 16x1 and 256x8, 512x4, 1024x2, and 2048x1 blocks up to the maximium gate count of the array

#### • Extensive I/O cell options:

- User-configurable pad cells with predefined components

- 1 to mA per single I/O cell

- Custom configurations for I/O drive up to 96 mA

- Standard and slew rate limited available

- PCI 33 MHz compliant

- CMOS, TTL, LVCMOS, LVTTL, PCI (33MHz) levels

#### • Mixed voltage operation:

- Split power supply bussing between core and pads

- V core operation

- Mixed V and V I/O pads

- 5V input tolerance on 3.3V pads

- 5V output drive with 5.0V power pads

- Extensive packaging capabilities:

- QFPs, CQFPs, TQFPs, PLCCs, LCCs, JLCCs, PBGA, BGAs, PGAs, CPGAs, SOICs, TSOPs, PDIPs, PQZs, M-QUADs, individual die

- Burn-in capability as required

- Automatic Test Program Generation: Scan macros (NETSCAN™) for high fault coverage

- JTAG Boundary Scan macro support

- Full operating voltage range from 2.7V to 5.5V

- ESD protection > 2kV; latchup > 100 mA

- Power dissipation: 1.58µW/MHz/gate (FO=1; V<sub>DD</sub>=V)

2-3

#### MIXED VOLTAGE I/O MACROS FOR 5 VOLT TOLERANT AND 5 VOLT COMPATIBILITY

- Technology continues to drive down the maximum core and I/O operating voltages of ASICs. Since board level compatibility with the older interface standards continues to exist, ASICs must be able to provide a mixed voltage I/O solution on the same design. The two industry terms that describe these interface requirements are 5 volt tolerant and 5 volt capable. In the following explanations of mixed voltage I/O the two voltages used are 5V and 3.3V, however, the same explanations apply to any mixed voltage I/O application (i.e. 3.3V and 2.5V).

- 5 VOLT TOLERANT: When operating at 3.3V, special output pad cells are required to drive 3.3V levels and withstand 5V during input or tri-state mode. When receiving signals above 3.3V, these I/O cells must be used to prevent damage to the circuit or disruption of normal circuit operation. The TTL input portion of the I/O cell are programmed to achieve proper switching levels for either 5V or 3.3V inputs but not both. Maximum drive of these cells is less than non 5 volt tolerant macros in the library since many of the output devices in the pad are used to construct the 5 volt tolerant circuitry.

- 5 VOLT CAPABLE: 5 volt capable I/O requires the cell both accept and drive 5V signals. Separate power pins are required for each of the core and I/O voltages. One or more power pins are used for core and low voltage pad macros and additional power pins are used for high voltage pad macros. All core macros and low voltage pad macros are tied to the 3.3V supply. 5 volt capable pad macros must be used when receiving/driving signals above 3.3V. Each I/O cell has voltage level shifters to allow either 5V or 3.3V external signals to interface to the 3.3V core logic.

#### AMI500xxxx 0.5 micron CMOS Standard Cell

#### **Product Applications**

PLD OR FPGA CONVERSION: For high volume products, AMI Semiconductor's NETRANS® converts netlists from PLDs and FPGAs to more cost and performance effective AMI designs.

**2ND SOURCE FOR EXISTING PRODUCTS:** AMI Semiconductor's netlist conversion capabilities allow AMI to be a cost-effective, alternate supply for existing high volume products.

**PROCESS UPGRADE:** AMIS ASICs designed in 1.25μm, 1.0μm, 0.8μm, 0.6μm processes can be easily upgraded to the AMI family. The AMIS ASIC Library provides a common netlist design base.

ADDING CUSTOM BLOCKS: AMIS specializes in adding custom logic and simple analog functions to ASIC designs.

#### ASIC Design Tools and Methodology

AMIS ASICs are supported on many third party software platforms:

- Cadence®

- Mentor Graphics<sup>™</sup>

- Synopsys®

- Viewlogic®

- Veribest®

- Motive<sup>™</sup>

- Exemplar Leonardo<sup>™</sup>

- SDF back-annotation

- VHDL Vital simulation<sup>™</sup> (sign-off pending)

- Verilog® simulation (sign-off)

AMI Semiconductor's proprietary expert-system software, ACCESS Design Tools<sup>™</sup>, is an integrated suite of software tools for digital ASIC verification, FPGA migration, and ASIC second sourcing. ACCESS allows greatly shortened development spans, lower NRE, and increased first silicon success. AMI Semiconductor's software support methodology ensures a tight, wellcoupled design to the fabrication process. AMI Semiconductor's dedicated, experienced engineering staff can assist at any step in the design process.

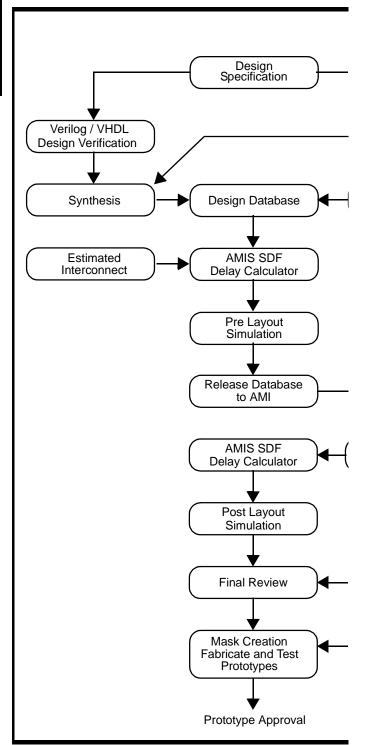

#### **ASIC Design Flow**

(See Figure 1: "ASIC Design Flow" on page 2-6) To help customers design their ASICs, AMIS supplies a design kit with a cell library containing symbols, simulation models, and software for design verification, timing calculation,

and netlist generation. Prelayout timing simulations use capacitance and resistance values derived from statistical averages of known layouts. After the actual layout is completed by AMIS, a post-layout interconnect capacitance and resistance table is supplied for final validation of device timing.

Working with an AMIS design center, customers capture and verify their designs using AMI Semiconductor'sAMI Semiconductor's ASIC Library. They also create test vectors for the logical part of their manufacturing test. AMIS provides automatic test program generation software, megacells, and netlist rule checkers to greatly speed up the design. A fault coverage check of the test vector set is an optional service.

A "Design Start Package" is completed by the customer and submitted to AMIS engineers for review. The Start Package contains the device specification, netlist, pin list, critical timing paths, and test vectors. The design is prescreened using AMI Semiconductor's ACCESS Design Tools and then resimulated on Verilog (AMI Semiconductor's sign-off simulators). The results are compared to the customer's simulation results.

Once the design has passed the initial screening, it is ready for layout. The layout begins by placing memory and megacells, assigning priority to critical paths, and designing the distribution and buffering of clocks. Layout is completed with automatic place-and-route on the balance of the circuit.

After layout is complete, the interconnect data is extracted from the physical layout and fed back to the sign-off simulator for final circuit verification. The post layout interconnect data is sent to the customer for final validation on their simulator. When the post-layout simulation is complete and approved by the customer, the design is released for mask and wafer fabrication.

The test program is developed in parallel with the design using automatic test program generation software. This allows prototypes to be tested before they are shipped.

AMIS uses Verilog/VHDL to speed ports between various software products.

#### AMI500xxxx 0.5 micron CMOS Standard Cell

#### Figure 1: ASIC Design Flow

#### AMI500xxxx 0.5 micron CMOS Standard Cell

#### The Design Library

AMI Semiconductor's design library provides a robust collection of building blocks for the AMI family. A broad range of primary cells is complemented with memory cell compilers and useful megafunctions. Custom cells are quickly designed by AMI Semiconductor's extensive, US-based design team.

#### The AMIS ASIC Library

The AMIS ASIC Library contains a rich set of core cells and configurable pad cells. The library is portable across all of AMI Semiconductor's gate array and standard cell families.

#### AMI's Innovative Pad-Piece Methodology

AMI Semiconductor's ASIC Library provides an innovative approach to I/O pad cell design. Thousands of different I/O cell configurations are possible by choosing from an array of input, output, and pullup/pulldown pad piece cells and making the appropriate schematic or HDL connections. In addition, AMIS conversion libraries can easily migrate netlist designs from older technologies that use ASIC Standard pad cells. AMI Semiconductor's ACCESS Design Tools software maps pad cells to their functional (fundamental), pad-piece blocks. Custom configurations are made by combining the pieces. Pad-piece design benefits AMIS customers by drastically reducing the need for workstation simulation models of I/O pad cells that do not yet exist. For detailed information of pad-piece usage, see the AMIS applications note *Pad Pieces* (4401035).

#### Memories

Customers supply cell specifications to AMI, and then receive simulation timing specifications overnight, and full simulation models for any AMIS supported software within five working days. See AMI Semiconductor's web page (www.amis.com) for more information.

#### Megacells

The AMIS gate array and standard cell families offer megacells for many popular functions, including: Core Processors, Peripherals, FIFOs, and Datapath (see Tables 3, 4, 5, and Table 6, "Peripherals," on page 2-9). AMIS core processors and peripherals duplicate the function of industry standard parts. Data path and FIFO megacells are developed using parameterized logic synthesizers. Most of AMI Semiconductor's megacells are "soft" or "firm" cores that are technology independent and can be customized for specific applications. Detailed functional information can be found in AMI Semiconductor's standard device data sheets.

#### **DC Specifications**

Table 1: Operating Specifications

| Р                              | Parameter                                                                   | Minimum             | Maximum             | Units |

|--------------------------------|-----------------------------------------------------------------------------|---------------------|---------------------|-------|

| V <sub>DD</sub> Supply Voltage |                                                                             | 2.7                 | 5.5                 | Volts |

| Ambient Temperature            | - Military                                                                  | -55                 | 125                 | °C    |

|                                | - Commercial                                                                | 0                   | 70                  | °C    |

| Junction Temperature           | - Military                                                                  | -55                 | 135                 | °C    |

|                                | - Commercial                                                                | 0                   | 85                  | °C    |

| CMOS Input Specificat          | tions (V <vdd<v; 0°c<t<70°c)<="" td=""><td></td><td></td><td></td></vdd<v;> |                     |                     |       |

| Vil                            | Low Level Input Voltage                                                     |                     | 0.3∗V <sub>DD</sub> | Volts |

| Vih                            | High Level Input Voltage                                                    | 0.7∗V <sub>DD</sub> |                     | Volts |

| lil                            | Low Level Input Current                                                     |                     | -1.0                | μΑ    |

| lih                            | High Level Input Current                                                    |                     | 1.0                 | μΑ    |

| lil                            | Input Pull-Up Current                                                       | -30                 | -110                | μΑ    |

| lih                            | Input Pull-Down Current                                                     | 30                  | 135                 | μA    |

| Vt-                            | Schmitt Negative Threshold                                                  | 0.2∗V <sub>DD</sub> |                     | Volts |

| Vt+                            | Schmitt Positive Threshold                                                  |                     | 0.8∗V <sub>DD</sub> | Volts |

| Vh                             | Schmitt Hysteresis                                                          | 1.0                 |                     | Volts |

| TTL Input Specificatio         | ns (V <vdd<v; 0°c<t<70°c)<="" td=""><td></td><td></td><td></td></vdd<v;>    |                     |                     |       |

| Vil                            | Low Level Input Voltage                                                     |                     | 0.8                 | Volts |

| Vih                            | High Level Input Voltage                                                    | 2.0                 |                     | Volts |

| lil                            | Low Level Input Current                                                     |                     | -1.0                | μA    |

| lih                            | High Level Input Current                                                    |                     | 1.0                 | μA    |

| lil                            | Input Pull-Up Current                                                       | -30                 | -110                | μΑ    |

| lih                            | Input Pull-Down Current                                                     | 30                  | 135                 | μA    |

| Vt-                            | Schmitt Negative Threshold                                                  | 0.7                 |                     | Volts |

| Vt+                            | Schmitt Positive Threshold                                                  |                     | 2.1                 | Volts |

| Vh                             | Schmitt Hysteresis                                                          | 0.4                 |                     | Volts |

| Driver <sup>1</sup> | Vol<br>Maximum | Voh<br>Minimum | lol<br>Maximum | loh<br>Maximum |

|---------------------|----------------|----------------|----------------|----------------|

| 1 mA Driver         | 0.4            | 2.4            | 1.0            | -1.0           |

| 2 mA Driver         | 0.4            | 2.4            | 2.0            | -2.0           |

| 4 mA Driver         | 0.4            | 2.4            | 4.0            | -4.0           |

| 8 mA Driver         | 0.4            | 2.4            | 8.0            | -8.0           |

| 16 mA Driver        | 0.4            | 2.4            | 16.0           | -16.0          |

#### Table 2: Output Operating Specifications $(V < VDD < V; 0^{\circ}C < T < 70^{\circ}C)$

1. See "DC Characteristics" on page 2-10 for specific output requirements.

Vol = Low Level Output Voltage given in Volts

Voh = High Level Output Voltage given in Volts

Iol = Low Level Output Current given in mA Ioh = High Level Output Current given in mA

#### Table 3: Absolute Maximum Ratings

AMI SEMICONDUCTOR

| Parameter                         | Minimum     | Maximum              | Units          |

|-----------------------------------|-------------|----------------------|----------------|

| V <sub>DD</sub> , Supply voltage  | -0.3        |                      | Volts          |

| Input pin voltage                 | -0.3        | V <sub>DD</sub> +0.3 | Volts          |

| Input pin current                 | -10.0       | 10.0                 | mA             |

| Storage temperature - Plastic pac | ckages -55  | 125                  | °C             |

| - Ceramic pa                      | ackages -65 | 150                  | °C             |

| Lead temperature                  |             | 300                  | °C for 10 sec. |

Note: The specifications indicate levels where permanent damage to the device may occur. Functional operation is not guaranteed under these conditions. Operation at absolute maximum conditions for extended periods may adversely affect the long term reliability of the device.

#### **DC Characteristics**

$(V_{DD} = V, T = 25^{\circ}C, Typical Process)$

**N-Channel Output Driver**

**N-Channel Pull-Down Device**

**P-Channel Output Driver**

**P-Channel Pull-Up Device**

#### **DC Derating Information**

The DC Characteristics shown on page 2-10 can be derated to obtain values at other operating conditions using the formula:

$I_{DC} = (I_{DC}(typ) \cdot K_{PDC} \cdot K_{VDC} \cdot K_{TDC})$

where:  $I_{DC}(typ)$  is a value from the DC characteristic current curves on page 2-10;  $K_{PDC}$  is the DC process derating coefficient determined at the processing limits;  $K_{VDC}$  is the DC voltage derating coefficient; and  $K_{TDC}$  is the DC temperature derating coefficient. The N-channel driver has a different set of coefficients for  $K_{PDC}$  and  $K_{TDC}$  due to the ESD protection structures.

Table 4: DC Variations with Process (KPDC)

|                  | N-Ch | annel Output<br>(Vol = 0.4V) |      | N-Chan | nel Pull-Dowr<br>(Vol = 0.4V) |      | All P-C | hannel (Voh = | = 2.4V) |

|------------------|------|------------------------------|------|--------|-------------------------------|------|---------|---------------|---------|

| Process          | WCS  | TYP                          | WCP  | WCS    | TYP                           | WCP  | WCS     | TYP           | WCP     |

| K <sub>PDC</sub> | 0.62 | 1.00                         | 1.18 | 0.63   | 1.00                          | 1.19 | 0.74    | 1.00          | 1.27    |

#### Table 5: DC Variations with Voltage (K<sub>VDC</sub>)

|                  | All N-Channel (Vol = 0.4V) |      |      | All P-Channel (Voh = $2.4V$ ) |      |      |

|------------------|----------------------------|------|------|-------------------------------|------|------|

| V <sub>DD</sub>  | 4.5                        | 5.0  | 5.5  | 4.5                           | 5.0  | 5.5  |

| K <sub>VDC</sub> | 0.98                       | 1.00 | 1.01 | 0.80                          | 1.00 | 1.21 |

DC Variations with Temperature for the N-Channel Output Driver ( $K_{TDC}$ )

DC Variations with Temperature for all other N-Channel and P-Channel Devices

#### **Delay Derating Information**

The propagation delays listed in the data sheets are for typical temperature (25°C), typical supply voltage (V), and typical processing conditions. To calculate the delay at other conditions, use the following equation:

$$T_{pdx} = T_{pdx}(\text{typ}) \cdot K_P \cdot K_V \cdot K_T$$

where  $T_{pdx}(typ)$  is given in the data sheets;  $K_P$  is the process derating coefficient (determined at the processing limits);  $K_T$  is the temperature derating coefficient; and  $K_V$  is the supply voltage derating coefficient.

#### Delay Variations with Temperature (K<sub>T</sub>)

Delay varies linearly with temperature.  $K_{T_{r}}$  the temperature derating coefficient, is determined by the following formula and table of common operating point values:

| Temp  | K <sub>T</sub> |

|-------|----------------|

| -55°C | 0.79           |

| -25°C | 0.86           |

| 0°C   | 0.96           |

| 25°C  | 1.00           |

| 70°C  | 1.13           |

| 100°C | 1.22           |

| 125°C | 1.29           |

| Temp. Range    | K <sub>T</sub> Formula               |

|----------------|--------------------------------------|

| -55°C to 140°C | $K_{T} = 1.0 + (T_{J}-25)(2.756E-3)$ |

Where  $T_J$  is the temperature (in °C) at the silicon junction.

#### Delay Variations with Process (K<sub>P</sub>)

Delay variations with process are fixed constants determined at the limits of acceptable processing. Values for  $K_{P_{r}}$  the process derating coefficient, are shown below:

| Derating Coefficient | (K <sub>P</sub> ) Process Variation Point                  |

|----------------------|------------------------------------------------------------|

| 1.30                 | Delay increase due to "Worst Case Speed" (WCS) processing  |

| 1.00                 | Typical delay; Processing target                           |

| 0.70                 | Delay reduction due to "Worst Case Power" (WCP) processing |

#### Delay Variations with Voltage (K<sub>V</sub>)

Delay varies nonlinearly with voltage. Values of K<sub>V</sub> for common operating points are shown below, and a characteristic curve is shown at right.

| V <sub>DD</sub> | K <sub>V</sub> |

|-----------------|----------------|

| 2.7V            | 1.75           |

| 3.0V            | 1.54           |

| 3.3V            | 1.39           |

| 4.5V            | 1.07           |

| 5.0V            | 1.00           |

| 5.5V            | 0.95           |

#### **Description of Data Sheet Features**

#### AMI500xxxx 0.5 micron CMOS Standard Cell

CELL NAME: AMI Semiconductor's cell name.

LIBRARY TYPE: Designates the minimum transistor gate length and library type, such as standard cell or gate array.

**DESCRIPTION:** Describes the function of the cell.

**LOGIC SYMBOL:** Shows a picture of the symbol as it appears in the workstation design kits.

**TRUTH TABLE:** A boolean table showing the output logic levels as a function of the input logic levels.

Types of logic levels found in the logic tables are as follows:

- н = High level steady state.

- L = Low level steady state,

- ↑ = Transition from low level to high level,

- $\downarrow$ = Transition from high level to low level,

- Х = Any level including transitions.

- NC = No change in output level for a given set of input levels,

- IL = The output level is unknown for this set of illegal input levels,

- Ζ = High impedance level,

- UN = Un-driven node or input,

- Q(n) = The level of Q before an active transition on the affecting node, and

- QN(n) = The level of QN before an active transition on the affecting node.

EQUIVALENT GATES: The cell area normalized to the area of the NA21, 2-input NAND gate.

HDL SYNTAX: Verilog and VHDL instantiation syntax.

EQUIVALENT LOAD: An equivalent load is defined as the capacitive pin load of an NA21 cell "A" pin. It is equal to 30.9 fF. In the propagation delay tables 13 fF of interconnect capacitance is added to each equivalent load. For a more accurate estimation of interconnect capacitance see Table 6, "Interconnect Load Estimation," on page 2-15.

PIN LOADING: A table of cell input loads in units of equivalent loads (the input load normalized to the input load of an NA21, 2-input NAND gate).

**POWER CHARACTERISTICS:** Power for the cell can be described in three parts, as shown by the three terms in the Power Equation for Core Cells and Input Buffers below. First, the power dissipated due to Static IDD across the channels and through the formed diodes. Second, the power due to the switching voltage across loads on the internal nodes of the cell. Third, the power due to the switching voltage across a load that a cell is driving.

The power characteristics table provides Static IDD for a junction temperature of 85°C, and the dissipative load for all the switching nodes in the cell in terms of equivalent loads. The load that a cell drives is calculated by adding up input loads. and then adding the estimated load from the Load Estimation table on page 2-15. Below are equations for calculating the power dissipation:

Core Cells and Input Buffers

POWER = (Static I<sub>DD</sub>) V<sub>DD</sub> + (30.9fF)EQL<sub>pd</sub>V<sub>DD</sub><sup>2</sup>f + (30.9fF)EQL<sub>I</sub>V<sub>DD</sub><sup>2</sup>f

Output Buffers

POWER = (Static I<sub>DD</sub>) V<sub>DD</sub> + (30.9fF)EQL<sub>pd</sub>V<sub>DD</sub><sup>2</sup>f + C<sub>ol</sub>V<sub>DD</sub><sup>2</sup>f

where:

Static I<sub>DD</sub> = Static leakage current of the cell

= Operating voltage VDD

EQLpd = Load of the switching nodes in the cell

f = Frequency of operation

= Load in farads on the output buffer

Col EQL = Load of the driven interconnect and driven input pins

#### **Description of Data Sheet Features** (continued):

The frequency term of the power equation dominates, making the static current term insignificant, except to give the standby current.

Three types of buffers (input, output, and bidirectional) may be assembled using pad piece cells. Calculating power characteristics for pad pieces is dependent on the buffer type. The power dissipated by a buffer is the cumulative power dissipated by its component pad pieces.

- ID pieces use the input buffer equation. (The input and output buffer equations are described on the previous page).

- Output pieces use the output buffer equation. C<sub>OL</sub> does not include any PADM pin loading of ID or PL pad piece cells that may be connected to the OD piece.

- PL pieces use the output buffer equation. C<sub>OL</sub> does not include any PADM pin loading of ID or OD pad piece cells that may be connected to the PL piece.

**PROPAGATION DELAYS :** The Propagation Delays table in a data sheet contains timing data for the various input to output paths in the cell. The path for the delay is identified by two pins. Delay values are given for each path's propagation delay or timing parameters corresponding to each of the five equivalent loads. The equivalent loads are given over the range of allowed loading for the cell, up to the maximum load the cell can drive. The output buffer loading is in picofarads. To find the delay for a cell, add up the loads of all the inputs that the cell is driving, then add the estimated interconnect load from the Load Estimation table on page 2-15. Finally, look up the value for the desired timing parameter corresponding to the load on the cell. Interpolate to find values in between load columns.

The Delay Characteristics table in a data sheet may contain the following propagation delays and timing parameters:

- t<sub>PLH</sub> = Input to output propagation delay for a rising edge on the output

- t<sub>PHL</sub> = Input to output propagation delay for a falling edge on the output

- $t_{ZH}$  = High impedance to high level delay

- t<sub>ZL</sub> = High impedance to low level delay

- t<sub>HZ</sub> = High level to high impedance delay

- t<sub>LZ</sub> = Low level to high impedance delay

- t<sub>su</sub> = Input setup time with respect to clock

- t<sub>h</sub> = Input hold time

- t<sub>w</sub> = Input pulse width

AMIS models the effects of input slew, and output resistive and capacitive loading for a particular cell's path delay. The delay in the data sheets represents a typical load on the inputs of the cell. Due to differing capabilities of logic simulators, the delay modeling method varies and may still be a linear model. Loads beyond the maximum load are an extrapolation of the model, and their accuracy is not guaranteed. More accurate delays can be determined using an AMIS workstation kit. Contact your sales representative or the factory about modeling for specific workstation kits and simulators.

#### AMI500xxxx 0.5 micron CMOS Standard Cell

#### Interconnect estimation

AMI SEMICONDUCTOR

For pre layout simulation, AMIS provides an estimated interconnect value based on statistical data. Table 12 provides data points from those non-linear equations to enable the designer to estimate timing based on data book information.

|     |     | Fan Out (Equivalent Loads) |     |     |      |      |      |      |

|-----|-----|----------------------------|-----|-----|------|------|------|------|

|     | 1   | 3                          | 6   | 9   | 12   | 20   | 35   | 50   |

| 100 | 0.3 | 1.2                        | 2.3 | 3.4 | 4.5  | 7.2  | 11.9 | 16.4 |

| 125 | 0.4 | 1.3                        | 2.6 | 3.8 | 5.0  | 8.0  | 13.2 | 18.1 |

| 150 | 0.4 | 1.4                        | 2.8 | 4.2 | 5.4  | 8.6  | 14.3 | 19.6 |

| 175 | 0.4 | 1.6                        | 3.1 | 4.5 | 5.8  | 9.3  | 15.3 | 21.0 |

| 200 | 0.5 | 1.7                        | 3.3 | 4.8 | 6.2  | 9.8  | 16.3 | 22.3 |

| 225 | 0.5 | 1.8                        | 3.4 | 5.0 | 6.5  | 10.4 | 17.1 | 23.5 |

| 250 | 0.6 | 1.9                        | 3.6 | 5.3 | 6.9  | 10.9 | 18.0 | 24.7 |

| 300 | 0.6 | 2.0                        | 3.9 | 5.7 | 7.5  | 11.8 | 19.5 | 26.8 |

| 350 | 0.7 | 2.2                        | 4.2 | 6.2 | 8.0  | 12.7 | 20.9 | 28.7 |

| 400 | 0.7 | 2.3                        | 4.5 | 6.5 | 8.5  | 13.4 | 22.2 | 30.4 |

| 450 | 0.8 | 2.5                        | 4.8 | 6.9 | 9.0  | 14.2 | 23.3 | 32.0 |

| 500 | 0.8 | 2.6                        | 5.0 | 7.2 | 9.4  | 14.9 | 24.5 | 33.6 |

| 550 | 0.9 | 2.7                        | 5.2 | 7.6 | 9.8  | 15.5 | 25.5 | 35.0 |

| 600 | 0.9 | 2.8                        | 5.4 | 7.9 | 10.2 | 16.1 | 26.5 | 36.4 |

| 650 | 1.0 | 3.0                        | 5.6 | 8.2 | 10.6 | 16.7 | 27.5 | 37.7 |

#### **Table 6: Interconnect Load Estimation**

The equivalent loads that are provided in the propagation delay tables within the data sheets include 13 fF of interconnect capacitance for each equivalent load. Table 6 was created from a non-linear statistical model and provides a more accurate representation of estimated interconnect for the various die sizes, base arrays and fanout. To compute equivalent loads driven by a given cell use the following formula:

total\_eq\_loads =  $\Sigma$  fanout loads (from pin loading tables) + estimated interconnect value (table 6)

The equivalent loads in the propagation delay tables need to be scaled by multiplying each equivalent load by 1.42.

#### Packaging

A variety of popular packages is available for the AMIS gate array and standard cell families.

For information on special packages or packaging requirements, contact an AMIS sales representative.

#### Table 7: Package Offering

| Package Type                          | Pin Count                                                                               |

|---------------------------------------|-----------------------------------------------------------------------------------------|

| Plastic Quad Flatpack, PQFP           | 44, 52, 64, 80, 100, 120, 128, 144, 160, 184, 208, 240, 256, 304                        |

| Low/Thin Quad Flatpack, LTQFP         | 32, 44, 48, 64, 80, 100, 120, 128, 144, 160, 176, 208                                   |

| Metal Quad Flatpack, MQUAD®           | 128, 144, 208                                                                           |

| Power Quad 2, PQ2                     | 128, 144, 160, 208, 304                                                                 |

| Ceramic Quad Flatpack, CQFP           | 40, 44, 52, 64, 84, 100, 132, 144, 172, 196, 256, 352                                   |

| Plastic Leaded Chip Carrier, PLCC     | 20, 28, 32, 44, 52, 68, 84                                                              |

| Ceramic Leaded Chip Carrier,<br>JLDCC | 28, 44, 52, 68, 84                                                                      |

| Ceramic Pin Grid Array, CPGA          | 65, 68, 69, 84, 85, 101, 109, 121, 132, 145, 155, 177, 181, 208, 225, 257, 299, 476     |

| Ball Grid Array, BGA                  | 121, 169, 208, 225, 256, 313, 316, 352, 388,420, 432, 456, 484, 560, 676, 680, 728, 900 |

| Low Profile Fine Pitch BGA, LFBGA     | 36, 40, 56, 64, 81, 84,100, 108, 128, 144, 160, 176, 208, 256                           |

#### **ON-LINE APPLICATION NOTES**

AMIS provides a collection of application notes to aid the engineer in the design of gate array and standard cell Application Specific Integrated Circuits (ASICs). Each of the topics found on AMI Semiconductor's web site http:// www.amis.com/tech\_library provides supplemental information to those found in this book in addition to other very useful guidelines and helps. Some of the subjects currently available are Boundary Scan, internal scan, clocking schemes, crystal oscillators usage, guidelines for supplying test vector simulation, using megacells and memories, sequential device metastability, on-chip pull-up/pull-down resistors, using pad pieces, power estimation, Programmable Phase Locked Loop (PLL), standard test philosophy, synchronous design, thermal resistance of packages, using nand tree circuits for Input parametric testing, and VHDL based design methodology. This site will be continually updated with useful information to assist the designer.

## SECTION 3 CORE LOGIC

# This process has multiple cores libraries available. Select the appropriate library that will meet your specific design requirements. The core libraries can be found at @ http://www.amis.com/tech\_info.

|            | AMIS Fab Process | Separate Substrate | Core Voltages | Core Cells | Density (gates/mm <sup>2</sup> ) | Power (uW/MHz/gate) @ 5.0V | Power (uW/MHz/gate) @ 3.3V | Power (uW/MHz/gate) @ 2.5V | Speed NA22 => 1 fo-0mm | Speed NA22 => 2 fo-0mm | Speed NA22 => 2 fo-2mm | Toggle Rate (MHz) |

|------------|------------------|--------------------|---------------|------------|----------------------------------|----------------------------|----------------------------|----------------------------|------------------------|------------------------|------------------------|-------------------|

| AMI500HXSC | C5               | Ν                  | 5.0/3.3       | 349        | 7.35K                            | 1.58                       | 0.69                       | NA                         | 82                     | 103                    | 218                    | 590               |

| AMI500SXSC | C5               | Y                  | 5.0/3.3       | 332        | 6.92K                            | 1.58                       | 0.69                       | NA                         | 82                     | 103                    | 218                    | 590               |

| AMI500MXSC | C5               | Y                  | 5.0/3.3/2.5   | 332        | 14.4K                            | 0.63                       | 0.28                       | 0.16                       | 101                    | 128                    | 561                    | 440               |

| Notes      |                  |                    | (1)           |            | (2)                              | (3)                        | (4)                        | (5)                        | (6)                    | (6)                    | (6)                    | (7)               |

Notes:

1) Voltage for which the library has been characterized

2) These numbers are for comparison purposes only and indicate the raw (unrouted) densities. Routing density varies with number of routing layers, library cells, and total gates. Consult factory for more information.

3) Power numbers for library characterized at the first core voltage listed

4) Power numbers for library characterized at the second core voltage listed

5) Power numbers for library characterized at the third core voltage listed

6) All performance numbers are at typical first core voltage listed with typical temperature and process, result in pS

7) Toggle rates are first core voltage listed- 10%, worst case temperature of 135C, and WCS process corner

## SECTION 4 PAD LOGIC

# This process has multiple pad libraries available. Select the appropriate library that will meet your specific design requirements. The pad libraries can be found at @ http://www.amis.com/tech\_info

|            | AMIS Fab Process | Mixed Signal Enhancements | Min. Drawn Gate Length (um) | 5V I/O Tolerant | 5V I/O Capable | Mixed Voltage Ready | PCI 33MHz | Inline Pad Pitch (um) | Staggered Pad Pitch (um) | Pad Height (un/mil) | Max Output per Pad (mA) | Balanced Output per Pad (mA) | Pad Window Opening (um) | Pad Node Capacitance (pF) |

|------------|------------------|---------------------------|-----------------------------|-----------------|----------------|---------------------|-----------|-----------------------|--------------------------|---------------------|-------------------------|------------------------------|-------------------------|---------------------------|

| AMI500HXPR | C5               | Ν                         | 0.6                         | Ν               | Y              | Y                   | Y         | 86                    | 60                       | 718/82.3            | 24                      | 16                           | 74                      | 4.9                       |

| AMI500HXPS | C5               | Ν                         | 0.6                         | Ν               | Y              | Y                   | Ν         | 86                    | 60                       | 558/22.0            | 12                      | 10                           | 74                      | 4.9                       |

| AMI500XHPF | C5               | Y                         | 0.6                         | Ν               | Y              | Y                   | Ν         | 135                   | NA                       | 388/15.3            | 12                      | 12                           | 74                      | 5.8                       |

| AMI500HXPM | C5               | Y                         | 0.6                         | Ν               | Y              | Y                   | Ν         | 86                    | NA                       | 567/22.3            | 12                      | 10                           | 74                      | 4.9                       |

# **SECTION 5** Megacell Please refer to application notes which have either been included on the CD with this databook or at AMIS website <a href="http://www.amis.com/tech\_info">http://www.amis.com/tech\_info</a> for megacells available.

## **Selection Guide**

#### **Memories Selection Guide**

| SRAM High Speed Low-Power Single Port.         | 6-1  |

|------------------------------------------------|------|

| DPRAM_1R1W High speed Low-Power dual Port RAM. | 6-16 |

| DPRAM_2RW High Speed Low-Power Dual Port RAM.  | 6-30 |

| High Speed ROM.                                |      |

| Sync-Wrap.                                     | 6-49 |

| Memory Bist                                    | 6-50 |

#### **CMOS ASIC Standard Cell Memories**

#### Features

- 6-T memory cell design

- Simple combinational logic decoding

- Small bitline differential in read mode eliminates precharge delay

- Fast ATD circuit turns on wordlines and sense amps only as needed to save power while allowing asynchronous operation

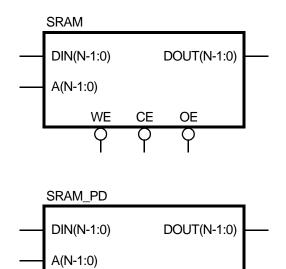

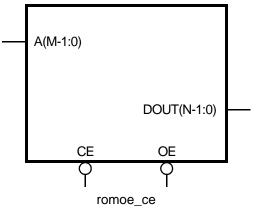

#### Logic Symbol

PD

φ

WE

Q

### SRAM: High Speed Low-Power Single Port Description

AMI Semiconductor's high speed, low power CMOS RAM is available in both single and dual port versions. Column select passgates provide a cascode gain stage, followed by a differential voltage sense amp. The memory array columns may be multiplexed to optimize the aspect ratio. Multiplexing of columns, or column folding, shortens the bitline length (reduces the number of rows in the array) while increasing the width of the memory array. No change in the total memory bit count occurs.

The zero\_out option sets all outputs to to 'zero'. This operation is controlled by the PD signal.

The RAM draws current only in response to changing inputs, minimizing power consumption and allowing complete IDDQ testing. In addition to normal CMOS transient current, address changes activate the sense amps and one row of memory cells for a period of time longer than access time. The current drawn by each sense amp is comparable to the read current of each memory cell.b

### **Signal Summary**

|            | INPUTS                                                                                            | OUTPUTS    |             |  |

|------------|---------------------------------------------------------------------------------------------------|------------|-------------|--|

| PORT LABEL | FUNCTION                                                                                          | PORT LABEL | FUNCTION    |  |

| A          | Address                                                                                           | DOUT       | Output Data |  |

| DIN        | Input Data                                                                                        |            |             |  |

| CE         | Chip Enable, avtive low                                                                           |            |             |  |

| WE         | Write Enable, active low                                                                          |            |             |  |

| OE         | Output Enable, active low, tristated output control                                               |            |             |  |

| PD         | Power Down, active high, read and write cycles disabled and output driven to zero (0) when active |            |             |  |

#### **Parameters**

| NAME        | DEFINITION                 | DATA TYPE | VALUES          |

|-------------|----------------------------|-----------|-----------------|

| Ν           | bits per word              | Integer   | 1 -144          |

| WORDS       | number of words            | Integer   | 8 -16384        |

| М           | address size               | Integer   | 3 - 14          |

| BPC         | bits per column            | Integer   | 2, 4, 8, 16, 32 |

| FLOORPLAN   | auto floorplan             | Integer   | 0, 1            |

| BUFFER_SIZE | buffer size                | String    | 1-6             |

| FREQUENCY   | frequency in MHz           | Integer   | 1-100           |

| VDROP       | voltage drop in millivolts | Integer   | 1-249           |

Block height range is 4-512; block width range is 4-288; max total bits is 144K (16K x 9).

### **Bits Per Column (BPC) Options**

| BPC VALUE | MINIMUM WORDS | MAXIMUM WORDS | ADDRESS<br>INCREMENT | MINIMUM BITS | MAXIMUM BITS |

|-----------|---------------|---------------|----------------------|--------------|--------------|

| 2         | 8             | 1024          | 4                    | 1            | 144          |

| 4         | 16            | 2048          | 8                    | 1            | 72           |

| 8         | 32            | 4096          | 16                   | 1            | 36           |

| 16        | 64            | 8192          | 32                   | 1            | 18           |

| 32        | 128           | 16384         | 64                   | 1            | 9            |

Memories

#### Parts

| PART NAME | PINS                     |

|-----------|--------------------------|

| sram      | A, CE, DIN, OE, WE, DOUT |

| sram_pd   | A, DIN, PD, WE, DOUT     |

#### Truth Table

#### zero-out option false

|     |    | INPUTS |     |    | OUTPUTS | COMMENT                                   |  |  |

|-----|----|--------|-----|----|---------|-------------------------------------------|--|--|

| Α   | CE | OE     | DIN | WE | DOUT    | COMMENT                                   |  |  |

| 0/1 | 0  | 0      | Х   | 1  | Data    | Read                                      |  |  |

| Х   | 0  | 1      | Х   | 1  | Z       | Output Disabled (standard) - RAM Active   |  |  |

| Х   | 1  | 1      | Х   | Х  | Z       | Output Disabled (standard) - RAM Disabled |  |  |

| Х   | 1  | 0      | Х   | Х  | Data    | Output Stable, RAM disabled               |  |  |

| 0/1 | 0  | 0      | 0/1 | 0  | Data    | Write with Write-Through                  |  |  |

| 0/1 | 0  | 1      | 0/1 | 0  | Z       | Write                                     |  |  |

#### zero-out option true

|     | INPU | ITS |    | OUTPUTS | COMMENT                                  |

|-----|------|-----|----|---------|------------------------------------------|

| Α   | PD   | DIN | WE | DOUT    | COMMENT                                  |

| Х   | 1    | Х   | Х  | 0       | Output Disabled (zero_out), RAM disabled |

| 0/1 | 0    | Х   | 1  | Data    | Read                                     |

| 0/1 | 0    | 0/1 | 0  | Data    | Write with Write-Through                 |

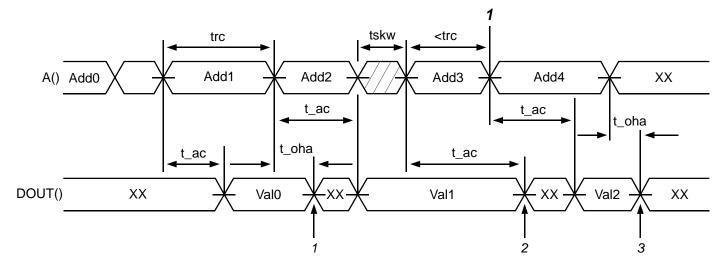

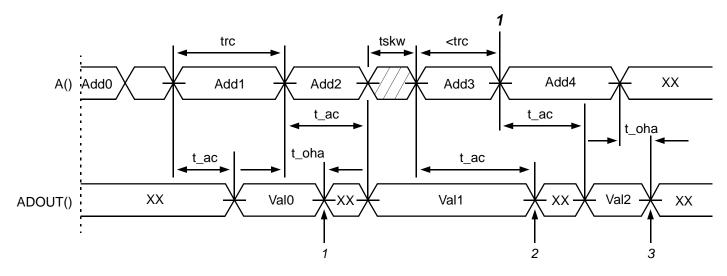

### SWITCHING TIME WAVEFORMS

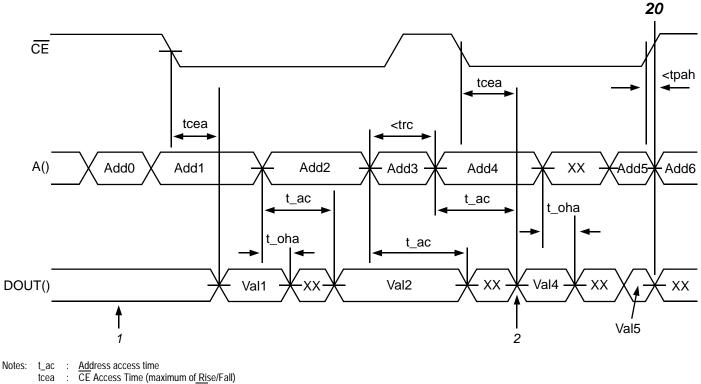

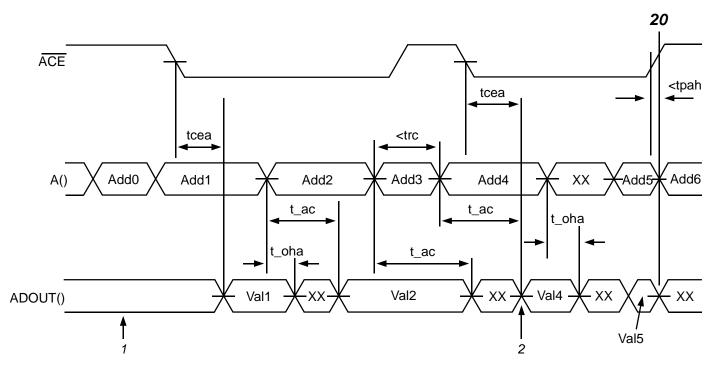

#### Single Port RAM Read Cycle 1

sram :CE = '0', OE = '0', WE = '1' sram\_pd:PD='0', WE='1'

Notes: t\_ac : Address Access Time (maximum of Rise/Fall)

trc : Read Cycle Time

t\_oha : Output Hold Time from Address Change (minimum of Rise/Fall)

tskw : All addresses must complete transition within this time

1. t\_oha delay will only be applied to the last data accessed, otherwise, t\_ac will be used for the pin-to-pin delay.

2. trc <= t\_ac. If Add3 width is less than trc, DOUT() goes to 'X'.

3. If A() becomes 'X', DOUT() goes 'X' after time t\_oha.

1. Error: Illegal Address input: Address cycle time is smaller than minimum trc.

## SRAM High Speed Low-Power Single Port

## **CMOS ASIC Standard Cell Memories**

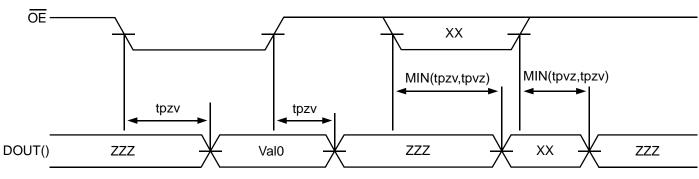

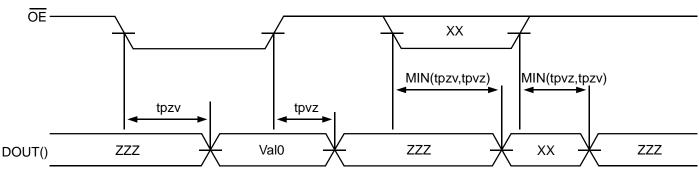

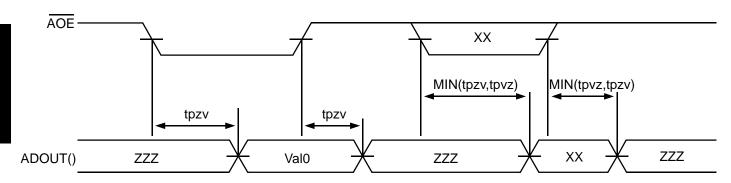

#### Single Port RAM Read Cycle 2

sram: CE = '0', WE = '1'

Notes:

tpvz

:

Delay to propagate valid DOUT() to high impedance to valid DOUT()

tpzv

:

Delay to propagate high impedance to valid DOUT()

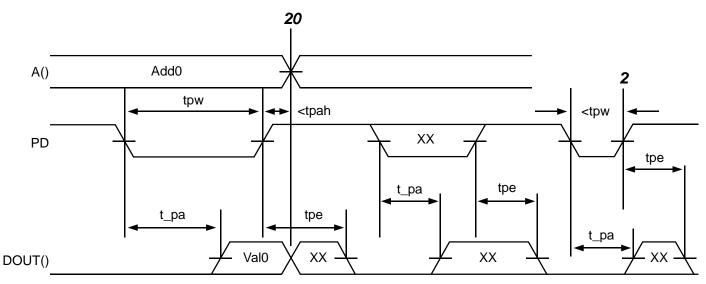

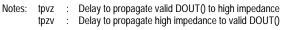

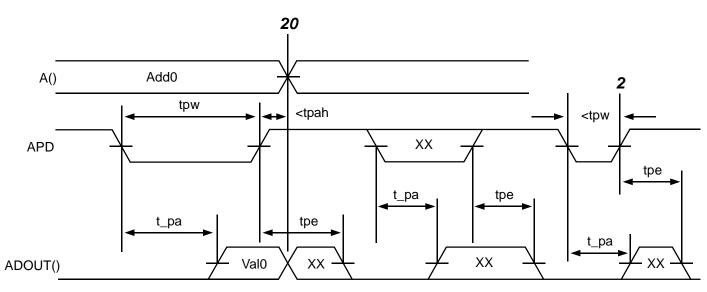

#### Single Port RAM Read Cycle 3

sram\_pd: WE = '1'

Notes: t\_pa : Access time from PD

- tpe : PD shutting off to DOUT() Fall

- tpw : Minimum pulse width for PD

- tpah : Address hold time from PD rising

2. Error: Illegal PD input: PD "Low" width time smaller than min. tpw. 20. Error: Illegal address input: hold time to PD is smaller than min. tpah.

#### Single Port RAM Read Cycle 4

sram: OE = '0', WE = '1'

Address hold time from PD or  $\overline{CE}$  rising tpah

trc

Min. ready cycle time

t\_oha : Output hold time from address change (minimum of Rise/Fall)

Normal DOUT() change due to address change is locked out by <u>CE' pin set to '1'.</u>

Output becomes valid after the MAX of t\_ac or tcea. Note that the 'CE' pin rising does not trigger a RAM access.

20. Error: Illegal address input: hold time to  $\overline{CE}/PD$  is smaller than min. tpah.

## **SRAM High Speed Low-Power Single Port**

## **CMOS ASIC Standard Cell Memories**

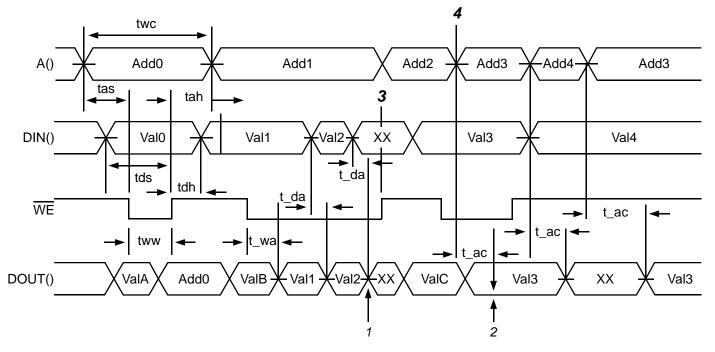

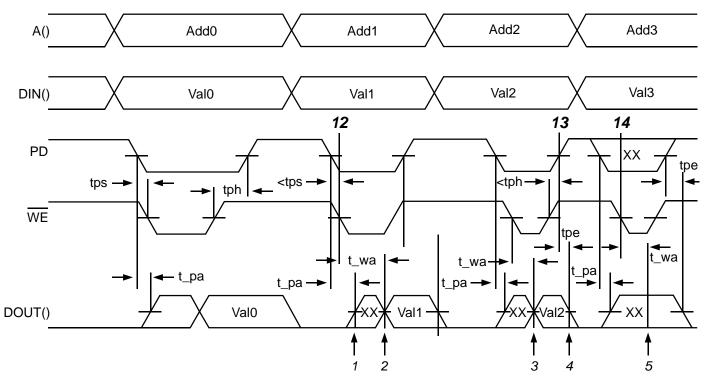

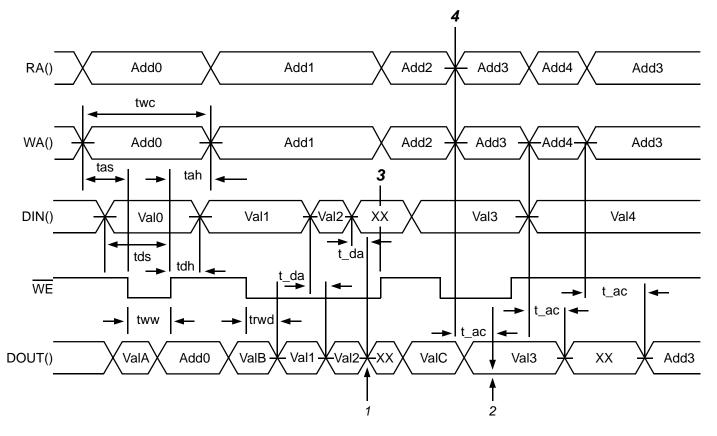

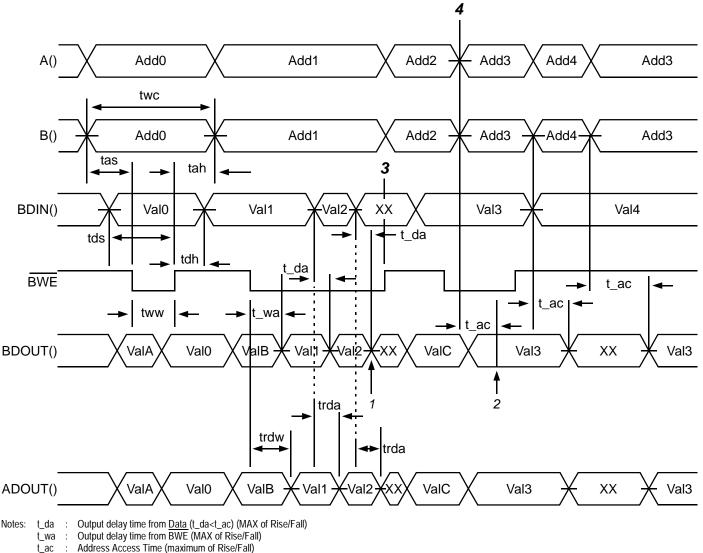

#### Single Port RAM Write Cycle 1

sram : CE = '0', OE = '0' sram\_pd : PD = '0'

Notes:

Output delay time from  $\underline{Dat}a$  (t\_da < t\_ac) (MAX of Rise/Fall) Output delay time from WE (MAX of Rise/Fall) t\_da :

- t\_wa

- Address access time t\_ac

- Address setup time tas :

- Address hold time tah

- tds Data setup time

- tdh Data hold time

- Write pulse width low tww

- twc Write cycle time

VaIA, VaIB, and VaIC are previously retained in address Add0, Add1, and Add2

1. Data retained in Add1 is overwritten by 'X' at this time.

2. Data retained in all words is overwritten by 'X' at this time. Writing Val3 into Add3 should be successful.

3. Error: Illegal Operation: Data "X" is written at rising edge of WE

4. Error: Illegal Operation: Address was changed while WE low

#### Single Port RAM Write Cycle 2

sram : CE = '0', OE = '0' sram\_pd : PD = '0'

Notes: t\_da : Output delay time from Data (t\_da < t\_ac) (MAX of Rise/Fall)

- Output delay time from WE (MAX of Rise/Fall) t\_wa :

- t\_ac Address access time

- Address hold time tah

- tds Data setup time

- tdh Data hold time

- tas Address setup time

ValA-ValF are previously retained in Add5-Add4.

1. Data retained in all words is overwritten by 'X' at this time. Writing Val0 into Add0 should be successful.

2. Data retained by all words is overwritten by 'X' at this time.

3. Data retained in Add3 is overwritten by 'X' at this time.

4. Data retained in Add4 is overwritten by 'X' at this time.

5. Error: Illegal Address Input: Address setup time to  $\overline{\text{WE}}$  is smaller than Min tas.

6. Error: Illegal Address Input: Address hold time to WE is smaller than Min tah.

Error: Illegal Data Input: DIN setup time to WE is smaller than Min tds.

Error: Illegal Data Input: DIN hold time to WE is smaller than Min tdh.

# SRAM High Speed Low-Power Single Port

## **CMOS ASIC Standard Cell Memories**

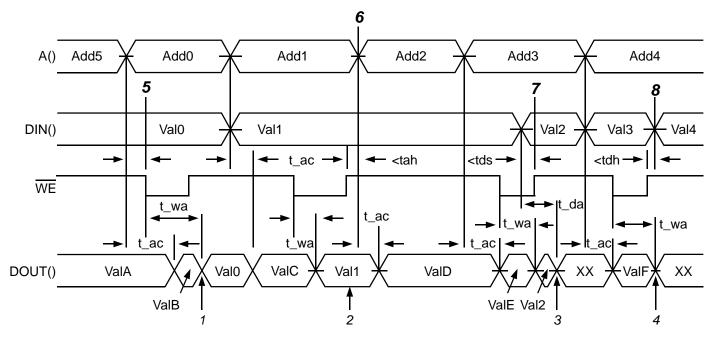

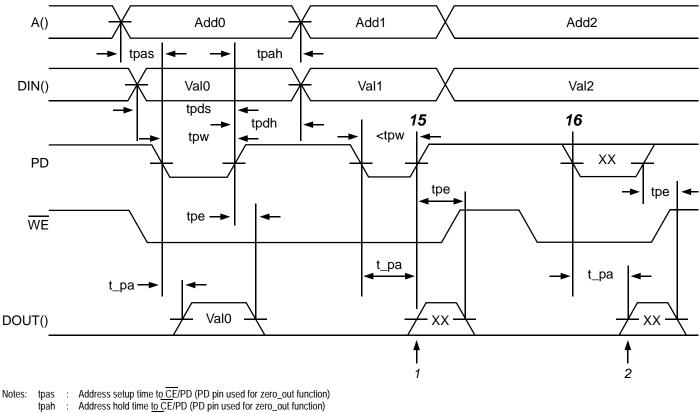

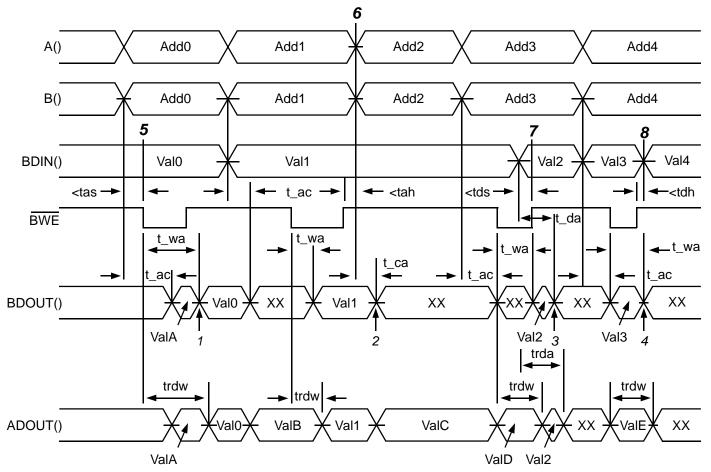

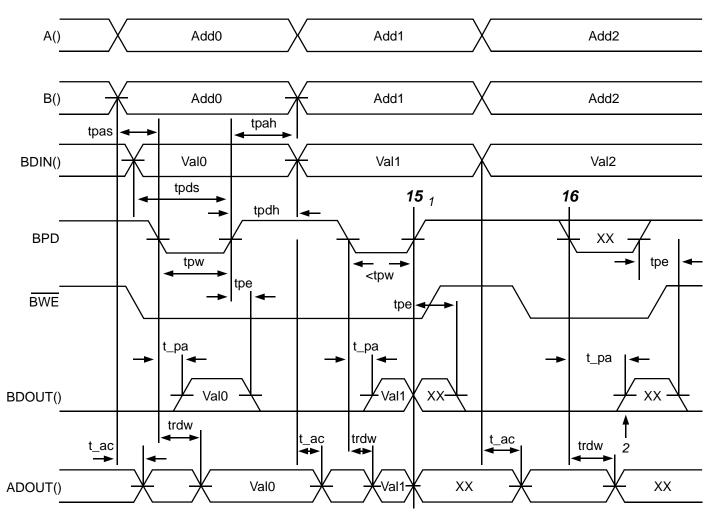

#### Single Port RAM Write Cycle 3

sram : CE = '0', OE = '0' sram\_pd : PD = '0'

- Notes: t\_wa : Ouput delay time from WE (MAX of Rise/Fall)

- t\_ac : Address access time

- tww : Write pulse width low

- 1. Data retained in Add0 is overwritten by 'X' at this time.

- 2. Data retained in Add1 is overwritten by 'X' at this time.

- 3. Data retained in Add2 is overwritten by 'X' at this time.

- 4. DOUT() becomes 'X' after t\_ac time from leading edge of address 'X'.

- 5. Data retained in all words is overwritten by 'X' after t\_wa time from falling edge of  $\overline{WE}$ .

- **3**. Error: Illegal <u>Operation: Data</u> "X" is written at rising edge of  $\overline{WE}$ .

- 9. Error: Illegal WE Input: WE "Low" width time is smaller than Min tww.

- 10. Error: Illegal Operation: WE input went to "X".

- 11. Error: Illegal Operation: Address was "X" at the falling edge of WE.

#### Single Port RAM Write Cycle 4 (sram\_pd)

$\label{eq:cell} \underline{CE} / \text{PD} \text{ setup time (PD pin used for zero_out function)} \\ \underline{CE} / \text{PD hold time (PD pin used for zero_out function)} \\ \\$ Notes: tps

tph

Output delay time from WE (MAX of Rise/Fall) t\_wa :

t\_pa

Access time from CE/PD CE/PD shutting off to DOUT() Fall tpe

1. 4. Data retained in all words is overwritten by 'X' at this time.

2. "X" retained in Add1 is overwritten by Val1 at this time.

3. "X" retained in Add2 is overwritten by Val2 at this time.

5. If Data retained in Add3 is not equal to Val3, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value.

Error: Illegal <u>CE</u>/PD Input: <u>CE</u>/PD setup time to <u>WE</u> is smaller than Min tps.

Error: Illegal CE/PD Input: <u>CE</u>/PD hold time to WE is smaller <u>than</u> Min tph.

14. Error: Illegal Operation: CE/PD was "X" at the falling edge of WE.

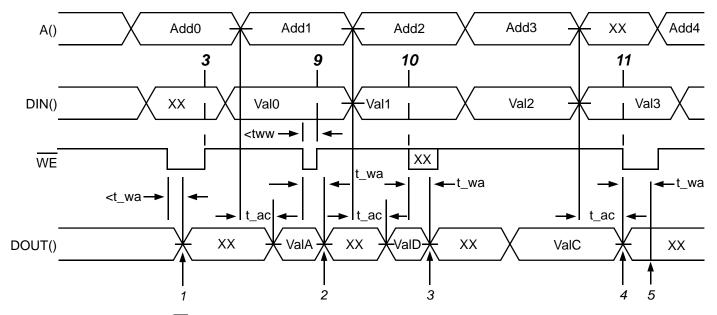

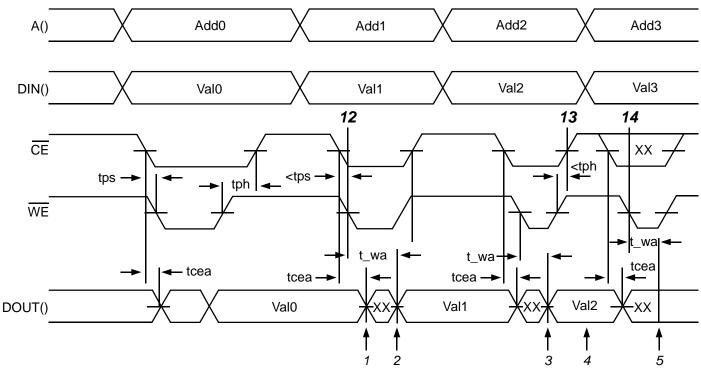

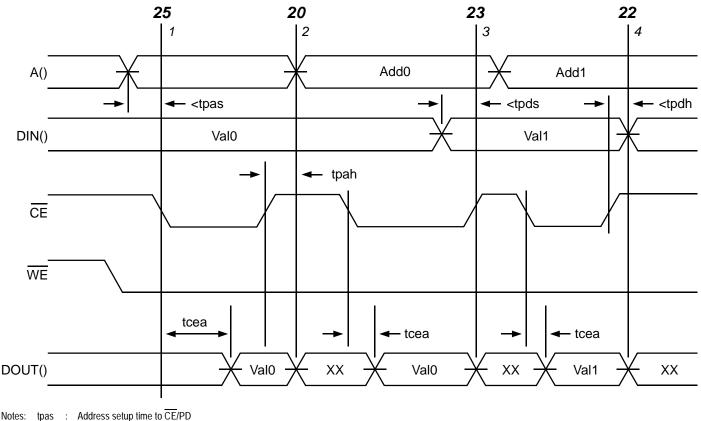

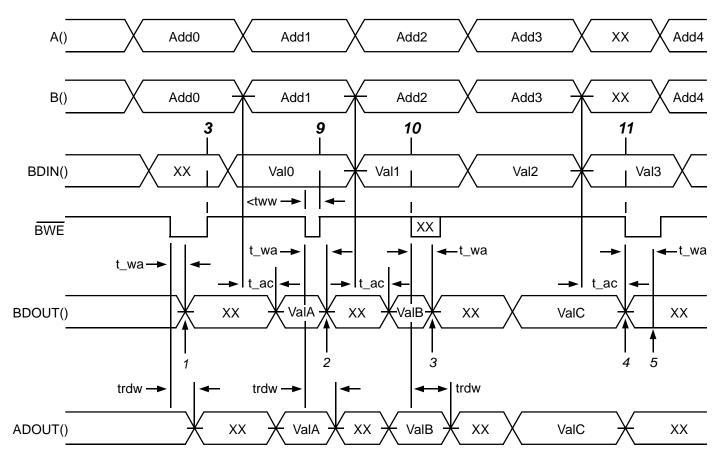

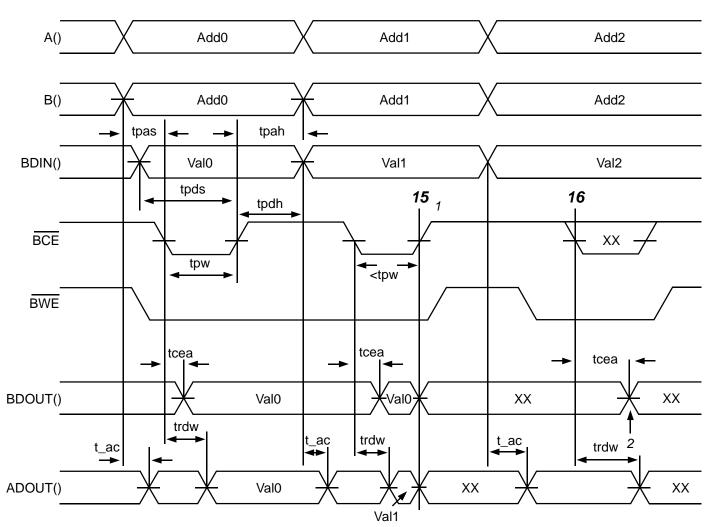

#### Single Port RAM Write Cycle 5

sram: OE = '0'

Notes: tps

- CE/PD setup time tph : CE/PD hold time

- Output delay time from  $\overline{\text{WE}}$  (MAX of Rise/Fall) Access time from  $\overline{\text{CE}}$ t\_wa

- : tcea

- 1. 4. Data retained in all words is overwritten by 'X' at this time.

- 2. "X" retained in Add1 is overwritten by Val1 at this time.

- 3. "X" retained in Add2 is overwritten by Val2 at this time.

- 5. If Data retained in Add3 is not equal to Val3, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value.

- **12**. Error: Illegal  $\overline{CE}$ /PD Input:  $\overline{CE}$ /PD setup time to  $\overline{WE}$  is smaller than Min tps. **13**. Error: Illegal CE/PD Inp<u>ut:</u> CE/PD hold time to WE is smaller <u>than</u> Min tph.

- 14. Error: Illegal Operation: CE/PD was "X" at the falling edge of WE.

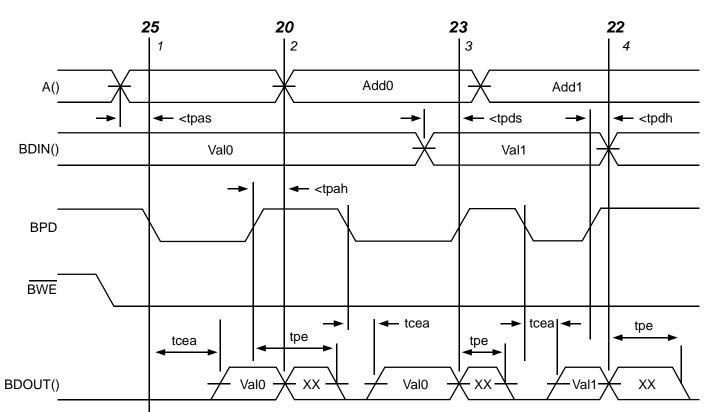

#### Single Port RAM Write Cycle 6 (sram\_pd)

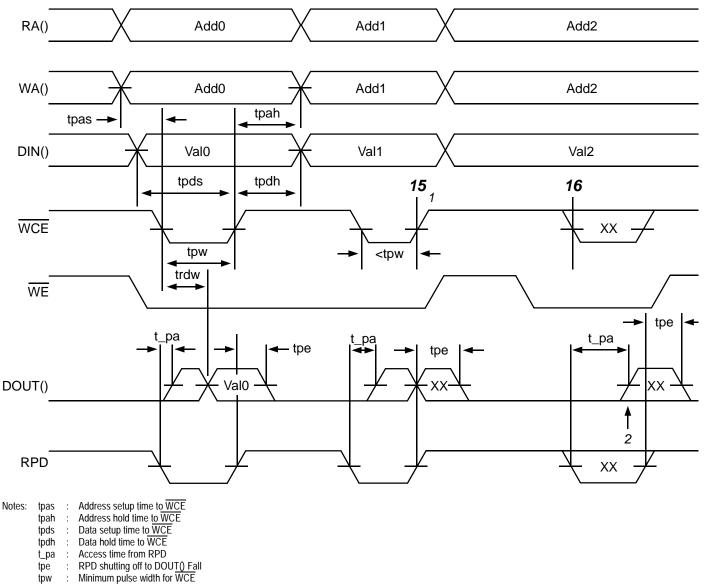

- tpah

- tpds Data setup time to CE/PD

- Data hold time to CE/PD tpdh

- Access time from CE/PD t\_pa

- PD shutting off to DOUT() Fall tpe

- Minimum pulse width for CE/PD tpw

1. If Data retained in Add1 is not equal to Val1, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value. 2. If Data retained in Add2 is not equal to Val2, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value.

15. Error: Illegal CE/PD input: CE/PD "Low" width time smaller than Min tpw.

16. Error: Illegal Operation: CE/PD went "X" while WE is "Low".

## **SRAM High Speed Low-Power Single Port**

## **CMOS ASIC Standard Cell Memories**

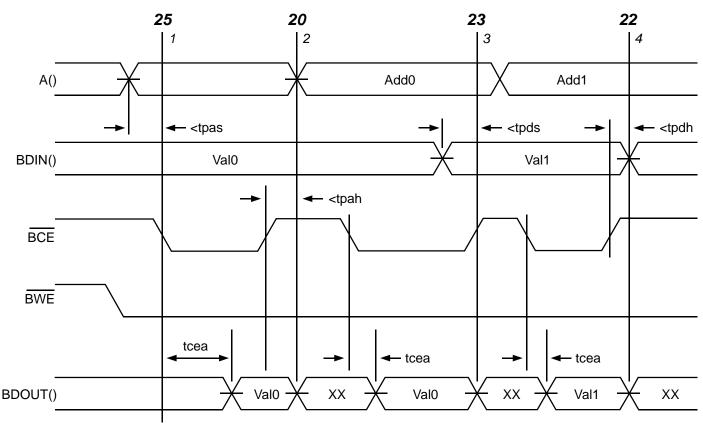

#### Single Port RAM Write Cycle 7 (sram)

- tpds Data setup time to CE/PD

- tpdh Data hold time to CE/PD

- Access time from  $\overline{CE}$ tcea

- PD shutting off to DOUT() Fall tpe

- Minimum pulse width from CE/PD tpw

1. If Data retained in Add1 is not equal to Val1, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value. 2. If Data retained in Add2 is not equal to Val2, retained data is overwritten by "X' at this time. If both are identical, retained data is not overwritten by any value.

15. Error: Illegal CE/PD input: CE/PD "Low" width time smaller than Min tpw.

16. Error: Illegal Operation: CE/PD went "X" while WE is "Low".

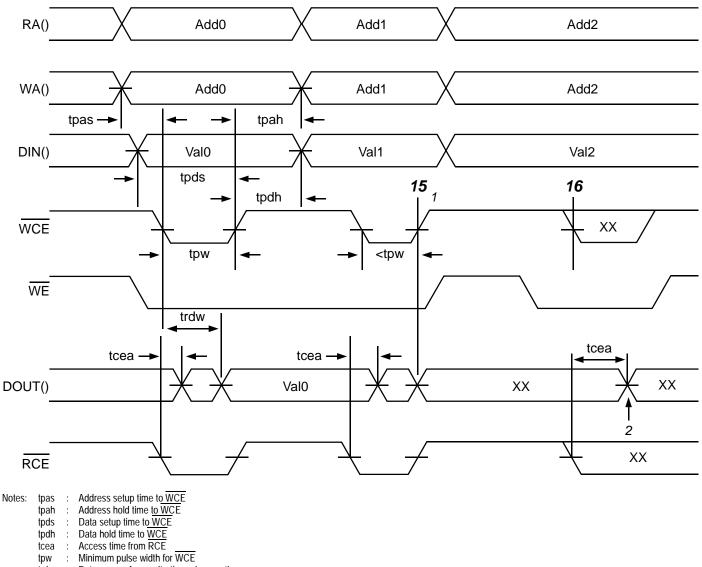

#### Single Port RAM Write Cycle 8 (sram)

Address setup time to CE/PD tpas

Address hold time to CE/PD Data setup time to CE/PD tpah

tpds :

tpdh Data setup time to CE/PD Access time from CE

tcea

1. If tpas is violated, data in all addresses is overwritten by "X" at this time.

2. If tpah is violated, data in all addresses is overwritten by "X" at this time.

3. If tpds is violated, data in Add0 is overwritten by "X" at this time.

4. If tpdh is violated, data in Add1 is overwritten by "X" at this time.

**20.** Error: Illegal address input: hold time to  $\overline{CE/PD}$  is smaller than min. tpah. 22. Error: Illegal data input: DIN hold time to CE/PD is smaller than min. tpdh. 23. Error: Illegal data input: DIN setup time to CE/PD is smaller than min. tpds. **25.** Error: Illegal address input: setup time to  $\overline{CE}/PD$  is smaller than min. tpas.

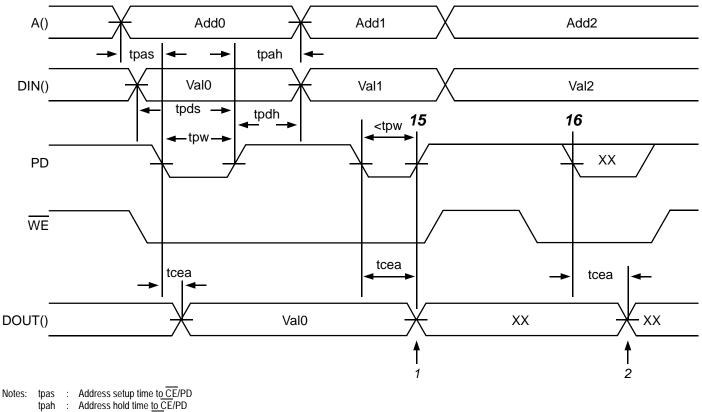

# **SRAM High Speed Low-Power Single Port**

## **CMOS ASIC Standard Cell Memories**

#### Single Port RAM Write Cycle 9 (sram\_pd)

Address setup time to CE/PD Notes: tpas :

Address hold time to CE/PD Data setup time to CE/PD tpah

tpds

tpdh Data hold time to CE/PD :

Access time from PD t\_pa :

PD shutting off to DOUT() Fall tpe

1. If tpas is violated, data in all addresses is overwritten by "X" at this time.

2. If tpah is violated, data in all addresses is overwritten by "X" at this time.

3. If tpds is violated, data in Add0 is overwritten by "X" at this time.

4. If tpdh is violated, data in Add1 is overwritten by "X" at this time.

**20**. Error: Illegal address input: hold time to  $\overline{CE}/PD$  is smaller than min. tpah.

22. Error: Illegal data input: DIN hold time to CE/PD is smaller than min. tpdh.

23. Error: Illegal data input: DIN setup time to CE/PD is smaller than min. tpds. 25. Error: Illegal address input: setup time to  $\overline{CE}/PD$  is smaller than min. tpas.

#### Features

- 8-T memory cell design

- Simple combinational logic decoding

- Small bitline differential in read mode eliminates precharge delay

- Fast ATD circuit turns on wordlines and sense amps only as needed to save power while allowing asynchronous operation

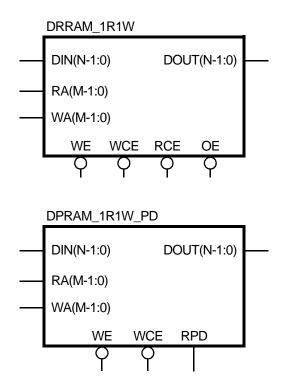

## Logic Symbol

## **CMOS ASIC Standard Cell Memories**

### DPRAM\_1R1W: High Speed Low-Power Dual Port Description

AMI Semiconductor's high speed, low power CMOS RAM is available in both single and dual port versions. Column select passgates provide a cascode gain stage, followed by a differential voltage sense amp. The memory array columns may be multiplexed to optimize the aspect ratio. Multiplexing of columns, or column folding, shortens the bitline length (reduces the number of rows in the array) while increasing the width of the memory array. No change in the total memory bit count occurs.

The zero\_out option sends the outputs all to "zero". This operation is controlled by the PD signal.

The RAM draws current only in response to changing inputs, minimizing power consumption and allowing complete IDDQ testing. Address changes activate the sense amps and one row of memory cells for a period of time longer than access time. The current drawn by each sense amp is comparable to the read current of each memory cell.

DPRAM\_1R1W High speed Low-Power dual Port RAM.

## **CMOS ASIC Standard Cell Memories**

### **Signal Summary**

|            | INPUTS                                                                                      | OUT        | PUTS        |

|------------|---------------------------------------------------------------------------------------------|------------|-------------|

| PORT LABLE | FUNCTION                                                                                    | PORT LABEL | FUNCTION    |

| RA         | Read Address                                                                                | DOUT       | Output Data |

| WA         | Write Address                                                                               |            |             |

| DIN        | Input Data                                                                                  |            |             |

| RCE        | Read Chip Enable, active low                                                                |            |             |

| WCE        | Write Chip Enable, active low                                                               |            |             |

| WE         | Write Enable, active low                                                                    |            |             |

| OE         | Output Enable, active low                                                                   |            |             |

| RPD        | Read Power Down, active high, read cycle disabled and output driven to zero (0) when active |            |             |

#### **Parameters**

| NAME        | DEFINITION                 | DATA TYPE | VALUES          |

|-------------|----------------------------|-----------|-----------------|

| WORDS       | number of words            | Integer   | 8-16384         |

| N           | bits per word              | Integer   | 1-144           |

| М           | address size               | Integer   | 3-14            |

| BPC         | bits per column            | Integer   | 2, 4, 8, 16, 32 |

| FLOORPLAN   | auto floorplan             | Integer   | 0, 1            |

| BUFFER_SIZE | buffer size                | String    | 1-6             |

| FREQUENCY   | frequency in MHz           | Integer   | 1-100           |

| VDROP       | voltage drop in millivolts | Integer   | 1-249           |

Block height range is 4-512; block width range is 4-288; max total bits is 144K (16K x 9).

#### **BPC Options**

| BPC VALUE | MINIMUM WORDS | MAXIMUM WORDS | ADDRESS<br>INCREMENT | MINIMUM BITS | MAXIMUM BITS |

|-----------|---------------|---------------|----------------------|--------------|--------------|

| 2         | 8             | 1024          | 4                    | 1            | 144          |

| 4         | 16            | 2048          | 8                    | 1            | 72           |

| 8         | 32            | 4096          | 16                   | 1            | 36           |

| 16        | 64            | 8192          | 32                   | 1            | 18           |

| 32        | 128           | 16384         | 64                   | 1            | 9            |

## **CMOS ASIC Standard Cell Memories**

#### Parts

| PART NAME     | PINS                                |

|---------------|-------------------------------------|

| dpram_1r1w    | DIN, OE, RA, RCE, WA, WCE, WE, DOUT |

| dpram_1r1w_pd | DIN, RA, RPD, WA, WCE, WE, DOUT     |

#### **Truth Tables**

#### zero-out option false

|        |          | INPUTS |     |    | OUTPUTS |                                           |  |

|--------|----------|--------|-----|----|---------|-------------------------------------------|--|

| RA, WA | WCE, RCE | OE     | DIN | WE | DOUT    | COMMENT                                   |  |

| 0/1    | 0        | 0      | Х   | 1  | Data    | Read                                      |  |

| Х      | 0        | 1      | Х   | 1  | Z       | Output Disabled (standard) - RAM Active   |  |

| Х      | 1        | 1      | Х   | Х  | Z       | Output Disabled (standard) - RAM Disabled |  |

| Х      | 1        | 0      | Х   | Х  | Data    | Outputs Stable, RAM Disabled              |  |

| 0/1    | 0        | 0      | 0/1 | 0  | Data    | Write with Write-Through                  |  |

| 0/1    | 0        | 1      | 0/1 | 0  | Z       | Write                                     |  |

#### zero-out option true

|        |     | INPUTS |     |    | OUTPUTS | COMMENT                                  |  |

|--------|-----|--------|-----|----|---------|------------------------------------------|--|

| RA, WA | RPD | DIN    | WCE | WE | DOUT    | COMMENT                                  |  |

| Х      | 1   | Х      | 1   | Х  | 0       | Output Disabled (zero_out), RAM Disabled |  |

| 0/1    | 0   | Х      | 1   | 1  | Data    | Read                                     |  |

| 0/1    | 0   | 0/1    | 0   | 0  | Data    | Write with Write-Through                 |  |

| 0/1    | 1   | 0/1    | 0   | 0  | 0       | Write without Write-Through              |  |

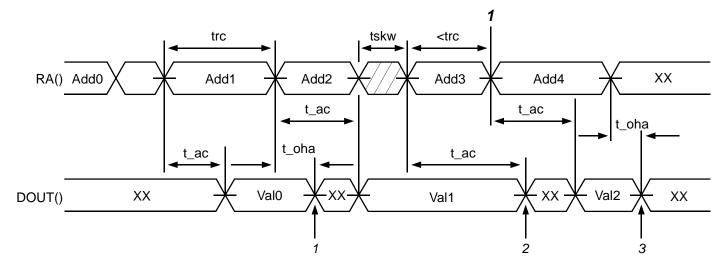

### **CMOS ASIC Standard Cell Memories**

### SWITCHING TIME WAVEFORMS

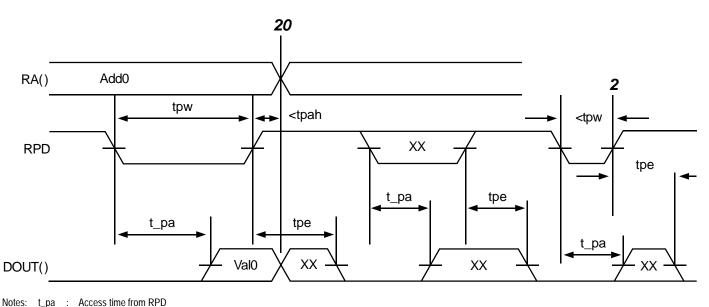

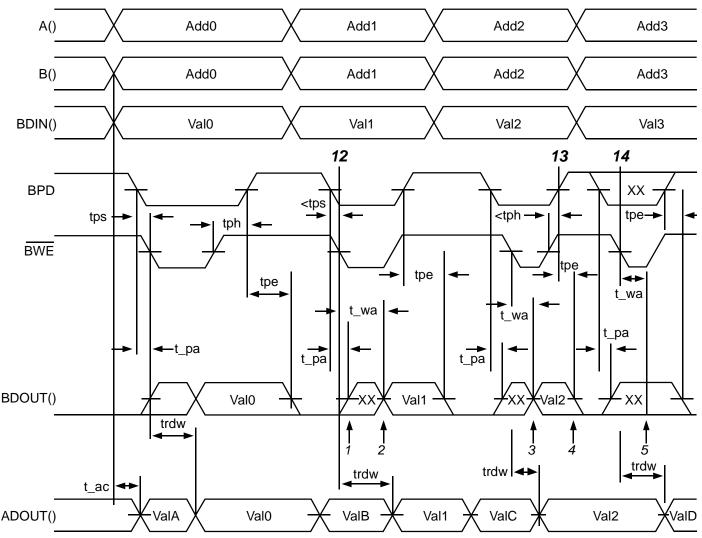

#### Dual Port RAM 1R1W Read Cycle 1

dpram\_1r1w : WE = '1', OE = '0', WCE = '0', RCE = '0' dpram\_1r1w\_pd: WE = '1', WCE = '0', RPD = '0'

- Notes: t\_ac : Address Access Time (maximum of Rise/Fall)

- trc : Read Cycle Time

- t\_oha : Output Hold Time from Address Change (minimum of Rise/Fall)

- tskw : All addresses must complete transition within this time

- 1. t\_oha delay will only be applied to the last data accessed, otherwise, t\_ac will be used for the pin-to-pin delay.

- 2.  $trc = t_ac$ . If Add3 width is less than trc, DOUT() goes to'X'.

- 3. If A() becomes 'X', DOUT() goes 'X' after time t\_oha.

1. Error: Illegal Address input: Address cycle time is smaller than minimum trc.

### **CMOS ASIC Standard Cell Memories**

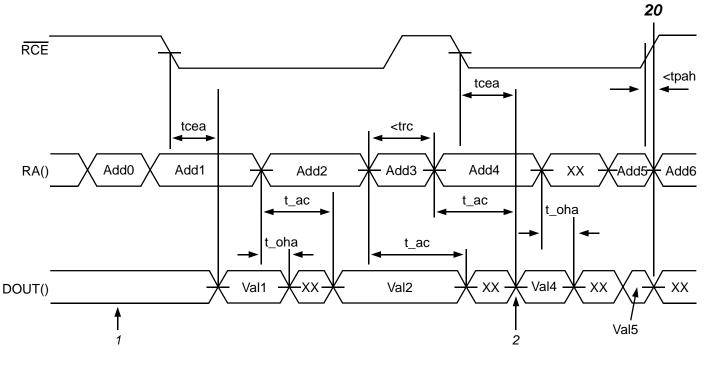

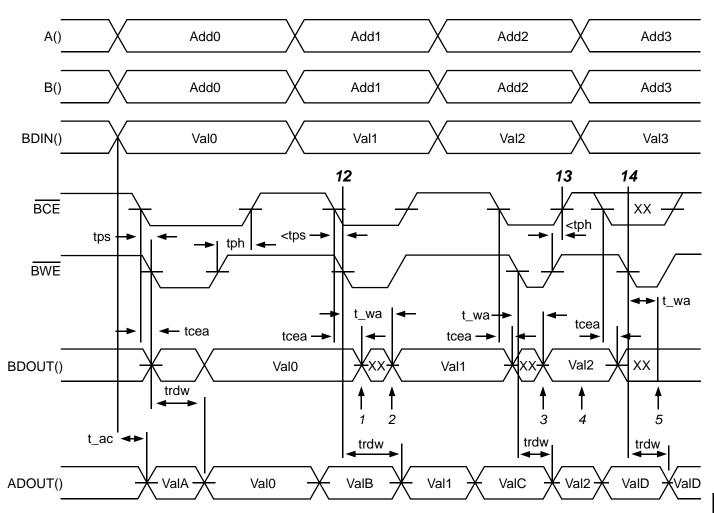

#### Dual Port RAM 1R1W Read Cycle 2

dpram\_1r1w: WE = '1', WCE = '0', RCE = '0'

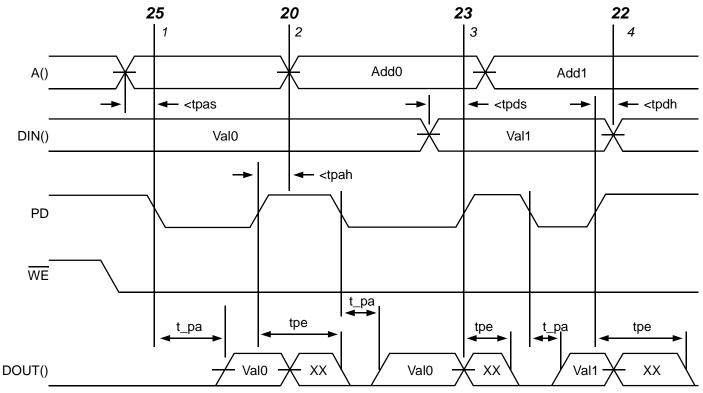

#### Dual Port RAM 1R1W Read Cycle 3

dpram 1r1w pd: WE = '1', WCE = '0'

Memories

t\_pa :

Access time from RPD RPD shutting off to DOUT() Fall tpe :

Minimum pulse width for RPD tpw

Address hold time from RPD rising tpah

2. Error: Illegal RPD input: RPD "Low" width time smaller than Min tpw. 20. Error: Illegal address input: hold time to RPD is smaller than min. tpah.

## **CMOS ASIC Standard Cell Memories**

#### Dual Port RAM 1R1W Read Cycle 4

dpram\_1r1w: WE = '1', WCE = '0', OE = '0'

Notes: t\_ac : Address access time

tcea : RCE access time (maximum of Rise/Fall)

tpah : Address hold time from RCE rising

trc : Read cycle time

t\_oha : Output hold time from address change (minimum of Rise/Fall)

1. Normal DOUT() change due to address change is locked out by  $\overline{RCE p}$  in set to '1'.

2. Output becomes valid after the MAX of t\_ac or tcea. Note that the RCE pin rising does not trigger a RAM access.

20. Error: Illegal address input: hold time to RCE is smaller than min. tpah.

### **CMOS ASIC Standard Cell Memories**

#### Dual Port RAM 1R1W Write Cycle 1

dpram\_1r1w : OE = '0', WCE = '0', RCE = '0' dpram\_1r1w\_pd : WCE = '0', RPD = '0'

- Notes: t\_da : Output delay time from Data (t\_da < t\_ac) (MAX of Rise/Fall)

- trdw : Data access for a write-through operation

- t\_ac : Address access time

- tas : Address setup time

- tah : Address hold time

- tds : Data setup time

- tdh : Data hold time

- tww : White pulse width low

- twc : Write cycle time

ValA, ValB, and ValC are previously retained in address Add0, Add1, and Add2.

- 1. Data retained in Add1 is overwritten by 'X' at this time.

- 2. Data retained in all words is overwritten by 'X' at this time. Writing Val3 into Add3 should be successful.

- 3. Error: Illegal Operation: Data "X" is written at rising edge of  $\overline{WE}$ .

- 4. Error: Illegal Operation: Address was changed while WE low.

## **CMOS ASIC Standard Cell Memories**

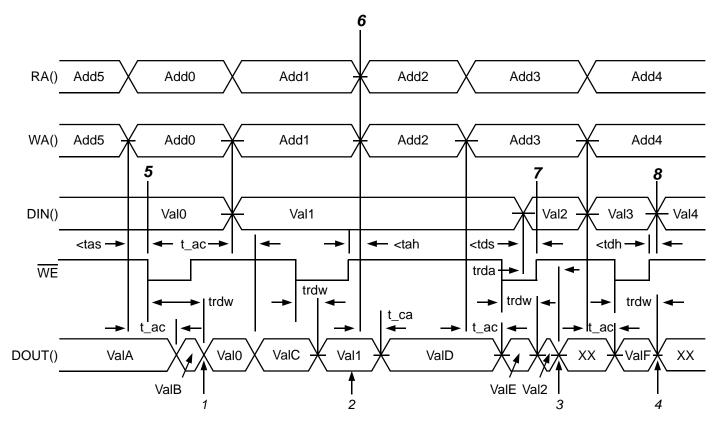

#### Dual Port RAM 1R1W Write Cycle 2

dpram\_1r1w : OE = '0', WCE = '0', RCE = '0' dpram\_1r1w\_pd : WCE = '0', RPD = '0'

Notes: t\_ac : Address access time

- trda : Output delay time from DIN to DOUT (<t\_ac) (MAX of Rise/Fall)

- trdw : Data access for a write-through operation

- tas : Address setup time

- tah : Address hold time

- tds : Data setup time

- tdh : Data hold time

ValA-ValF are previously retained in Add5-Add4.

1. Data retained in all words is overwritten by 'X' at this time. writing Val0 into Add0 should be successful.

- 2. Data retained by all words is overwritten by 'X' at this time.

- 3. Data retained in Add3 is overwritten by 'X' at this time.

4. Data retained in Add4 is overwritten by 'X' at this time.

- 5. Error: Illegal Address Input: Address setup time to WE is smaller than Min tas.

- 6. Error: Illegal Address Input: Address hold time to WE is smaller than Min tah.

- 7. Error: Illegal Data Input: DIN setup time to WE is smaller than Min tds.

8. Error: Illegal Data Input: DIN hold time to WE is smaller than Min tdh.

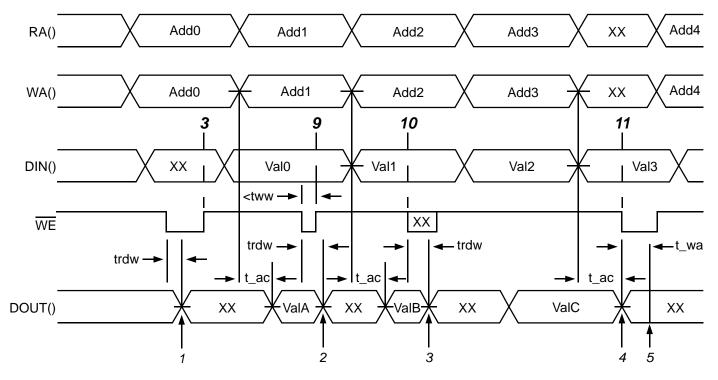

### **CMOS ASIC Standard Cell Memories**

#### Dual Port RAM 1R1W Write Cycle 3

dpram\_1r1w : OE = '0', WCE = '0', RCE = '0' dpram\_1r1w\_pd: WCE = '0', RPD = '0'

Notes:

- trdw : Data access for a write-through operation

- Output delay time from WE (Max of Rise/Fall) t wa

- Address access time t\_ac

- Write pulse width low tww :

- 1. Data retained in Add0 is overwritten by 'X' at this time.

- 2. Data retained in Add1 is overwritten by 'X' at this time.

- 3. Data retained in Add2 is overwritten by 'X' at this time.

- 4. DOUT() becomes 'X' after t\_ac time from leading edge of address 'X'.

- 5. Data retained in all words is overwritten by 'X' after t\_wa time from falling edge of WE.

- Error: Illegal <u>Operation: Data</u> "X" is written at rising edge of WE.

Error: Illegal WE input: WE "Low" width time is smaller than Min tww.

- 10. Error: Illegal Operation: WE input went to "X".

- 11. Error: Illegal Operation: Address was "X" at the falling edge of WE.

## **CMOS ASIC Standard Cell Memories**

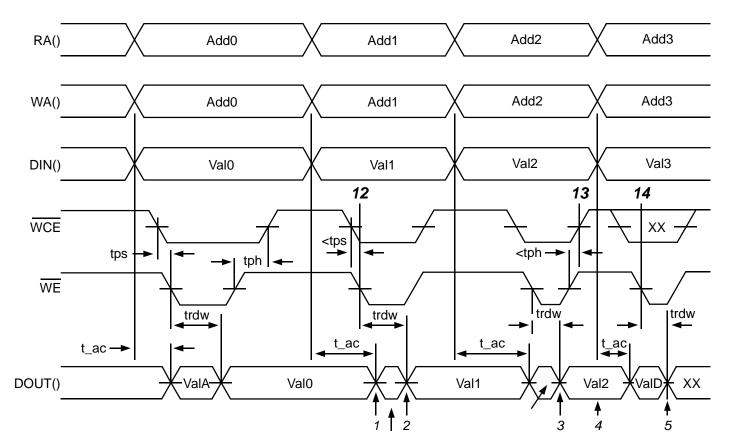

#### Dual Port RAM 1R1W Write Cycle 4, and Write Cycle 5

dpram\_1r1w\_pd : RPD = '0' dpram\_1r1w : RCE = '0', OE = '0'

Notes: tps : WCE/RPD setup time

tph : PD hold time

trdw : Data access for a write-through operation

t\_ac : Address access time

ValA-ValD are previously retained in address Add0-Add3.

1. 4. Data retained in all words is overwritten by 'X' at this time.

2. "X" retained in Add1 is overwritten by Val1 at this time.

3. "X" retained in Add2 is overwritten by Val2 at this time.

5. If Data retained in Add3 is not equal to Val3, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value.

**12**. Error: Illegal RPD Input: RPD setup time to  $\overline{WE}$  is smaller than Min tps.

13. Error: Illegal RPD Input: RPD hold time to WE is smaller than Min tph.

14. Error: Illegal Operation: RPD was "X" at the falling edge of WE.

### **CMOS ASIC Standard Cell Memories**

#### Dual Port RAM 1R1W Write Cycle 6 (dpram\_1r1w\_pd)

- trdw : Data access for a write-through operation

- 1. If Data retained in Add1 is not equal to Val1, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value. 2. If Data retained in Add2 is not equal to Val2, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value.

- 15. Error: Illegal WCE input: WCE "Low" width time smaller than Min tpw.

## **CMOS ASIC Standard Cell Memories**

#### Dual Port RAM 1R1W Write Cycle 7 (dpram\_1r1w)

trdw Data access for a write-through operation

1. If Data retained in Add1 is not equal to Val1, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value. 2. If Data retained in Add2 is not equal to Val2, retained data is overwritten by "X" at this time. If both are identical, retained data is not overwritten by any value.

Error: Illegal WCE input: WCE "Low" width time smaller than Min tpw.

Error: Illegal Operation: WCE went "X" while WE is "Low".

### **CMOS ASIC Standard Cell Memories**

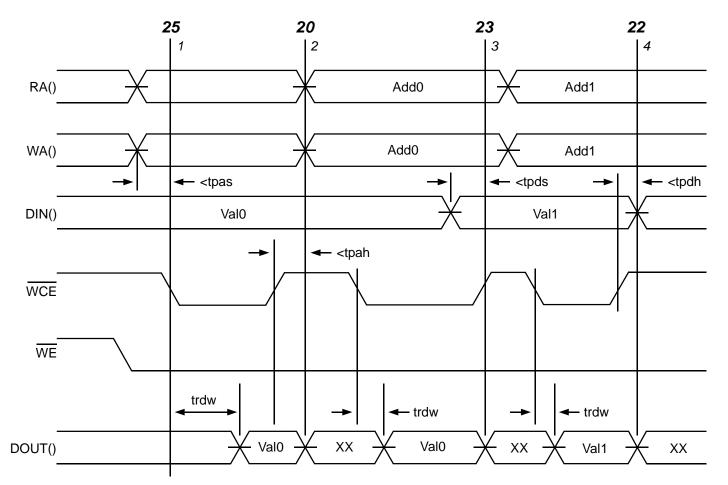

#### Dual Port RAM 1R1W Write Cycle 8, Write Cycle 9

dpram\_1r1w\_pd: RPD = '0' dpram\_1r1w : RCE = '0', OE = '0'

- Notes: tpas : Address setup time to WCE

- tpah : Address hold time to WCE

- tpds : Data setup time to WCE

- tpdh : Data hold time to WCE

- trdw : Data access for a write-through operation

- 1. If tpas is violated, data in all addresses is overwritten by "X" at this time. 2. If tpah is violated, data in all addresses is overwritten by "X" at this time.

- 3. If tpds is violated, data in Add0 is overwritten by "X" at this time.

- 4. If tpdh is violated, data in Add1 is overwritten by "X" at this time.

20. Error: Illegal address input: hold time to WCE is smaller than min. tpah.

22. Error: Illegal data input: DIN hold time to WCE is smaller than min. tpdh.

23. Error: Illegal data input: DIN setup time to WCE is smaller than min. tpds.

25. Error: Illegal address input: setup time to WCE is smaller than min. tpas.

## **CMOS ASIC Standard Cell Memories**

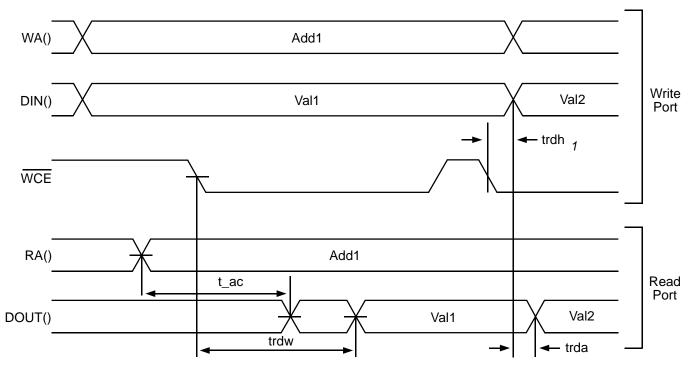

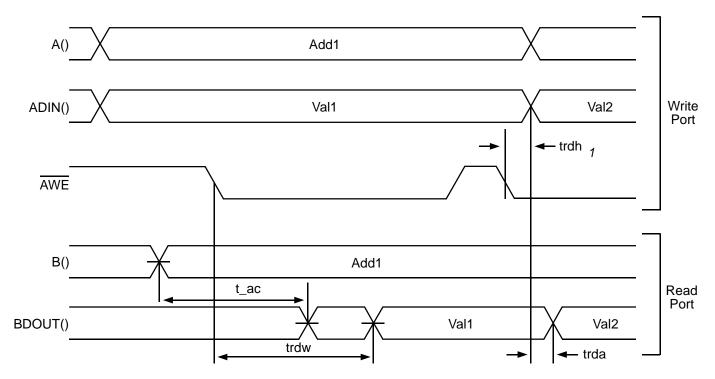

#### Dual Port RAM 1R1W Write Through

dpram\_1r1w : OE = '0', WCE = '0', RCE = '0' dpram\_1r1w\_pd : WCE = '0', RPD = '0'

Notes: t\_ac : Address access time

trdw : Data access for a write-through operation from WE to data out. This time is always longer than t\_wa or t\_ac

trdh : Data hold from WE rising/falling for write-through

trda : Output delay from DIN

1. If DIN change from WE falling edge is greater than trdh, the DIN change will not propagate through to DOUT until the rising edge of WE.

## **CMOS ASIC Standard Cell Memories**

#### Features

- 8-T memory cell design

- Simple combinational logic decoding

- Small bitline differential in read mode eliminates precharge delay

- Fast ATD circuit turns on wordlines and sense amps only as needed to save power while allowing asynchronous operation

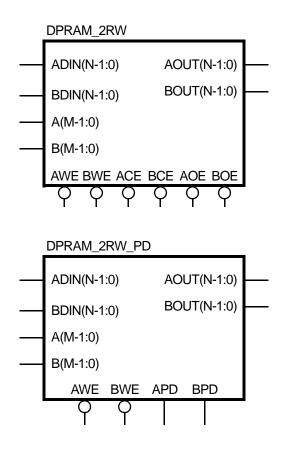

## Logic Symbol

## **CMOS ASIC Standard Cell Memories**

#### DPRAM\_2RW: High Speed Low-Power Dual Port Description

AMI Semiconductor's high speed, low power CMOS RAM is available in both single and dual port versions. Column select passgates provide a cascode gain stage, followed by a differential voltage sense amp. The memory array columns may be multiplexed to optimize the aspect ratio. Multiplexing of columns, or column folding, shortens the bitline length (reduces the number of rows in the array) while increasing the width of the memory array. No change in the total memory bit count occurs.

The zero\_out option sends the outputs all to "zero". This operation is controlled by the PD signal.

The RAM draws current only in response to changing inputs, minimizing power consumption and allowing complete IDDQ testing. Address changes activate the sense amps and one row of memory cells for a period of time longer than access time. The current drawn by each sense amp is comparable to the read current of each memory cell.

## **CMOS ASIC Standard Cell Memories**

### Signal Summary

|            | INPUTS                                                                                            | OUTPUTS      |             |  |