### 93H72

## HIGH SPEED 4-BIT SHIFT REGISTER (With Enable)

**DESCRIPTION** — The '72 high speed 4-bit shift register is a multifunctional sequential logic block which is useful in a wide variety of register applications. It may be used in serial-serial, shift left, shift right, serial-parallel, parallel-serial and parallel-parallel data transfers. The '72 has three synchronous modes of operation: shift, parallel load and hold (do nothing). The hold capability permits information storage in the register independent of the clock.

- 60 MHz TYPICAL SHIFT FREQUENCY

- SYNCHRONOUS PARALLEL DATA ENTRY

- DATA HOLD (DO NOTHING) INDEPENDENT OF CLOCK

- FULLY SYNCHRONOUS, EDGE-TRIGGERED

- ASYNCHRONOUS MASTER RESET

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                              | PKG<br>TYPE |  |

|--------------------|-----|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{C to} + 125^{\circ}\text{C}$ |             |  |

| Plastic<br>DIP (P) | Α   | 93H72PC                                                                                  |                                                                                             | 9B          |  |

| Ceramic<br>DIP (D) | Α   | 93H72DC                                                                                  | 93H72DM                                                                                     | 6B          |  |

| Flatpak<br>(F)     | А   | 93H72FC                                                                                  | 93H72FM                                                                                     | 4L          |  |

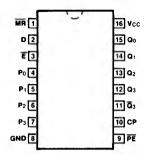

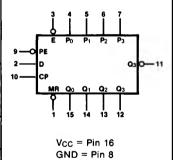

## CONNECTION DIAGRAM PINOUT A

#### LOGIC SYMBOL

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                        | DESCRIPTION                        | <b>93H (U.L.)</b><br>HIGH/LOW |

|----------------------------------|------------------------------------|-------------------------------|

| E                                | Enable Input (Active LOW)          | 2.0/2.0                       |

| PE                               | Parallel Enable Input (Active LOW) | 1.0/1.0                       |

| $P_0 - P_3$                      | Parallel Data Inputs               | 1.0/1.0                       |

| CP                               | Clock Pulse Input                  | 2.0/2.0                       |

| CP<br>MR                         | Master Reset Input (Active LOW)    | 1.0/1.0                       |

| D                                | Serial Data Input                  | 1.0/1.0                       |

| $Q_0 - Q_3$                      | Parallel Outputs                   | 20/10                         |

| $\frac{Q_0-Q_3}{\overline{Q}_3}$ | Last Stage Complementary Output    | 20/10                         |

**FUNCTIONAL DESCRIPTION** — The '72 is a 4-bit shift register with three modes of operation: shift, parallel load and hold (do nothing). The register is fully synchronous with any output change occuring after the rising clock edge. The '72 features edge-triggered type characteristics on all inputs (except  $\overline{\text{MR}}$ ) which means there are no restrictions on the activity of these inputs ( $\overline{\text{PE}}$ ,  $\overline{\text{E}}$ ,  $\overline{\text{PO}}$  — P3, D) for logic operation except for the setup requirements prior to the LOW-to-HIGH clock transition.

The mode of operation of the '72 is determined by the two inputs, Parallel Enable (PE) and Enable (E) as shown in Table 1. The active LOW Enable when HIGH, places the register in the hold mode with the register flip-flops retaining their information. When the Enable is activated (LOW) the Parallel Enable (PE) determines whether the register operates in a shift or parallel data entry mode.

When the Enable is LOW and the Parallel Enable input is LOW the parallel inputs are selected and will determine the next condition of the register synchronously with the clock as shown in Table II. In this mode the element appears as four common clocked D flip-flops. With E LOW and the PE input HIGH the device acts as a 4-bit shift register with serial data entry through the D input shown in Table III. In both cases the next state of the flip-flops occurs after the LOW-to-HIGH transition of the clock input.

The asynchronous active LOW Master Reset overrides all inputs and clears the register forcing outputs  $Q_0 - Q_3$  LOW and  $\overline{Q_3}$  HIGH. To provide for left shift operation,  $P_3$  is used as the serial data input and  $Q_0$  is the serial data output. The other outputs are tied back to the previous parallel inputs, with  $Q_3$  tied to  $P_2$ ,  $Q_2$  tied to  $P_1$  and  $Q_1$  tied to  $P_0$ .

LOGIC DIAGRAM

#

#### TABLE I. MODE SELECT TABLE

| MODE                   |                                       | MR  | Ē   | PE   | Po                                     | P <sub>1</sub>     | P <sub>2</sub> | P3            | D                           |

|------------------------|---------------------------------------|-----|-----|------|----------------------------------------|--------------------|----------------|---------------|-----------------------------|

| Synchronous            | Parallel Load<br>Serial Shift<br>Hold | TIT | ILL | יבד: | X<br>X                                 | allel Da<br>X<br>X | ata En         | try<br>X<br>X | X<br>Serial Data Entry<br>X |

| Asynchronous           | Hold<br>Reset                         | H   | H   | Н    | X<br>All (                             | X<br>Output        | X<br>s Set I   | X             | $\overline{Q}_3 = HIGH$     |

| Asylicilionous   neset |                                       | _   | _ ^ | L ^_ | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | Cuipu              | 3 361          |               | G3 - HIGH                   |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

#### TABLE II. PARALLEL DATA ENTRY SERIAL DATA ENTRY

| P <sub>0</sub> — P <sub>3</sub> | Q                    |

|---------------------------------|----------------------|

| INPUT @ t <sub>n</sub>          | @ t <sub>n</sub> + 1 |

| L                               | L                    |

| H                               | H                    |

## TABLE III.

| D INPUT<br>@ t <sub>n</sub> | Q <sub>0</sub><br>@ t <sub>n + 1</sub> |

|-----------------------------|----------------------------------------|

| L                           | L                                      |

| ) н                         | н                                      |

tn = Present State

tn + 1 = State after next clock H = HIGH Voltage Level

L = LOW Voltage Level

#### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER                    |    | 93  | ВН         | UNITS | CONDITIONS                                    |

|--------|------------------------------|----|-----|------------|-------|-----------------------------------------------|

| 01     |                              |    | Min | Max        | 0     |                                               |

| los    | Output Short Circuit Current |    | -30 | -100       | mA    | V <sub>CC</sub> = Max, V <sub>OUT</sub> = 0 V |

| lcc    | Power Supply Current         | XM |     | 120<br>135 | mA    | Vcc = Max                                     |

#### AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|                  |                               | 9:               | 3H       |       | CONDITIONS      |

|------------------|-------------------------------|------------------|----------|-------|-----------------|

| SYMBOL           | PARAMETER                     | C <sub>L</sub> = | 15 pF    | UNITS |                 |

|                  |                               | Min              | Max      |       |                 |

| f <sub>max</sub> | Maximum Shift Frequency       | 45               |          | MHz   | Figs. 3-1, 3-8  |

| tPLH<br>tPHL     | Propagation Delay<br>CP to Qn |                  | 16<br>21 | ns    | Figs. 3-1, 3-8  |

| tPHL             | Propagation Delay MR to Qn    |                  | 26       | ns    | Figs. 3-1, 3-16 |

#### AC OPERATING REQUIREMENTS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25 ^{\circ} \text{C}$

| SYMBOL                                   | PARAMETER                                           | 9:  | 3H  | UNITS | CONDITIONS   |  |

|------------------------------------------|-----------------------------------------------------|-----|-----|-------|--------------|--|

|                                          | T ANAMETER                                          | Min | Max | ]     | 001121110110 |  |

| ts (H)<br>ts (L)                         | Setup Time HIGH or LOW<br>D or P <sub>n</sub> to CP | 7.0 |     | ns    | Fig. 3-6     |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>E to CP                   | 17  |     |       |              |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW PE to CP                     | 19  |     | ns    | Fig. 3-6     |  |

| th (H)<br>th (L)                         | Hold Time HIGH or LOW<br>D, Pn, E or PE to CP       | 0   |     |       | 119.00       |  |

| t <sub>w</sub> (L)                       | MR Pulse Width LOW                                  | 19  |     | ns    | Fig. 3-16    |  |

| trec                                     | MR Recovery Time                                    | 7.0 |     | ]     | , .g         |  |