93415A-F,N • 93425A-F,N

#### DESCRIPTION

The 93415A and 93425A, with a typical access time of 30ns, are ideal for cache buffer applications and for systems requiring very high speed main memory.

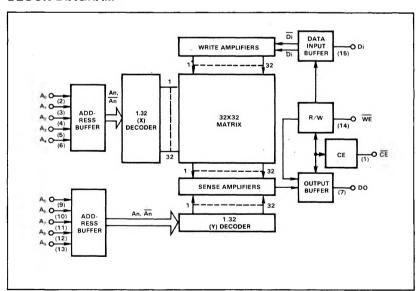

Both the 93415A and 93425A require a single +5V power supply and feature very low current pnp input structures. They include on-chip decoding and a chip enable input for ease of memory expansion, and feature either open collector or tri-state outputs for optimization of word expansion in bused organizations.

Both devices are available in the commercial temperature range (0°C to +75°C).

## **FEATURES**

- Address access time: 45ns max

- Write cycle time: 45ns max

- Power dissipation: 0.5mW/bit typ

- Input loading: -250μA max

- On-chip address decoding

- Output options:

93415A: Open collector

93425A: Tri-state

- Non-inverting output

- Blanked output during Write

- Fully TTL compatible

## **APPLICATIONS**

- High speed main frame

- Cache memory

- Buffer storage

- Writable control store

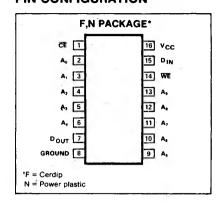

## PIN CONFIGURATION

# TRUTH TABLE

| MODE        | CE   | WE  | D   | DOUT        |             |  |

|-------------|------|-----|-----|-------------|-------------|--|

| MODE        | CE   | ₩ E | DIN | 93415A      | 93425A      |  |

| Read        | 0    | 1   | х   | Stored data | Stored data |  |

| Write low   | 0    | 0   | 0   | 1           | High-Z      |  |

| ∘Write high | 0    | 0   | 1   | 1           | High-Z      |  |

| Disabled    | * 1. | X   | x   | 1           | High-Z      |  |

X = Don't care

## **BLOCK DIAGRAM**

93415A-F,N • 93425A-F,N

# **ABSOLUTE MAXIMUM RATINGS**

|      | PARAMETER1         | RATING      | UNIT |

|------|--------------------|-------------|------|

| Vcc  | Supply voltage     | +7          | Vdc  |

| VIN  | Input voltage      | +5.5        | Vdc  |

|      | Output voltage     |             | Vdc  |

| Vон  | High (93415A)      | +5.5        | 1    |

| Vo   | Off-state (93425A) | +5.5        | i    |

|      | Temperature range  |             | l ∘c |

| TA   | Operating          | 0 to +75    |      |

| TSTG | Storage            | -65 to +150 |      |

# DC ELECTRICAL CHARACTERISTICS $0^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +75 $^{\circ}$ C, 4.75V $\leq$ V<sub>CC</sub> $\leq$ 5.25V

|                                                       |                                                                                       |                                                                                                                                  | 1   | LIMITS           |                         |                |

|-------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-------------------------|----------------|

|                                                       | PARAMETER                                                                             | TEST CONDITIONS                                                                                                                  | Min | Typ <sup>2</sup> | Max                     | UNIT           |

| V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>IC</sub> | Input voltage<br>Low¹<br>High¹<br>Clamp¹.3                                            | V <sub>CC</sub> = Min<br>V <sub>CC</sub> = Max<br>V <sub>CC</sub> = Min, I <sub>IN</sub> = -12mA                                 | 2.1 | -1.0             | .85<br>-1.5             | V              |

| V <sub>OL</sub><br>Voн                                | Output voltage<br>Low1.4<br>High (93425A)1.5                                          | $V_{CC} = Min$ $I_{OL} = 16mA$ $I_{OH} = -2mA$                                                                                   | 2.4 | 0.35             | 0.45                    | V              |

| liL<br>liH                                            | Input current<br>Low<br>High                                                          | V <sub>IN</sub> = 0.45V<br>V <sub>IN</sub> = 5.5V                                                                                |     | -10<br>1         | -250<br>25              | μΑ             |

| lolk<br>lo(OFF)                                       | Output current<br>Leakage (93415A)6<br>Hi-Z state (93425A)<br>Short circuit (93425A)7 | V <sub>CC</sub> = Max<br>V <sub>OUT</sub> = 5.5V<br>V <sub>OUT</sub> = 5.5V<br>V <sub>OUT</sub> = 0.456<br>V <sub>OUT</sub> = 0V | -20 | 1<br>1<br>-1     | 40<br>60<br>-60<br>-100 | μΑ<br>μΑ<br>mA |

| Icc                                                   | Vcc supply current8                                                                   | $V_{CC} = Max$ $0 < T_A < 25^{\circ}C$ $T_A \ge 25^{\circ}C$ $T_A \le 0^{\circ}C$                                                |     | 120<br>95        | 155<br>130<br>170       | mA             |

| Cin<br>Cout                                           | Capacitance<br>Input<br>Output                                                        | $V_{CC} = 5.0V$ $V_{IN} = 2.0V$ $V_{OUT} = 2.0V$                                                                                 |     | 4 7              |                         | pF             |

93415A-F,N • 93425A-F,N

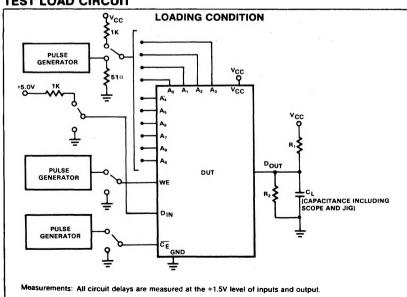

# AC ELECTRICAL CHARACTERISTICS 9 $R_1 = 270\Omega$ , $R_2 = 600\Omega$ , $C_L = 30 pF$ , $0^{\circ}C \le T_A \le +75^{\circ}C$ , $4.75 V \le V_{CC} \le 5.25 V_{CC} \le 1.25 V$

| PARAMETER  Access time TAA Address |                          | 70            | FROM         | LIMITS |                  |     |      |

|------------------------------------|--------------------------|---------------|--------------|--------|------------------|-----|------|

|                                    |                          | то            | FROM         | Min    | Typ <sup>2</sup> | Max | UNIT |

|                                    |                          |               |              |        | 30               | 45  | ns   |

| TAA<br>TCE                         | Chip enable              |               |              |        | 15               | 30  |      |

| <del></del>                        | Disable time             |               |              |        |                  |     | ns   |

| TCD                                |                          | Output        | Chip enable  |        | 15               | 30  |      |

| $T_{WD}$                           |                          | Output        | Write enable |        | 20               | 30  |      |

| Twn                                | Write recovery time      |               |              |        | 20               | 30  | ns   |

|                                    | Setup and hold time      |               |              |        |                  |     | ns   |

| Twsa                               | Setup time               | 14/=:40 0=010 | A 44         | _      | ١ ,              | i i |      |

| TWHA                               | Hold time                | Write enable  | Address      | 5      | 0                |     |      |

| Twsp                               | Setup time <sup>10</sup> | Write enable  | Data in      | 40     | 35               |     |      |

| TwhD                               | Hold time                | write enable  |              | 5      | 0                |     |      |

| Twsc                               | Setup time               | Write enable  | CE           | 5      | 0                |     |      |

| Twhc                               | Hold time                | Will Chaple   |              |        | <u> </u>         |     |      |

|                                    | Pulse width              |               |              |        |                  |     | ns   |

| Twp                                | Write enable11           | 1             |              | 35     | 25               | l I |      |

#### NOTES

- 1. All voltage values are with respect to network ground terminal.

- 2. All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

- 3. Test each input one at a time.

- 4. Measured with a logic low stored. Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 5. Measured with VIL applied to CE and a logic high stored.

- 6. Measured with VIH applied to CE.

- 7. Duration of the short circuit should not exceed 1 second.

- 8. ICC is measured with the write enable and memory enable inputs grounded, all other inputs at 4.5V, and the output open.

- 9. The operating ambient temperature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a 2-minute warm-up. Typical thermal resistance values of the package at maximum temperature are:

- θ<sub>JA</sub> junction to ambient at 400fpm air flow-50° C/watt

- θ JA junction to ambient-still air-90° C/watt

- θ JA junction to case-20° C/watt 10. For minimum Write pulse width.

- 11. Minimum required to guarantee a Write into the slowest bit.

## **TEST LOAD CIRCUIT**

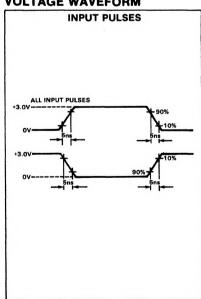

## **VOLTAGE WAVEFORM**

93415A-F.N • 93425A-F.N

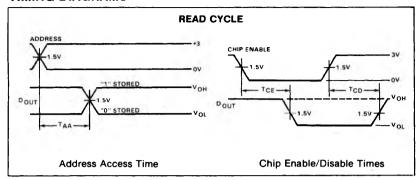

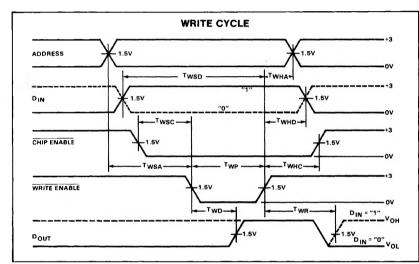

## **TIMING DIAGRAMS**

### **MEMORY TIMING DEFINITIONS**

- Twn Delay between end of Write Enable pulse and when Data Output becomes valid. (Assuming Address still valid—not as shown.)

- TCE Delay between beginning of Chip Enable low (with Address valid) and when Data Output becomes valid.

- T<sub>CD</sub> Delay between when Chip Enable becomes high and Data Output is in off state.

- TAA Delay between beginning of valid Address (with Chip Enable low) and when Data Output becomes

- Twsc Required delay between beginning of valid Chip Enable and beginning of Write Enable pulse.

- T<sub>WHD</sub> Required delay between end of Write Enable pulse and end of

- Write Enable pulse and end o valid Input Data.

- Twp Width of Write Enable pulse.

Twsa Required delay between begin-

- Twsa Required delay between beginning of valid Address and beginning of Write Enable pulse.

- Twsb Required delay between beginning of valid Data Input and end of Write Enable pulse.

- TwD Delay between beginning of Write Enable pulse and when Data Output is in off state.

- TWHC Required delay between end of Write Enable pulse and end of Chip Enable.

- TWHA Required delay between end of Write Enable pulse and end of valid Address.