# 54H/74H108

# **DUAL JK EDGE-TRIGGERED FLIP-FLOP**

(With Separate Sets, A Common Clear and Clock)

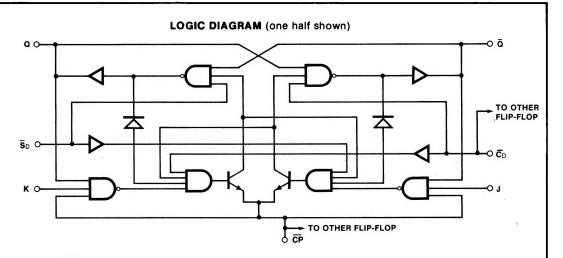

**DESCRIPTION** — The '108 is a high speed JK negative edge-triggered flipflop. It features individual J, K, and asynchronous Set inputs to each flip-flop as well as common clock and asynchronous Clear inputs. When the clock goes HIGH, the inputs are enabled and data will be accepted. The logic state of J and K inputs may be allowed to change when the clock pulse is in a HIGH state and the bistable will perform according to the Truth Table as long as minimum setup times are observed. Input data is transferred to the outputs on the falling edge of the clock pulse.

#### **TRUTH TABLE**

| INPUTS           |   | OUTPUT           |  |  |

|------------------|---|------------------|--|--|

| @ t <sub>n</sub> |   | @ tn + 1         |  |  |

| J                | К | Q                |  |  |

| L                | L | Qn               |  |  |

| H                | H | H                |  |  |

| Н                | Н | $\overline{Q}_n$ |  |  |

### **Asynchronous Inputs:**

LOW input to  $\overline{S}_D$  sets Q to HIGH level LOW input to  $\overline{C}_D$  sets Q to LOW level Clear and Set are independent of clock Simultaneous LOW on  $\overline{C}_D$  and  $\overline{S}_D$  makes both Q and  $\overline{Q}$  HIGH

$t_{n}=$  Bit time before clock pulse.  $t_{n+1}=$  Bit time after clock pulse. H= HIGH Voltage Level

L = LOW Voltage Level

#### **ORDERING CODE: See Section 9**

|                    | PIN | COMMERCIAL GRADE                                                                             | MILITARY GRADE                                                                                        | PKG<br>TYPE |  |

|--------------------|-----|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ} \text{ C to } +70^{\circ} \text{ C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C} \text{ to } +125^{\circ}\text{ C}$ |             |  |

| Plastic<br>DIP (P) | Α   | 74H108PC                                                                                     |                                                                                                       | 9A          |  |

| Ceramic<br>DIP (D) | А   | 74H108DC                                                                                     | 54H108DM                                                                                              | 6A          |  |

| Flatpak<br>(F)     | Α   | 74H108FC                                                                                     | 54H108FM                                                                                              | 31          |  |

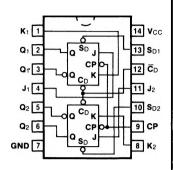

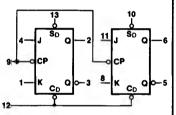

# CONNECTION DIAGRAM PINOUT A

#### LOGIC SYMBOL

V<sub>CC</sub> = Pin 14 GND = Pin 7

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                                                                                                     | DESCRIPTION                             | <b>54/74H (U.L.)</b><br>HIGH/LOW |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------|

| J <sub>1</sub> , J <sub>2</sub> , K <sub>1</sub> ,K <sub>2</sub>                                                              | Data Inputs                             | 1.25/1.25                        |

| CP                                                                                                                            | Clock Pulse Input (Active Falling Edge) | 0*/6.0                           |

| $\bar{C}_{D}$                                                                                                                 | Direct Clear Input (Active LOW)         | 5.0/2.5                          |

| $\begin{array}{c} J_{1},\ J_{2},\ K_{1},K_{2}\\ \hline CP\\ \hline C_{D}\\ \overline S_{D1},\ \overline S_{D2}\\ \end{array}$ | Direct Set Inputs (Active LOW)          | 2.5/1.25                         |

| $Q_1, Q_2, \overline{Q}_1, \overline{Q}_2$                                                                                    | Outputs                                 | 12.5/12.5                        |

\*CP Sourcing Current, see DC Characteristics Table

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER                | 54/74H |      | UNITS   | CONDITIONS                                     |

|--------|--------------------------|--------|------|---------|------------------------------------------------|

|        |                          | Min    | Max  | 0.4.7.5 | J CONDITIONS                                   |

| Ін     | Input HIGH Current at CP | 0      | -1.0 | mA      | V <sub>CC</sub> = Max, V <sub>CP</sub> = 2.4 V |

| Icc    | Power Supply Current     |        | 76   | mA      | V <sub>CC</sub> = Max, V <sub>CP</sub> = 0 V   |

# AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|              |                                                                                        | 54/74H  C <sub>L</sub> = 25 pF  R <sub>L</sub> = 280 Ω |          | UNITS | CONDITIONS                                   |

|--------------|----------------------------------------------------------------------------------------|--------------------------------------------------------|----------|-------|----------------------------------------------|

| SYMBOL       | PARAMETER                                                                              |                                                        |          |       |                                              |

|              |                                                                                        | Min                                                    | Max      | 1     |                                              |

| fmax         | Maximum Clock Frequency                                                                | 40                                                     |          | MHz   | Figs. 3-1, 3-9                               |

| tPLH<br>tPHL | Propagation Delay<br>CP to Q <sub>n</sub> or Q̄ <sub>n</sub>                           |                                                        | 15<br>20 | ns    | Figs. 3-1, 3-9                               |

| tPLH<br>tPHL | Propagation Delay CD or SDn to Qn or Qn                                                |                                                        | 12<br>20 | ns    | V <sub>CP</sub> = ≥ 2.0 V<br>Figs. 3-1, 3-10 |

| tpLH<br>tpHL | Propagation Delay $\overline{C}_D$ or $\overline{S}_{Dn}$ to $Q_n$ or $\overline{Q}_n$ |                                                        | 12<br>35 | ns    | V <sub>CP</sub> = ≤ 0.8 V<br>Figs. 3-1, 3-10 |

# AC OPERATING REQUIREMENTS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$

| SYMBOL                                                         | PARAMETER                                     | 54/74H   |     | UNITS | CONDITIONS   |

|----------------------------------------------------------------|-----------------------------------------------|----------|-----|-------|--------------|

|                                                                |                                               | Min      | Max |       | CONSTITUTION |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L)                       | Setup Time<br>Jn or Kn to CP                  | 10<br>13 |     | ns    | Fig. 3-7     |

| t <sub>s</sub> (L)<br>t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time<br>Jn or Kn to CP                   | 0        |     | ns    | 119.01       |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L)                       | CP Pulse Width                                | 10<br>15 |     | ns    | Fig. 3-9     |

| tw (L)                                                         | $\bar{C}_D$ or $\bar{S}_{Dn}$ Pulse Width LOW | 16       |     | ns    | Fig. 3-10    |